国際特許分類[H01L21/283]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/283]の下位に属する分類

気体または蒸気からの析出,例.凝結 (1,528)

液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/283]に分類される特許

111 - 120 / 487

半導体装置及びその製造方法

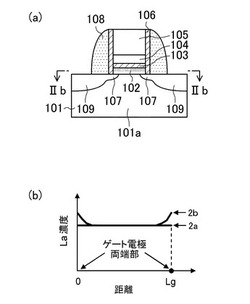

【課題】高誘電率ゲート絶縁膜、及び、ゲート電極としてメタル膜を含む半導体装置において、逆短チャネル効果の発生を防止して高性能化を実現する。

【課題手段】半導体装置は、半導体基板101の上に形成されたランタンを含有する高誘電率ゲート絶縁膜102と、高誘電率ゲート絶縁膜102の上に形成されたキャップ膜103と、キャップ膜103の上に形成されたメタル膜104と、メタル膜104の上に形成されたポリシリコン膜105と、高誘電率ゲート絶縁膜102、キャップ膜103、メタル膜104、及びポリシリコン膜105それぞれの両側面に形成されたランタンを含有するゲート側壁絶縁膜106とを備えている。

(もっと読む)

酸化膜形成方法

【課題】膜中欠損を生じさせることなくGe基板の表面にGe酸化膜を形成する。

【解決手段】Ge基板2の表面にGe酸化膜を形成するプロセスシステム1の酸化炉13において、1000Pa以下の圧力及び300℃以下の基板温度のもとでGe基板2にオゾン供給装置11からオゾンガスを供して当該基板の表面にGe酸化膜を形成する。室温よりも低温の基板温度のもとで前記基板に前記オゾンガスを供給してGe基板2上にオゾン分子層を形成させる。次いで、前記オゾンガスの供給を遮断させた後、Ge基板2を室温まで加熱することにより前記オゾン分子層によって当該基板の表面を酸化させてGe酸化膜を形成させる。Ge基板2が室温まで達した後に前記加熱を遮断して当該基板の温度を室温よりも低温に降下させるとよい。Ge基板2を加熱するための加熱源として赤外光光源を用いるとよい。前記オゾンガスはオゾン濃度が100%であるとよい。

(もっと読む)

高耐圧半導体素子の製造方法及びその構造

【課題】高耐圧半導体素子の層間絶縁膜とその上層に形成される金属膜との密着性を向上させた高耐圧半導体素子の製造方法及びその構造を提供する。

【解決手段】半導体基板1の表面にMOS部2を形成し、このMOS部2を有する前記半導体基板上に層間絶縁膜3を形成し、前記層間絶縁膜上にシリコン膜4を形成し、所定温度の酸化雰囲気内で、成膜した前記シリコン膜4を酸化させて酸化シリコン膜5を形成し、前記酸化シリコン膜5及び前記層間絶縁膜3を貫通する開口を形成し、前記酸化シリコン膜上と前記開口内に金属膜6を被着させ、かつ該金属膜6の上層に電極膜7を形成する、各工程を有する。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

ヘテロ接合電界効果型トランジスタ及びその製造方法

【課題】ゲートリーク電流を抑制する、窒化物半導体からなるリセスゲート構造のヘテロ接合FET及びその製造方法を提供することを目的とする。

【解決手段】本発明のヘテロ接合電界効果トランジスタは、窒化物半導体からなるヘテロ接合電界効果トランジスタであって、バリア層4とバリア層4の上に形成されたキャップ層5を含む半導体層と、半導体層に下部を埋没するようにして半導体層上に設けられたゲート電極9と、ゲート電極9の側面と半導体層の間に設けられた絶縁膜10と、を備え、ゲート電極9は、下面のみが半導体層と接触することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】塗布法や堆積法を用いて高品質な絶縁部材を半導体素子周辺に形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100の製造方法は、半導体基板2上に、Si系絶縁材料からなる絶縁膜10を付加的に形成する工程と、絶縁膜10上に触媒金属膜11を形成する工程と、触媒金属膜11を触媒として用いて絶縁膜10に酸化処理を施す工程と、酸化処理を施した絶縁膜10を加工してゲート絶縁膜4を形成する工程と、ゲート絶縁膜4を含むMOSFET1を形成する工程と、を含む。

(もっと読む)

ボラジン骨格を含むパッシベーション膜、それを使った表示装置

【課題】耐湿性に優れ、信頼性に優れた低誘電率膜を用いて、高性能なパッシベーション膜を備えた表示装置を提供する。このようなパッシベーション膜を用いることにより、表示装置の薄膜化、軽量化、製造コスト削減が可能となる。

【解決手段】ボラジン骨格を有する重合体を含むことを特徴とする表示装置用パッシベーション膜とする、もしくはボラジン骨格を有する化合物及び/または重合体から得られる表示装置用パッシベーション膜を用いる。

(もっと読む)

PMOSデバイスのゲートスタックのしきい値電圧を調整する方法

【課題】本発明は、半導体基板上にゲート誘電体層とゲート電極とのゲートスタックを含む半導体デバイスを製造する方法であって、ゲートスタックのVT値を容易に調整することができる方法を提供する。

【解決手段】ゲート誘電体層とゲート電極とのゲートスタックを含む半導体デバイスを製造する方法は、第1の電気陰性度を有する金属酸化物または半金属酸化物であるゲート誘電体層を半導体基板上に形成するステップと、第2の電気陰性度を有する金属酸化物または半金属酸化物である誘電体VT調整層を形成するステップと、ゲート誘電体層およびVT調整層の上にゲート電極を形成するステップと、を含み、前記ゲートスタックの実効仕事関数が、誘電体VT調整層の厚さおよび組成を調整することによって所望の値に調整され、第2の電気陰性度が、第1の電気陰性度およびAl2O3のいずれよりも高い。

(もっと読む)

半導体装置及びその製造方法

【課題】デュアルメタルゲートプロセスを用いることなく、p型MISトランジスタ及びn型MISトランジスタ双方の特性を向上した半導体装置を実現できるようにする。

【解決手段】半導体装置は、p型半導体領域10Aの上に順次形成された第1の界面シリコン酸化膜105、アルミニウムを含む第1のゲート絶縁膜106A及び第1のゲート電極119Aと、n型半導体領域10Bの上に順次形成された第2の界面シリコン酸化膜105、実効仕事関数を低下させる効果を有する元素を含む第2のゲート絶縁膜106B及び第2のゲート電極119Aとを備えている。第1のゲート絶縁膜106Aの上部におけるアルミニウムの濃度は、1×1020/cm3以上である。第2のゲート絶縁膜106Bの上部におけるアルミニウムの濃度は、1×1019/cm3以下である。第1の界面シリコン酸化膜105の膜厚と第2の界面シリコン酸化膜105の膜厚との差は0.2nm以下である。

(もっと読む)

絶縁膜の形成方法

【課題】絶縁膜としての性能を損なうことなく、スピンオングラスを用いた簡便な方法でメタル下絶縁膜や素子分離用絶縁膜として利用可能な絶縁膜を形成する方法を提供する。

【解決手段】第一の工程としてオルガノアルコキシシランの加水分解縮合物を含む塗布液を基板上に塗布して塗布基板を得る工程と、第二の工程として前記塗布基板を700℃以上900℃以下の温度で水素を含む気体中で加熱して前記塗布膜を焼成して絶縁膜を形成する焼成工程とを順に含む。

(もっと読む)

111 - 120 / 487

[ Back to top ]