国際特許分類[H01L21/283]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/283]の下位に属する分類

気体または蒸気からの析出,例.凝結 (1,528)

液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/283]に分類される特許

131 - 140 / 487

半導体装置およびその製造方法

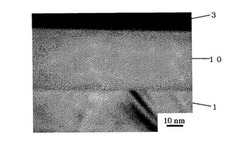

【課題】シリコン表面に厚さがサブナノから数ナノメートル(nm)レベルの極薄の絶縁膜を形成し、これを利用して、低電圧動作MOSデバイスを実現する。

【解決手段】ガラス基板上の多結晶シリコン(薄膜)に対して、その上に室温硝酸酸化法により1.8nmのSiO2膜1を形成し、さらに、その上にプラズマCVD法により40nmのSiO2膜2を堆積して積層にし、これをゲート絶縁膜10として、p−チャンネルMOSトランジスタ(TFT)を創製した。このTFTは、駆動電圧を3Vに低減しても十分に動作可能であり、消費電力を顕著に低減することできる。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造としてメタル電極/High−k膜構造を用いた半導体装置において、仕事関数の制御とEOTの薄膜化とを両立させる。

【解決手段】半導体基板101におけるnチャネルMISトランジスタ形成領域の上に、ゲート絶縁膜として、第1の高誘電率絶縁層202、アルミニウム含有層203、ランタン含有層204及び第2の高誘電率絶縁層205を順次形成する。その後、ゲート電極形成を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】EOTを小さく保ちつつ、より高い実効仕事関数を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101のn型活性領域103の上に形成された第1のゲート絶縁膜107と、第1のゲート絶縁膜107の上に形成された第1のゲート電極111とを有している。第1のゲート絶縁膜107は、ハフニウム及びアルミニウムを含み、且つ中央部において上部及び下部よりもアルミニウムの濃度が高い。第1のゲート電極111はチタンを含む。

(もっと読む)

窒化物半導体発光素子

【課題】光取り出し効率が高く、かつ発光効率が高い窒化物半導体発光素子を提供する。

【解決手段】本発明の窒化物半導体発光素子は、窒化物半導体層と、導電性の第1酸化物層と、絶縁性の第2酸化物層とを含み、第1酸化物層および第2酸化物層は、同一種類の酸化物材料からなることを特徴とする。第1酸化物層を構成する二酸化チタン中のチタンに対し、ニオブ、タンタル、モリブデン、ヒ素、アンチモン、アルミニウムまたはタングステンのいずれかがモル比で1%以上10%以下ドープされ、第2酸化物層を構成する二酸化チタン中のチタンに対し、ニオブ、タンタル、モリブデン、ヒ素、アンチモン、アルミニウムまたはタングステンのいずれかがモル比で1%未満ドープされることが好ましい。

(もっと読む)

積層体、その製造方法、積層体を備える薄膜トランジスタ、および積層体を備えるプリント配線基板

【課題】基板とめっき層との密着性に優れた積層体、その製造方法、積層体を備える薄膜トランジスタ、積層体を備えるプリント配線基板を提供する。

【解決手段】

積層体1では、基板2上にシリカ層3および有機層4を介し、めっき層5が形成されている。シリカ層3はポリシラザンを前駆体として形成されているので、基板2との密着性が良好で、上面に無数の微細な凹凸が存在するシリカ層3が形成される。有機層4は、シリカ層3の上面の凹凸によって発現するアンカー効果により、シリカ層3と強固に結合する。また、有機層4の上面には、シリカ層3の上面の無数の微細な凹凸を反映して凹凸が形成されるので、めっき層5と有機層4とは、化学的もしくは電気的な結合に加え、アンカー効果により強固に結合される。よって、シリカ層3および有機層4を介して基板2上に形成されるめっき層5の基板2に対する密着性を向上できる。

(もっと読む)

半導体装置の製造方法。

【課題】 金属膜やHigh−k膜の膜質の劣化を抑制できる半導体装置の製造方法を提供すること。

【解決手段】 第1の薄膜2上に、第1の薄膜2とは異なる第2の薄膜3を形成し、第2の薄膜3上に、第2の薄膜3とは異なる膜からなる犠牲膜5を形成し、犠牲膜5をエッチングにより所望の間隔を持つパターンに加工し、犠牲膜パターンを形成し、シリコン含有プリカーサー、酸素含有ガスを基板上に間欠的に供給して、犠牲膜パターンにシリコン酸化膜6を被覆し、シリコン酸化膜6をエッチングにより犠牲膜5の側壁上に側壁スペーサー6aを形成し、犠牲膜5を除去し、側壁スペーサー6aをマスクとして用いて第1の薄膜2および第2の薄膜3を加工する。

(もっと読む)

半導体装置の作製方法

【課題】 信頼性の高いTFT構造を用いた半導体装置を実現する。

【解決手段】 TFTに利用する絶縁膜、例えばゲート絶縁膜、保護膜、下地膜、層間絶縁膜等として、ボロンを含む窒化酸化珪素膜(SiNX BY OZ )をスパッタ法で形成する。その結果、この膜の内部応力は、代表的には−5×1010dyn/cm2 〜5×1010dyn/cm2 、好ましくは−1010dyn/cm2 〜1010dyn/cm2 となり、高い熱伝導性を有するため、TFTのオン動作時に発生する熱による劣化を防ぐことが可能となった。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、高誘電率膜を用いた相補型トランジスタの実効仕事関数を調整して適切なしきい値電圧を実現する際に、エッチング工程数を低減するとともに、エッチングダメージの発生を回避する。

【解決手段】 nチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第1のゲート絶縁膜と第1金属ゲート電極との間にアルミニウム膜を設けるとともに、pチャネル絶縁ゲートトランジスタのSiO2より誘電率の高い第2ゲート絶縁膜と第2金属ゲート電極との間に酸化アルミニウム膜を設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】仕事関数を十分に制御することができ、閾値電圧の変動を抑制した半導体装置および半導体装置の製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10に第1導電型チャネルMOSFETを備える。第1導電型チャネルMOSFETは、例えばPチャネルMOSFETであって、半導体基板10の上に設けられたゲート絶縁膜21と、ゲート電極65とからなる。ゲート電極65は、ゲート絶縁膜21の上に設けられた金属ゲート電極20と、金属ゲート電極20の上に設けられた金属酸化膜24と、金属酸化膜24の上に設けられた金属ゲート電極26と、を含んでいる。

(もっと読む)

素子内蔵型配線フィルム

【課題】塗装プロセスを用いた印刷技術により必要な配線やトランジスタ等の素子を形成するにあたり、前記配線の精度を容易に確保することができると共に配線形成に要する時間を短縮することができ、そして、これにより必要な配線やトランジスタ等の素子を実装・搭載した半導体デバイスのトータルのタットタイムを短縮することができる有利な構造の素子内蔵型配線フィルムを提供すること。

【解決手段】長尺の絶縁テープ1もしくは絶縁シート上に微細な配線パターン2を形成した配線フィルム3上に、配線パターン2を構成する配線4の一部を取り込んでトランジスタ、キャパシタ、抵抗等の素子を構成する材料を含有するインクを用いた塗装プロセスを施すことにより、前記素子を直接且つ一体に形成した、素子内蔵型配線フィルム。

(もっと読む)

131 - 140 / 487

[ Back to top ]