国際特許分類[H01L21/283]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体装置または固体装置またはそれらの部品の製造または処理に特に適用される方法または装置 (183,847) | 半導体装置またはその部品の製造または処理 (125,986) | 少なくとも一つの電位障壁または表面障壁,例.PN接合,空乏層,キャリア集中層,を有する装置 (97,574) | 不純物,例.ドーピング材料,を含むまたは含まない周期律表第IV族の元素またはA↓I↓I↓IB↓V化合物から成る半導体本体を有する装置 (83,040) | 21/20〜21/268に分類されない方法または装置を用いる半導体本体上への電極の製造 (9,571) | 電極用の導電または絶縁材料の析出 (3,372)

国際特許分類[H01L21/283]の下位に属する分類

気体または蒸気からの析出,例.凝結 (1,528)

液体からの析出,例.電解液からの析出 (1,357)

国際特許分類[H01L21/283]に分類される特許

121 - 130 / 487

自己整列グラフェン・トランジスタ

【課題】自己整列グラフェン・トランジスタを作製するスキームを提供する。

【解決手段】グラフェン電界効果トランジスタは、ゲート・スタックであってシード層とシード層の上に形成されたゲート酸化物とゲート酸化物の上に形成されたゲート金属とを含む該ゲート・スタック、絶縁層、およびシード層と絶縁層との間に転写されたグラフェン・シート、を含む。

(もっと読む)

金属の付着

システム及び方法が、電圧切り換え可能な誘電体材料に1つ以上の材料を付着させることを含む。特定の態様では、電圧切り換え可能な誘電体材料が、導電バックプレーン上に配置される。いくつかの実施形態では、電圧切り換え可能な誘電体材料が、付着に関する特性電圧が相違する複数の領域を含む。いくつかの実施形態は、マスキングを含み、取り除くことが可能なコンタクトマスクの使用を含むことができる。特定の実施形態は、電気グラフトを含む。いくつかの実施形態は、2つの層の間に配置される中間層を含む。 (もっと読む)

耐酸化性酸化ホウ素層を含む電極およびその製造方法

ここで開示されているのは、銅、ニッケル、鉄、コバルト、チタン、鉛、アルミニウム、スズおよびこれらの金属の1つを主成分として含む合金からなる群から選択される導電性構成成分を含む導電層と、酸化ホウ素を含む酸化保護層とを含む電極であって、前記酸化保護層が導電層の上面を被覆するかまたは導電層の上面および側面の両方を被覆するかまたは導電層が形成されている全ての場所を被覆する電極であって;導電層および酸化保護層を同時に空気焼成することによって形成される電極である。 (もっと読む)

半導体装置の製造方法

【課題】素子の特性の変動を抑えること。

【解決手段】面方位が(100)面のシリコン基板1の表面に、1nm以下の酸化膜10を形成する。そして、この酸化膜10の表面に、スパッタリングによってアルミニウムを積層することで、全面が(111)面のアルミニウム膜2を形成する。そして、アルミニウム膜2の表面に、無電解めっき処理によりニッケルめっき層を形成する。また、アルミニウム膜2を形成した後、シリコン基板1とアルミニウム膜2とをシンタリングする際に、酸素濃度に合わせて、熱処理温度を調整する。

(もっと読む)

薄膜トランジスタ

【課題】信頼性が高く、耐酸化性に優れる薄膜トランジスタを提供すること。

【解決手段】基板2上に、ゲート電極3、ゲート絶縁層4、半導体層5、ソース電極6およびドレイン電極7を形成してなる薄膜トランジスタであって、アルカリ可溶性フェノール樹脂(A)と感放射線化合物(B)とを含有する感放射線性樹脂組成物からなる保護膜8が、前記ゲート絶縁層4、前記半導体層5、前記ソース電極お6よび前記ドレイン電極7に接触して形成されていることを特徴とする薄膜トランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極周辺の寄生容量を低減させることのできる半導体装置の製造方法を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する。ゲート絶縁膜上に、その上部に絶縁膜を有するゲート電極を形成する。ゲート電極を形成した後、半導体基板とゲート電極を覆う第1シリコン酸化膜を形成する。第1シリコン酸化膜を形成した後、第1シリコン酸化膜を覆う第1シリコン窒化膜を形成する。第1シリコン窒化膜を形成した後、第1シリコン窒化膜を覆う第2シリコン酸化膜を形成する。第2シリコン酸化膜を形成した後、第2シリコン酸化膜をエッチングして、第2シリコン酸化膜をゲート電極の側壁部に残す。第2シリコン酸化膜をゲート電極の側壁部に残す工程の後、半導体基板に不純物拡散層を形成する。不純物拡散層を形成した後、第2シリコン酸化膜を除去する。第2シリコン酸化膜を除去した後、半導体基板を覆う第2シリコン窒化膜を形成する。

(もっと読む)

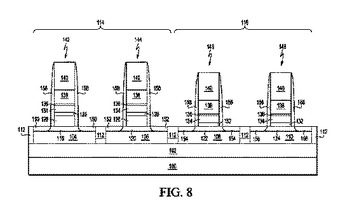

酸素拡散バリア層を有する半導体デバイスおよびそれを製造するための方法

方法および装置はトランジスタを製造するために提供される。トランジスタが、半導体材料104、106、108、110上に配置されたゲートスタック142、144、146を備える。ゲートスタックが、半導体材料上に堆積される酸化物層126、堆積された酸化物層上に配置された酸素拡散バリア層128、酸素拡散バリア層上に配置された高誘電率の誘電体層134、および高誘電率の誘電体層上に配置された酸素ゲッター導電性層138を備える。酸素拡散バリア層が、堆積された酸化物層から酸素ゲッター導電性層への酸素の拡散を防止する。  (もっと読む)

(もっと読む)

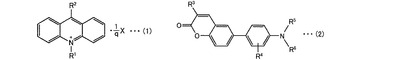

光照射によって誘電率が変化する膜およびそれを用いた電子デバイス

【課題】光照射によって誘電率を変化させることが可能な膜、およびそれを用いた電子デバイスを提供する。

【解決手段】薄膜トランジスタ20は、ガラス基板21、ゲート電極22、ゲート絶縁膜23、半導体層(活性層)24、ソース電極25およびドレイン電極26を備える。ゲート電極22、ゲート絶縁膜23および半導体層24は、この順序でガラス基板21上に積層されている。ソース電極25およびドレイン電極26は、半導体層24上に形成されている。ゲート絶縁膜23は、有機重合体と、その有機重合体中に分散された化合物とを含む溶液を、ガラス基板上に形成されたゲート絶縁膜上にスピンコート法によって塗布した。その化合物は、以下の式(1)で表される化合物および以下の(2)で表される化合物から選ばれる少なくとも1種の化合物である。[化学式(1)および(2)] (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】 高誘電率ゲート絶縁膜を用い、PMOS、NMOSそれぞれに適した仕事関数を有するCMOSFETを有する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板の主面に素子分離領域によって、絶縁分離されたP型及びN型領域を形成する工程と、前記第P型及びN型領域上にシリコン酸化膜或いはシリコン酸窒化膜からなる第一の絶縁膜を形成する工程と、前記P型領域上の前記第一の絶縁膜上にランタン酸化膜を形成する工程と、前記P型領域上の前記ランタン酸化膜及び前記N型領域上の前記第一の絶縁膜上にハフニウム或いはジルコニウムを含む第二の絶縁膜を形成する工程と、前記第二の絶縁膜上にTixNyとするとx/y<1を満たすチタンナイトライド膜を形成する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート構造としてメタル電極/High−k膜構造を用いた半導体装置において、仕事関数の制御とEOTの薄膜化とを両立させる。

【解決手段】半導体基板101におけるnチャネルMISトランジスタ形成領域の上に、ゲート絶縁膜として、第1の高誘電率絶縁層202、アルミニウム含有層203、ランタン含有層204及び第2の高誘電率絶縁層205を順次形成する。その後、ゲート電極形成を行う。

(もっと読む)

121 - 130 / 487

[ Back to top ]