国際特許分類[H01L23/12]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | マウント,例.分離できない絶縁基板 (9,861)

国際特許分類[H01L23/12]の下位に属する分類

形状に特徴のあるもの (436)

材料またはその電気特性に特徴のあるもの (925)

国際特許分類[H01L23/12]に分類される特許

981 - 990 / 8,500

半導体パッケージの製造方法

【課題】接続端子となるパッドが狭小化された半導体パッケージに対しても、はんだボールを確実に搭載することができかつ接続信頼性に優れた製造方法を提供すること。

【解決手段】この発明は、パッド102の周縁部を取り囲むソルダーレジスト103上に、パッド102から離れるに連れて開口面積が大きくなり、パッド102と対向する開口121を有するボール案内部120を形成する。次に、パッド102にフラックス109を塗布し、ボール案内部120上に、ボール振込み開口110aが形成されたマスク110を載置する。次に、マスク110を介してはんだボール111をパッド102上に搭載し、はんだボール111をパッド102に接合させ、はんだバンプ112を形成する。さらに、フラックス洗浄処理をし、ソルダーレジスト103上に形成されたボール案内部120を除去する。

(もっと読む)

樹脂ペースト組成物

【課題】低温(125℃)以下で硬化でき、接着強度に優れるとともにブリードアウトを生じることなる、作業性が良好な樹脂ペースト組成物を提供する。

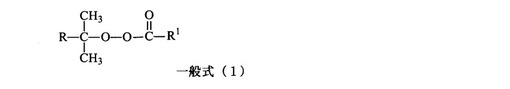

【解決手段】(A)アクリル酸エステル化合物及びメタクリル酸エステル化合物から選択される化合物、(B)下記一般式(1)で表され、且つ10時間半減期温度が60〜80℃である過酸化物、(C)可とう化材、及び、(D)非球状フィラー及び球状フィラーを含む充填材を含有してなる樹脂ペースト組成物。

(式(1)中、Rは炭素数1〜10のアルキル基、又2−アシルパーオキシプロピル−2−イル−アルキレン基を示し、R1は炭素数3〜10のアルキル基を示す。)

(もっと読む)

半導体ウェハおよびそれにより形成した半導体装置

【課題】半導体ウェハの保護層に形成された溝のアスペクト比が0.5以上である場合においても、再配線を形成する際のレジスト膜に破壊が生じることを防止する手段を提供する。

【解決手段】半導体ウェハが、集積回路を形成した複数の能動領域と、隣合う能動領域間に設けられたダイシング領域と、能動領域とダイシング領域とを覆う保護層5と、保護層の能動領域の外側を掘込んで形成されたガイド溝21と、能動領域の保護層上を覆う保護膜7と、保護膜上に形成され、集積回路に電気的に接続する第2の配線9とを備え、ガイド溝のアスペクト比が0.5以上の場合にそのガイド溝を保護膜で覆う。

(もっと読む)

半導体パッケージの製造方法

【課題】接続端子とバンプ間の接合強度に優れ、信頼性の高い半導体パッケージを提供する。

【解決手段】最上層の導体回路上にはんだバンプ形成用のソルダーレジスト開口を有するソルダーレジスト層を設け、はんだバンプ形成用開口内にはんだバンプを形成する。このとき、少なくとも下記a〜dの工程を有する。

a:ソルダーレジスト形成よりも後に基板全面に無電解銅めっき層を形成し、凹型形状の導体パッドを形成する工程、b:前記無電解銅めっき層上の開口部を除くソルダーレジスト上に対してめっきレジスト層を形成し、前記はんだバンプ形成用開口内の無電解銅めっき層上に金属被覆処理を施す工程、c:前記めっきレジスト層を除去する工程、d:前記無電解銅めっき層を除去する工程

(もっと読む)

半導体装置及びその製造方法

【課題】電解メッキで形成する柱状電極の頭頂面を平坦面に近づけるようにする半導体装置を提供する。

【解決手段】半導体ウエハ上にシード層を積層し、上部配線23及び枠状の上部ランド24をシード層上に形成し、ドライフィルムレジストをシード層上に形成して、上部配線23をドライフィルムレジストで覆うとともに、上部ランド24及びその内側のシード層をドライフィルムレジストから露出させ、上部ランド24及びシード層を電極として電解メッキを行い、上部ランド24上及び上部ランド24内のシード層上に柱状電極25を成長させ、ドライフィルムレジストを除去して、シード層のうち上部ランド24、上部配線23及び柱状電極25に重なっていない部分を除去し、柱状電極25の周囲において半導体ウエハ上に封止層26を積層して、その封止層26でその上部配線23を覆う。

(もっと読む)

配線基板

【課題】 小型で、端子電極と絶縁基板との接合強度の高い配線基板を提供することにある。

【解決手段】 本発明の配線基板は、絶縁基板1と、絶縁基板1の上面に配置された端子電極2と、端子電極2に接合されて、絶縁基板1の面方向に延びたリード端子5とを備えた配線基板において、端子電極2から絶縁基板1内に突出した金属体2aを有し、金属体2aは少なくとも、リード端子5の延びる方向と反対側の、端子電極2の端部に配置されている。リード端子5に絶縁基板1の面方向に引っ張られるような応力が加わることで、端子電極2に引っ張られる力が加わっても、金属体2aが絶縁基板1内に引っかかるので、端子電極2が絶縁基板1から剥がれることを抑制できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 外部接続用電極の周囲を封止膜で覆ったCSPと呼ばれる半導体装置において、封止膜の上面側を研削するとき、外部接続用電極の上面にバリが発生しないようにする。

【解決手段】 メッキレジスト膜を用いた電解メッキにより外部接続用電極10を形成した後に、サーフェスプレーナーを用いて全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜の上面側を切って除去し、外部接続用電極10の高さを揃える。この場合、外部接続用電極10の上面にバリが発生することはない。次に、メッキレジスト膜を剥離し、封止膜11を形成し、封止膜11の上面側を研削し、外部接続用電極10上に封止膜11が僅か例えば厚さ数μm〜10μm残るようにする。この場合、外部接続用電極10の上部は研削しないため、外部接続用電極10の上面にバリが発生することはない。次に、外部接続用電極10の上面中央部に対応する部分における封止膜11に、レーザビームを照射するレーザ加工により、開口部12を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】柱状電極の中心間隔を小さくしたとしてもレジスト残渣の発生を抑制することで、歩留まりを高める半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に設けられ、ランドを有する配線と、ランド上に設けられた柱状電極とを備えている。柱状電極におけるランドに接触している面の形状は、3点以上の凸曲線からなる凸部20bと、凸部のそれぞれを結ぶ凹曲線20cからなる辺部とを有する。

(もっと読む)

半導体パッケージ基板の検査方法、半導体パッケージ基板の製造方法、半導体パッケージ基板

【課題】コンデンサ実装後に半導体パッケージ基板出荷する場合の電気検査において、コンデンサを破壊することなく絶縁性を保証でき、検査工程を増やすことがない検査方法、半導体パッケージ基板を提供する。

【解決手段】フリップチップBGAパッケージ用基板1上にコンデンサ13を実装するための1対の金属バンプ15のうち、少なくとも一方に接続する金属配線5の一部が検査用プローブB−1、B−2との接触のためソルダーレジスト4’から露出され、露出されているパッド部10がコンデンサ13と導通するパッド部10a、コンデンサ13と導通しないパッド部10bとに分離されていて、パッド部10a、10bのそれぞれに検査用プローブB−1、B−2を接触させて電気検査を行う。

(もっと読む)

実装基板

【課題】ICチップの接続用端子と導体パターンとがソルダーレジストに形成された開口部に敷設される半田を介して電気接続され、ソルダーレジストとICチップ間の隙間で電気接続部以外がアンダーフィルによって充填された実装基板において、短時間でアンダーフィルを充填するとともに、ボイドの発生を抑制し、信頼性を向上させた実装基板を提供する。

【解決手段】アンダーフィル7によって被覆されるソルダーレジスト6r部分が接続用開口部の設置ピッチよりも狭い幅の溝9aを備えており、これらの溝9aが、各接続用開口部間にストライプ状に縫うように、あるいは開口部を格子状、多角形形状、円形状、楕円形状で囲うように、あるいは波状に縫うように形成され、その断面形状がU字型、V字型、矩型のいずれかである実装基板である。

(もっと読む)

981 - 990 / 8,500

[ Back to top ]