国際特許分類[H01L23/32]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の完全装置を支持する支持体,すなわち分離できる定着物 (458)

国際特許分類[H01L23/32]に分類される特許

31 - 40 / 458

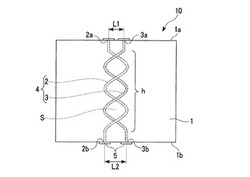

貫通配線基板

【課題】電磁界による影響を受け難く、信号ノイズの発生が低減された貫通配線基板の提供。

【解決手段】(1)基板1を構成する複数の面のうち、何れか2つの面を結ぶ微細孔が基板1内に配され、該微細孔内に導電性物質が配されてなる貫通配線を複数設けた貫通配線基板10であって、前記複数の貫通配線のうち少なくとも2本の隣接した貫通配線2,3からなるペア配線4が、その長手方向の少なくとも一区間hにおいて互いにツイストすることを特徴とする貫通配線基板10。(2)ペア配線4が差動伝送路を構成することを特徴とする(1)に記載の貫通配線基板10。

(もっと読む)

積層板、回路基板、半導体パッケージおよび積層板の製造方法

【課題】反りが低減され、薄型回路基板として適した積層板を提供すること。

【解決手段】繊維基材層と樹脂層を備える複数のプリプレグが積層されてなり、上部に配線層が形成されるか、またはビルドアップ層が形成される積層板であり、積層方向において、一方の面110に最も近く配置された第一繊維基材層101の中心線A1と、第一繊維基材層101に隣接する第二繊維基材層101aの中心線A3との距離をD1とし、他方の面111に最も近く配置された第三繊維基材層105の中心線A2と、第三繊維基材層105に隣接する第四繊維基材層105aの中心線A4との距離をD2とし、当該積層板の厚さをD3とし、当該積層板中の繊維基材層の数をn(ただし、nは2以上の整数である。)としたとき、下記式(1)および(2)の条件をいずれも満たす積層板100cである。

D3/n<D1 (1)

D3/n<D2 (2)

(もっと読む)

半導体装置、および配線基板

【課題】信頼性の高い半導体装置を実現する。

【解決手段】半導体装置100は、配線基板10と、配線基板10上に実装された半導体チップ20と、を備えている。配線基板10は、一面において半導体チップ20と対向する基材52と、配線基板10を、半導体チップ20を除く外部に接続する端子40と、基材52の一面上に設けられ、かつ端子40に接続するダミー配線32と、基材52上およびダミー配線32上に設けられた絶縁膜と、を有している。

(もっと読む)

配線基板、半導体装置及び配線基板の製造方法

【課題】配線基板に内蔵されるキャパシタの大容量化を容易に実現することのできる配線基板、半導体装置及び配線基板の製造方法を提供する。

【解決手段】配線基板1は、第1主面R1と第2主面R2との間を貫通する貫通孔10Xを有する基板本体10と、貫通孔10Xに形成された貫通電極12と、基板本体10の第1主面及び貫通孔10Xの内壁面を覆う絶縁膜11上に、第1電極22と誘電体層23と第2電極24とが順に積層されて形成されたキャパシタ部21を有するキャパシタ20を備えている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】信頼性に優れた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、主面に複数の埋込導電部(埋込導電部106)が設けられたシリコンウエハ102と、シリコンウエハ102の主面に配置された、埋込導電部106に電気的に接続する複数の第1の半導体素子(半導体チップ108)と、を備える構造体を用意する工程と、半導体封止用樹脂組成物を用いて、シリコンウエハ102の主面上の複数の半導体チップ108を封止する封止材層110を形成する工程と、シリコンウエハ102の裏面を研削して、裏面に埋込導電部106を露出させて、貫通プラグ105とする工程と、を含む。

(もっと読む)

IC及びマザーボードの間の入出力信号の計測方法

【課題】アダプタ基板を用いたIC及びマザーボードの間の入出力信号の計測方法であって、パッドの近傍に部品が存在している場合においても、アダプタ基板を実装することができるための手段を得る。

【解決手段】マザーボードとアダプタ基板とのとの間に測定すべきICと同じ大きさの中継基板を配置させる。また、中継基板を多層構造とし、中継基板の内層を電源層及びグラウンド層の組とする。

(もっと読む)

インターポーザおよびその製造方法

【課題】インターポーザに半導体装置を実装する際の、実装不良を抑制することを目的とする。

【解決手段】貫通電極6の絶縁樹脂13上に、突起20を設けることにより、半田バンプ3を介してインターポーザ16に半導体装置1を実装する際の加熱により、絶縁樹脂13が熱分解により低分子化され変質する率を低減し、実装不良を抑制することができる。

(もっと読む)

誘電体膜の製造方法、デカップリングキャパシタの製造方法及びデカップリングキャパシタ

【課題】 誘電体膜の製造方法、デカップリングキャパシタの製造方法及びデカップリングキャパシタに関し、内部端子のピッチを外部端子のピッチより大きくして容量をより大きくすることを可能にする膜強度を有する粒子充填度の高い誘電体膜を得る。

【解決手段】 平均粒径が600nm乃至800nmに分級した第1の母粒子群と、前記第1の母粒子群と同じ組成で且つ平均粒径が150nm乃至200nmに分級した第2の母粒子群と、前記第1の母粒子群と同じ組成で且つ平均粒径が50nm以下の第3の母粒子群とを気体中に浮遊させ、前記浮遊した第1乃至第3の母粒子群をノズルにより成膜基板上に吹き付けて、前記成膜基板上に誘電体膜を成膜する。

(もっと読む)

インターポーザ基板、インターポーザ基板の製造方法、及び電子装置

【課題】電子部品及びインターポーザ基板の隙間を狭小化しても、電子部品及びインターポーザ基板の隙間を充分に確保することが出来るインターポーザ基板を提供すること。

【解決手段】基板本体11と、前記基板本体11の表面に設けられ、電子部品30の突起端子32を接続するための電極パッド15を有する配線パターン12と、前記配線パターン12の前記電極パッド15の周囲に選択的に形成され、前記電極パッド15より半田の濡れ性が低い金属膜13と、を備えるインターポーザ基板。

(もっと読む)

配線基板及びその製造方法

【課題】半導体素子の実装時等において発生し得る基板の反りを低減すること。

【解決手段】配線基板10は、複数の配線層が絶縁層を介在させて積層され、半導体素子が搭載される第1面側と、これと反対側に位置する第2面側とを有している。第1面側に位置する最外層の絶縁層12には、搭載される半導体素子と電気的に接続されるインターポーザ30が埋設され、第2面側に位置する最外層の絶縁層20には、シート状部材40が埋設されている。インターポーザ30とシート状部材40は、互いに対称となる位置に配設されている。

(もっと読む)

31 - 40 / 458

[ Back to top ]