国際特許分類[H01L23/32]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 半導体または他の固体装置の細部 (40,832) | 動作中の完全装置を支持する支持体,すなわち分離できる定着物 (458)

国際特許分類[H01L23/32]に分類される特許

11 - 20 / 458

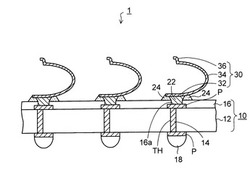

スプリング端子付き基板及びその製造方法

【課題】スプリング端子付き基板において、スプリング端子のはんだ接続部を補強すること。

【解決手段】接続パッドPを備える基板10と、接続部32がはんだ層22によって接続パッドPに接続されたスプリング端子30と、はんだ層22の側面を覆って形成された補強樹脂部24とを含む。はんだ層22及び補強樹脂部24は、樹脂含有はんだペーストから形成される。

(もっと読む)

半導体実装部材及び半導体実装部材の製造方法

【課題】 多配線への対応及び電源強化を図りながら歩留まりが下がらない半導体実装部材を提供する。

【解決手段】 半導体実装部材100を第2基板110と第1基板10との2つのプリント配線板で構成するため、多配線への対応及び電源強化の目的で、1枚のビルドアップ基板の層数を増やしサイズを大きくするのと比較し、歩留まりが低下しない。第1基板10と第2基板110との間に支持体188が介在するので、第1基板10と第2基板110との間にアンダーフィルを充填させる必要が無い。

(もっと読む)

電子装置、電子装置の製造方法及び中継基板

【課題】接続信頼性に優れた電子装置を提供する。

【解決手段】電子装置1は、回路基板10と電子部品30が、それらの間に配置された中継基板20を介して、電気的に接続される。中継基板20は、熱膨張性の絶縁基板21と、絶縁基板21に設けられた貫通孔22と、貫通孔22の内壁に設けられた導電部23とを含む。回路基板10と電子部品30は、互いの突起電極10a,30aが、中継基板20の熱膨張性の絶縁基板21に設けられた貫通孔22に挿入され、その貫通孔22の内壁に設けられた導電部23と接触することで、電気的に接続される。

(もっと読む)

半導体装置

【課題】信号伝送速度を高速化しても信頼性が高く、かつ、汎用的なリードフレームを利用可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、内側ワイヤボンディング20、内側ボンディング用端子100、配線110、外側ボンディング用端子120、外側ワイヤボンディング30を具備し、この順に、ボンディングパッド90からインナーリード60までを電気的に接続する信号伝送手段を有する。内側ボンディング用端子100、配線110、外側ボンディング用端子120は、絶縁性部材40上に形成されている。信号伝送手段は、ボンディングパッド90から前記アウターリード70の先端までの信号伝送路の距離が実質的に等しくなるように、配線110の配線長によって調整されている。

(もっと読む)

電子部品

【課題】応力緩和機能を備える新規な構造の電子部品を提供する。

【解決手段】接続電極Eと、下側に空間が設けられた状態で接続電極Eに接続され、本体部40a(膨出部)と、本体部40aの上面に設けられた突出接続部40bとを備え、圧力によって弾性変形する可撓性電極端子40とを含む。可撓性電極端子40は、実装基板、インターポーザ、半導体チップ又はプローブ基板などの外部接続端子として設けられる。

(もっと読む)

電子部品とその製造方法

【課題】電子部品とその製造方法において、従来よりも微細な導体パターンを形成すること。

【解決手段】導体プレート124の一方の主面124xに形成されたパターン124wを、樹脂基材121の電極パッド122に接続する工程と、導体プレート124と樹脂基材121との間に樹脂を注入して樹脂層123を形成する工程と、樹脂層123が現れるまで導体プレート124の他方の主面124yに対して研磨、CMP 、又は切削を行い、パターン124wを樹脂層123に導体パターン124zとして残す工程とを有する電子部品の製造方法による。

(もっと読む)

電子部品とその製造方法、及びコネクタ

【課題】電子部品とその製造方法、及びコネクタにおいて、パッケージ基板とコネクタとを電気的に良好に接続すること。

【解決手段】パッケージ基板8と、バネ21を介してパッケージ基板8と電気的に接続されているコネクタ5有することを特徴とする電子部品による。

(もっと読む)

インターポーザ及びその製造方法、並びに半導体装置及びその製造方法

【課題】シリコン基板上の有機絶縁膜の内部応力よって引き起こされる反りを緩和することができるインターポーザを提供する。

【解決手段】複数の貫通電極10を有するシリコン基板1と、シリコン基板1の一方の面に形成された有機絶縁膜220と、シリコン基板1の他方の面に形成され、貫通電極10と電気的に接続された外部接続用端子(電極パッド3又はハンダバンプ14)とを有し、貫通電極10の間に位置する有機絶縁膜220に切り欠き部30が形成されている。

(もっと読む)

半導体装置、電子装置、配線基板、半導体装置の製造方法、及び配線基板の製造方法

【課題】配線基板に半導体素子を形成する場合において、配線基板の製造工程数を少なくする。

【解決手段】コア層200の一面上には、第1配線232が設けられている。第1配線232上、及びその周囲に位置するコア層200の一面上には、半導体層236が形成されている。第1配線232及び半導体層236は、半導体素子を形成している。本実施形態において半導体素子は、第1配線232をゲート電極としたトランジスタ230であり、半導体層236と第1配線232の間に、ゲート絶縁膜234を有している。

(もっと読む)

電子機器用基板及び電子機器

【課題】電気抵抗の低い貫通電極構造、または、放熱特性に優れた熱伝導路を有する電子機器用基板及びそれを用いた電子機器を提供すること。

【解決手段】基板1は、複数の貫通電極2及び柱状ヒートシンク3の少なくとも一方を有する。貫通電極2は、カーボンナノチューブを含有し、基板1に設けられたビア20を鋳型とする鋳込み成形体でなる。柱状ヒートシンク3は、基板に設けられたビア30を鋳型とする鋳込み成形体でなり、炭素原子構造体を含有する。

(もっと読む)

11 - 20 / 458

[ Back to top ]