国際特許分類[H01L25/07]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678) | すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439) | 個別の容器を持たない装置 (7,415) | 装置がグループ29/00に分類された型からなるもの (4,054)

国際特許分類[H01L25/07]に分類される特許

81 - 90 / 4,054

半導体装置

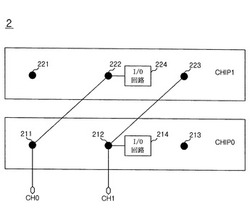

【課題】本発明は、積層されるチップに形成される貫通ビアの多様な連結構造を含む半導体装置を提供する。

【解決手段】半導体装置は、積層される第1および第2チップを備える。第1及び第2チップに垂直な同一線上に位置し、各々第1及び第2チップを貫通して形成される第1ないし第3貫通ビアと、第1チップの第2貫通ビアと連結される第1入出力回路及び第2チップの第2貫通ビアと連結される第2入出力回路とを備える。

(もっと読む)

ポリマーナノコンポジット樹脂組成物

【課題】耐熱性の高さの指標であるガラス転移温度が高く、且つ高密着性及び低吸湿性を実現するポリマーナノコンポジット樹脂組成物を提供することを目的とする。

【解決手段】熱硬化性樹脂3と、硬化剤4と、シルセスキオキサン誘導体2により表面改質処理された無機ナノフィラー1とを含んでなるポリマーナノコンポジット樹脂組成物、かかる組成物を硬化してなるポリマーナノコンポジット樹脂硬化物、かかる組成物の製造方法、かかる組成物により封止してなる半導体モジュール、ならびに半導体モジュールの製造方法を提供する。

(もっと読む)

半導体装置、半導体装置モジュールおよび半導体装置の製造方法

【課題】半導体装置と外部回路とを接続させる際、モールドパッケージの外側において余分なスペースが発生せず、またはんだを用いず当該接続を可能せしめる半導体装置を提供する。

【解決手段】半導体装置100は、半導体素子1,2および電極端子部3,4,6がモールドパッケージ部9により覆われている。また、モールドパッケージ部9の第一の主面内には、底面から電極端子部3,4,6が露出している第一の開口孔10,11が形成されている。そして、第一の開口孔10,11の開口部を塞ぐように、第一の主面上に固定される外部接続部材17A,17B,17Cと、第一の開口孔10,11の内部に配設され、弾性を有し、電極端子部3,4,6と外部接続部材17A,17B,17Cとを電気的に接続する第一のコンタクト部材16A,16B,19とを、備えている。

(もっと読む)

半導体装置

【課題】回路配線パターンのレイアウトの自由度の高さを有し、かつ、高い組立性を有し、かつ、厳しい温度環境下においても部材接続信頼性を維持するようなパワー半導体装置を提供すること。

【解決手段】交流端子の基板接続端と直流端子の基板接続端とは、ケースの外周部において対向するように配置され、交流端子と直流端子それぞれは、基板接続端と外部機器接続端との間に基板の主面と略平行な平面部(130b、131b、132b)を有し、交流端子と直流端子それぞれは、平面部よりも幅の狭い連結部(130c、131c)を有し、交流端子と直流端子は、交流端子の基板接続端側において連結部によって連結される。

(もっと読む)

半導体装置

【課題】コントローラによるメモリに対するデータの読み書きの高速化が可能な半導体装置を提供する。

【解決手段】実施の形態によれば、半導体装置が提供される。半導体装置は、パッケージ基板と、パッケージ基板上に実装され、個別に機能が割り当てられて第1の順序で配列された複数の第1ボンディングパッドを上面に有する第1の半導体チップと、第1の半導体チップよりも外形が小さく、第1の半導体チップの上に配置され、複数の第1ボンディングパッドの各々と対応する機能が割り当てられて、第1の順序で並ぶように配列された複数の第2ボンディングパッドを上面に有する第2の半導体チップと、第1ボンディングパッドと第2ボンディングパッドとを接続する第1ボンディングワイヤと、を有する。

(もっと読む)

配線シート付き配線体、半導体装置、およびその半導体装置の製造方法

【課題】製造工程を簡略化することのできる配線シート付き配線体、半導体装置、およびその半導体装置の製造方法を提供する。

【解決手段】第1主面11にソース電極14およびゲート電極15が形成されかつ第2主面12にドレイン電極13が形成されたスイッチング素子10と、ドレイン電極13に接続された導電層積層基板80とを備える半導体装置1に対して、配線シート付き配線体30は、上側配線構造体として適用される。配線シート付き配線体30は、ソース電極14に接続される第1配線体40と、ゲート電極15に接続されるゲート端子が設けられた配線シート60とを備える。第1配線体40においてソース電極14が接続される面に配線シート60が取り付けられている。

(もっと読む)

三次元実装装置

【課題】半導体デバイスの製造のスループットをさらに向上できるとともに、製造される半導体デバイスの品質の低下を防止できる三次元実装装置を提供する。

【解決手段】三次元実装装置11において、搬送トレイ16は配置面16aaを含む内側トレイ16aを有し、且つ該配置面16aaに配置された8つの積層チップ21を搬送し、チャンバ27は内側トレイ16aを収容し、下部ステージ28はチャンバ27内において内側トレイ16aを載置し、上部ステージ29は、下部ステージ28に載置された内側トレイ16aにおける配置面16aaと平行な押圧面29aを有し、下部ステージ28及び上部ステージ29はそれぞれヒータ33,39を内蔵し、下部ステージ28及び上部ステージ29が間を詰めるように移動する。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

ダイ積層システムおよび方法

【課題】ダイ積層システムを持つ大きい電気的伝導性表面領域を有する半導体デバイスを提供する。

【解決手段】システム100は、代表的ワイアボンド120等のワイアボンド群を介して、第一のダイ102に結合される半導体デバイスパッケージ基板101を含んでいる。この第一のダイは、パッシベーション領域104と、ボンドパッド領域106のような伝導性ボンドバッド領域と、第一の積層ダイ受容領域108と、第二の伝導性積層ダイ受容領域110と、を含む表面を有する。この第一の伝導性積層ダイ受容領域は、少なくとも第二のダイ112を受容できるサイズとされている。この第二の伝導性積層ダイ受容領域は、少なくとも第三のダイ114を受容できるサイズとされている。各伝導性積層ダイ受容領域およびは、ボンドパッド領域のような従来のボンドパッド領域より広い伝導性領域を有する。

(もっと読む)

異物検査装置および半導体製造装置

【課題】薄くされたチップを積層して半導体装置を製造する際に、処理対象の上面に存在する異物によって積層させるチップが割れてしまうことを防ぐ異物検査装置を提供する。

【解決手段】実施形態によれば、異物検査装置20は、下地検査部221および下地検査部221を支持する支持部222を有する検知ヘッド22と、下地データ格納部233、検査制御部232および異物存在判定部234を有する制御部23と、を備える。下地データ格納部233は、配線基板80または配線基板80の最上層のチップの配置位置を示す下地配置領域を含む下地データを格納する。検査制御部232は、検知ヘッド22を検査対象上の所定の位置に接触させながら所定の力で押圧するように制御する。異物存在判定部234は、下地検査部221から取得した検査データから、下地データを参照して下地配置領域のうち周囲よりも圧力が高まっている領域を異物存在領域として抽出する。

(もっと読む)

81 - 90 / 4,054

[ Back to top ]