国際特許分類[H01L25/07]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678) | すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439) | 個別の容器を持たない装置 (7,415) | 装置がグループ29/00に分類された型からなるもの (4,054)

国際特許分類[H01L25/07]に分類される特許

71 - 80 / 4,054

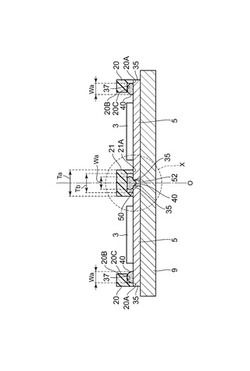

パワーモジュール

【課題】ケースを固定する接着剤の塗布量を抑え、なおかつパワーデバイスへのはみ出しを防止できるパワーモジュールを提供すること。

【解決手段】パワーデバイス3を載置した複数のベース板5を並べて配置し、これらのベース板5をケース7で囲んだパワーモジュール1において、前記ケース7は、複数の前記ベース板5の全てを囲む外囲壁20と、隣り合う前記ベース板5同士の間に沿って配置される仕切壁21と、を備え、前記外囲壁20、及び前記仕切壁21の底面20A、21Aが前記ベース板5の上面に接着剤40で接着されるとともに、前記仕切壁21の底面21Aには、前記ベース板5同士の間に沿って延在し、隣り合う前記ベース板5同士の間に塗布された接着剤40を封じる溝50を設けた。

(もっと読む)

半導体装置

【課題】配線基板上にメモリチップとコントローラチップとを積層したパッケージ構造を備えた半導体装置において、メモリチップとコントローラチップを接続する配線の自由度を向上させる。

【解決手段】メモリカード1Aは、配線基板2とその主面上に積層された4枚のメモリチップM1〜M4と最上層のメモリチップM4の表面上に実装されたコントローラチップ3およびインターポーザ4とを備えている。メモリチップM1〜M4のそれぞれは、その長辺を配線基板2の長辺と同じ方向に向けた状態で配線基板2の表面上に積層されている。最下層のメモリチップM1は、配線基板2のパッド9と重ならないよう、メモリカード1Aの先端部方向に所定距離ずらした状態で配線基板2上に実装されている。メモリチップM1上に積層された3枚のメモリチップM2〜M4は、パッド6が形成されている側の短辺がメモリカード1Aの先端部に位置するように配置されている。

(もっと読む)

半導体ウエハーの接合方法および半導体装置の製造方法

【課題】積層された半導体ウエハーが備える接続部間の電気的な接続を安定的に行い得るとともに、効率よく複数の半導体素子を製造し得る半導体ウエハーの接合方法および信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体ウエハーの接合方法では、半導体ウエハー210と半導体ウエハー220との間に、フラックス活性を有する硬化剤と、熱硬化性樹脂とを含む接合層60を介在させて、半導体ウエハー210、220が積層された半導体ウエハー積層体230を得た後に、半導体ウエハー積層体230を、加熱しつつ、その厚さ方向に加圧することにより、半田バンプ224を溶融・固化するとともに、前記熱硬化性樹脂を硬化して、半導体ウエハー210と半導体ウエハー220とが固着することにより、接続部(半田バンプの固化物)225で、接続部212と接続部222とが電気的に接続された半導体ウエハー接合体240を得る。

(もっと読む)

積層型半導体装置、プリント回路板、及びプリント配線板の接合構造

【課題】はんだの高さを確保し、接合の信頼性を向上させることができる接合体、該接合体を用いることで小面積化が可能な半導体装置、該接合体でプリント配線板に接合される半導体装置を有するプリント回路板を提供する。

【解決手段】プリント回路板100は、半導体素子1が実装され、片面に電極パッド8が形成されたインターポーザ2と、インターポーザ2に対向する片面に電極パッド9が形成されたプリント配線板3と、電極パッド8,9を接合する接合体70と、を備えている。接合体70は、はんだ層60と、電極パッド8,9に接合された金属層50,50と、を有している。各金属層50,50は、金属粒子同士が結合して形成された金属粒子集合体10と、金属粒子集合体10の隙間に埋められたはんだ11とからなる。

(もっと読む)

半導体装置

【課題】回路配線パターンのレイアウトの自由度の高さを有し、かつ、高い組立性を有し、かつ、厳しい温度環境下においても部材接続信頼性を維持するようなパワー半導体装置を提供すること。

【解決手段】交流端子の基板接続端と直流端子の基板接続端とは、ケースの外周部において対向するように配置され、交流端子と直流端子それぞれは、基板接続端と外部機器接続端との間に基板の主面と略平行な平面部(130b、131b、132b)を有し、交流端子と直流端子それぞれは、平面部よりも幅の狭い連結部(130c、131c)を有し、交流端子と直流端子は、交流端子の基板接続端側において連結部によって連結される。

(もっと読む)

半導体装置

【課題】コントローラによるメモリに対するデータの読み書きの高速化が可能な半導体装置を提供する。

【解決手段】実施の形態によれば、半導体装置が提供される。半導体装置は、パッケージ基板と、パッケージ基板上に実装され、個別に機能が割り当てられて第1の順序で配列された複数の第1ボンディングパッドを上面に有する第1の半導体チップと、第1の半導体チップよりも外形が小さく、第1の半導体チップの上に配置され、複数の第1ボンディングパッドの各々と対応する機能が割り当てられて、第1の順序で並ぶように配列された複数の第2ボンディングパッドを上面に有する第2の半導体チップと、第1ボンディングパッドと第2ボンディングパッドとを接続する第1ボンディングワイヤと、を有する。

(もっと読む)

電力変換装置

【課題】主回路インダクタンスを低減でき、かつ、電流振動が発生する周波数帯域で高抵抗になる導体形態を有する電力変換器を提供することにある。

【解決手段】上記の課題を解決する手段として、正極側電流を流す導体と絶縁シートと負極側電流を流す導体とを積層接着させ、各々の導体に流れる電流の経路を対向させた電力変換器の主回路配線において、積層された導体の表面のうち、他方の導体側の面について、導体内部よりも高周波帯域において高抵抗な部材を用いる。

(もっと読む)

半導体装置

【課題】 多様な方式でスキャンテスト経路を形成することができる半導体装置を提供する。

【解決手段】第1チップおよび第2チップを電気的に連結する第1貫通ビアおよび第2貫通ビアと、前記第1チップに配置され、テストデータを受信するとともに前記第1貫通ビアと接続される第1回路部と、前記第1チップに配置され、前記第2貫通ビアおよび前記第1回路部と接続される第2回路部と、前記第2チップに配置され、前記第1貫通ビアと接続される第3回路部と、を含み、前記第1回路部は第1制御信号に応答して前記第1貫通ビアおよび前記第2回路部のうちいずれか一つに前記第1回路の出力信号を出力する。

(もっと読む)

半導体装置およびその製造方法

【課題】固相拡散接合により、プロセス温度が低温化され、プロセス時間が短縮化され、かつフリップチップ構造の半導体装置提供する。

【解決手段】絶縁基板8と、絶縁基板8上に配置された信号配線電極12と、絶縁基板8上に若しくは絶縁基板8を貫通して配置されたパワー配線電極16と、絶縁基板8上にフリップチップに配置され、半導体基板26と、半導体基板26の表面上に配置されたソースパッド電極SPおよびゲートパッド電極GPと、半導体基板26の裏面上に配置されたドレインパッド電極36とを有する半導体デバイス10と、ゲートパッド電極GP上に配置されたゲートコネクタ18と、ソースパッド電極SP上に配置されたソースコネクタ20とを備え、ゲートコネクタ18とゲートパッド電極GPおよび信号配線電極12、ソースコネクタ20とソースパッド電極SPおよびパワー配線電極16は、固相拡散接合される半導体装置1。

(もっと読む)

半導体モジュール

【課題】簡素な構成の半導体モジュールを提供すること。

【解決手段】半導体モジュール10は、第1構造体10Uaと第2構造体10Ubを備えている。第1構造体10Uaと第2構造体10Ubが共通形態である。第1構造体10Uaの第1出力バスバーUout1と第2構造体10Ubの高圧側バスバー10Pが共通形態であり、第1構造体10Uaの低圧側バスバー10Nと第2構造体10Ubの第2出力バスバーUout2が共通形態である。

(もっと読む)

71 - 80 / 4,054

[ Back to top ]