国際特許分類[H01L25/07]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 複数の個々の半導体または他の固体装置からなる組立体 (14,678) | すべての装置がグループ27/00〜51/00の同じサブグループに分類される型からなるもの,例.整流ダイオードの組立体 (8,439) | 個別の容器を持たない装置 (7,415) | 装置がグループ29/00に分類された型からなるもの (4,054)

国際特許分類[H01L25/07]に分類される特許

61 - 70 / 4,054

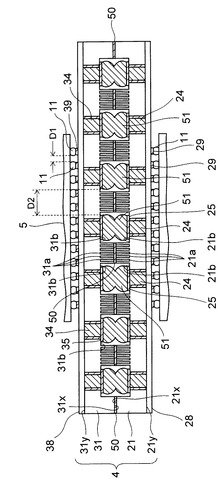

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、半導体装置を効率的に冷却すること。

【解決手段】積層された複数の半導体チップ5と、複数の半導体チップ5のいずれかの間に設けられ、冷媒が流れる複数の流路Cを備えたインターポーザ4とを有し、インターポーザ4は、一方の主面同士が互いに接合された第1の基板21と第2の基板31とを備え、第1の基板21と第2の基板31の少なくとも一方の表面により流路Cが画定された半導体装置による。

(もっと読む)

半導体装置の製造方法及び半導体装置、電子機器

【課題】空洞部の破壊を防ぐと共に、基板間の接続の信頼性を向上できるようにした半導体装置の製造方法及び半導体装置、電子機器を提供する。

【解決手段】第1の基板は、第1の面と第2の面とを有する第1の基材と、第1の基材の第1の面側に設けられた犠牲層と、第1の基材の第1の面と第2の面との間を貫通する貫通電極と、貫通電極と第1の基材との間に設けられた絶縁膜と、を有する。第2の基板は、第3の面を有する第2の基材と、第2の基材の第3の面側に設けられたバンプと、第2の基材の第3の面側に設けられ、バンプを囲む環状導電部と、を有する。第2の面と第3の面とを対向させた状態で、貫通電極とバンプとを接続すると共に、第1の基板の周縁部を環状導電部に埋入させる実装工程と、実装工程の後で、犠牲層をエッチングして第1の基材の第1の面側に空洞部を形成するエッチング工程と、を含む。

(もっと読む)

電力用半導体装置および電力用半導体装置の製造方法

【課題】小型で、信頼性の高い電力用半導体装置を得ることを目的としている。

【解決手段】電力用半導体素子21、22を接合するダイパッド11dと、ダイパッド11dに対して段差を付けられた制御素子23を接合するダイパッド12dが、並列する複数の端子11、12を形成するリードパターンとともに、端子の延在方向におけるそれぞれ一端側の領域と他端側の領域で連なり、かつ、一端側の領域から他端側の領域にかけて延在する延在パターン13、15が形成された1枚のリードフレーム10を用い、リードフレーム10の面を保ったまま、延在パターン13、15の所定部分Rbに屈曲部13b、15bを形成することにより、制御素子23が、電力用半導体素子21、22にオーバーラップするようにした。

(もっと読む)

電気部品の積層構造体の製造方法、電気部品の平面配置集合体及び電気部品の平面配置集合体の積層結合方法

【課題】より高品質、高生産性及び高歩留まりで電気部品の積層構造体を製造することができる電気部品の積層構造体の製造方法及び電気部品の平面配置集合体を提供する。

【解決手段】水平に配置されたチップ10同士の隙間を再配置材料22で固定して再配置チップ集合体20を形成し、再配置チップ集合体20同士をそれぞれのチップ10同士が対応するように重ね合わせて結合させる。このため、再配置チップ集合体20の積層構造体を一括して製造できる。再配置チップ集合体20それぞれの再配置材料を溶解可能な液体で溶解させることにより再配置チップ集合体20内のチップ10それぞれを分離して積層チップ40を形成する。ダイシングによるチップ10及びチップ10同士の結合部への機械的ダメージや歩留まりの低下が無くなる。より高品質、高生産性及び高歩留まりで電気部品の積層構造体を製造することができる。

(もっと読む)

半導体装置

【課題】自己インダクタンスの低減性能を向上させた半導体装置を提供する。

【解決手段】半導体装置は、相隔てて配置される正電極材11および負電極材13と、正電極材11と負電極材13の間において、正電極材11と負電極材13を結ぶ直線SLと平行となる平行部(凹部15a)、または正電極材と負電極材とを結ぶ曲線の接線と平行となる平行部を有する導電層(第1の導電材15)とを備える。これにより、主電流による磁束が集中する箇所に導電層の一部が配置されることになる。よって、導電層に磁束が集中し易くなり、誘導電流を効率的に発生可能となり、電極材11、13に生じる自己インダクタンスの低減性能を向上させることができる。

(もっと読む)

電力変換装置およびその製造方法

【課題】電子部品と制御回路基板を繋ぐワイヤを保持しやすく、フレームを容易に反転できる電力変換装置と、その製造方法を提供する。

【解決手段】半導体モジュール2と冷媒流路3とを有する装置本体部10をフレーム4内に固定し、フレーム4に電子部品5(平滑コンデンサ)を取り付ける。そして、フレーム4の側壁部40に形成した被係合部41に治具11を係合し、該治具11を使ってフレーム4を反転する。その後、半導体モジュール2の制御端子22に制御回路基板6を接続し、電子部品5と制御回路基板6とをワイヤ12によって接続する。そして、被係合部41にワイヤ保持具7を係合し、ワイヤ保持具7を使ってワイヤ12を保持する。

(もっと読む)

パワーモジュール

【課題】ケースを固定する接着剤の塗布量を抑え、なおかつパワーデバイスへのはみ出しを防止できるパワーモジュールを提供すること。

【解決手段】パワーデバイス3を載置した複数のベース板5を並べて配置し、これらのベース板5をケース7で囲んだパワーモジュール1において、前記ケース7は、複数の前記ベース板5の全てを囲む外囲壁20と、隣り合う前記ベース板5同士の間に沿って配置される仕切壁21と、を備え、前記外囲壁20、及び前記仕切壁21の底面20A、21Aが前記ベース板5の上面に接着剤40で接着されるとともに、前記仕切壁21の底面21Aには、前記ベース板5同士の間に沿って延在し、隣り合う前記ベース板5同士の間に塗布された接着剤40を封じる溝50を設けた。

(もっと読む)

半導体装置

【課題】配線基板上にメモリチップとコントローラチップとを積層したパッケージ構造を備えた半導体装置において、メモリチップとコントローラチップを接続する配線の自由度を向上させる。

【解決手段】メモリカード1Aは、配線基板2とその主面上に積層された4枚のメモリチップM1〜M4と最上層のメモリチップM4の表面上に実装されたコントローラチップ3およびインターポーザ4とを備えている。メモリチップM1〜M4のそれぞれは、その長辺を配線基板2の長辺と同じ方向に向けた状態で配線基板2の表面上に積層されている。最下層のメモリチップM1は、配線基板2のパッド9と重ならないよう、メモリカード1Aの先端部方向に所定距離ずらした状態で配線基板2上に実装されている。メモリチップM1上に積層された3枚のメモリチップM2〜M4は、パッド6が形成されている側の短辺がメモリカード1Aの先端部に位置するように配置されている。

(もっと読む)

半導体ウエハーの接合方法および半導体装置の製造方法

【課題】積層された半導体ウエハーが備える接続部間の電気的な接続を安定的に行い得るとともに、効率よく複数の半導体素子を製造し得る半導体ウエハーの接合方法および信頼性の高い半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体ウエハーの接合方法では、半導体ウエハー210と半導体ウエハー220との間に、フラックス活性を有する硬化剤と、熱硬化性樹脂とを含む接合層60を介在させて、半導体ウエハー210、220が積層された半導体ウエハー積層体230を得た後に、半導体ウエハー積層体230を、加熱しつつ、その厚さ方向に加圧することにより、半田バンプ224を溶融・固化するとともに、前記熱硬化性樹脂を硬化して、半導体ウエハー210と半導体ウエハー220とが固着することにより、接続部(半田バンプの固化物)225で、接続部212と接続部222とが電気的に接続された半導体ウエハー接合体240を得る。

(もっと読む)

積層型半導体装置、プリント回路板、及びプリント配線板の接合構造

【課題】はんだの高さを確保し、接合の信頼性を向上させることができる接合体、該接合体を用いることで小面積化が可能な半導体装置、該接合体でプリント配線板に接合される半導体装置を有するプリント回路板を提供する。

【解決手段】プリント回路板100は、半導体素子1が実装され、片面に電極パッド8が形成されたインターポーザ2と、インターポーザ2に対向する片面に電極パッド9が形成されたプリント配線板3と、電極パッド8,9を接合する接合体70と、を備えている。接合体70は、はんだ層60と、電極パッド8,9に接合された金属層50,50と、を有している。各金属層50,50は、金属粒子同士が結合して形成された金属粒子集合体10と、金属粒子集合体10の隙間に埋められたはんだ11とからなる。

(もっと読む)

61 - 70 / 4,054

[ Back to top ]