国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

3,771 - 3,780 / 3,785

半導体装置

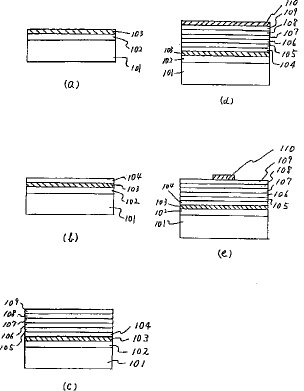

【目的】上下のPt電極の間にPZT薄膜が挟まれた構造を持つPZT薄膜の製造方法に於いて、アニール後のPb含有量をPZT薄膜の深さ方向にほぼ一様とし、良好な強誘電体特性を得る。

【構成】アニール前、PZT前駆体薄膜は104から109の6層で形成されており、PZT前駆体薄膜のPb含有量が、下部電極103側のPZT前駆体薄膜104から表面側すなわち上部電極110側に行くにつれ増加している。アニール後のPb含有量の深さ方向分布はほぼ一様となる。

【効果】不揮発性メモリや、光スイッチ、キャパシタ、赤外線センサ、超音波センサ、薄膜圧電振動子として利用できる

(もっと読む)

メモリモジュールおよびメモリシステム

【課題】 メモリチップを効率よく冷却することができるメモリモジュールおよびメモリシステムを提供すること。

【解決手段】 メモリモジュール10のSO−DIMM基板11との実装面にはメモリモジュール10の短辺とほぼ平行に複数の溝14が形成され、これらの溝14にはメモリ用ベアチップ1から発生した熱をメモリシステム20全体に拡散するための放熱部材15が取り付けられている。メモリ用ベアチップ1から発生した熱は、放熱部材15によってメモリシステム20全体に拡散されるので、放熱面積が拡大する。これによって外部への放熱の効率を上げることができ、メモリ用ベアチップ1の温度上昇を抑制することができる。

(もっと読む)

強誘電体メモリ素子及びその製造方法

強誘電体薄膜キャパシタをメモリキャパシタとして用いる強誘電体メモリ素子において、上部保護電極、上部電極8上の劣化防止層、強誘電体層7/電極6、8の界面劣化防止層の一つあるいは複数を設置し、あるいは強誘電体層7/上部電極8界面の変性層を低減する工程を設置することにより、強誘電体特性劣化の小さい強誘電体薄膜キャパシタを供給し、超寿命の強誘電体メモリ素子を実現する。

【効果】膜疲労及び刷り込みの生じにくい長寿命の強誘電体薄膜キャパシタを提供する。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、LOC構造を有する半導体メモリ製品の製造において、電気的特性を悪化させることなく、接着テープの浮きを防いで、信頼性を向上できるようにすることを最も主要な特徴とする。

【解決手段】たとえば、リード14の一部を櫛歯状に分岐させることによって、ダミーリード15bが形成されてなるリードフレーム13を用意する。そして、そのリード14よりダミーリード15bを切離させた後、このリードフレーム13を、接着テープ12を介して半導体チップ11の表面に接着する。これにより、ビット構成が異なる半導体チップ11を、ピン数の違うパッケージ17内にそれぞれに収納する場合にも、ダミーリード15bによるキャパシタンスのアンバランスを抑えつつ、本来はリードが存在しない部分での接着テープ12の浮きを防ぐことが可能な構成となっている。

(もっと読む)

強誘電体メモリ装置

【課題】 微細なサイズの強誘電体容量に低電圧を印加した際の分極特性を改善し、低電圧での動作を可能とし、かつ歩留りのよい高集積な強誘電体メモリ装置を提供する。

【解決手段】 メモリ内容を記憶させる前段階において、メモリ動作時に強誘電体容量Cに印加される通常の電圧VCCよりも高い電圧Vex(Vex>VCC)をあらかじめ強誘電体容量Cに印加する。強誘電体容量Cに高電圧Vexを印加することにより、強誘電体容量Cのドメインを再配列することができる。そのため、サイズの縮小による強誘電体容量Cの欠陥の増加等により分極反転を阻害されたドメインが、再配列により分極反転が可能となる。このような作用により小さいサイズの強誘電体容量における低電圧印加時の分極特性が改善される。この分極特性を改善した後、メモリ内容を書き込んでメモリ装置として使用する。

(もっと読む)

強誘電体メモリ装置

発振回路

【目的】ゲートアレイに内蔵される圧電素子を用いる発振回路において、そのレイアウト面積を増大させることなく、ノイズを除去することができる発振回路の提供。

【構成】ゲートアレイに内蔵される圧電素子を用いる発振回路であって、出力端に前記ゲートアレイの内部セル領域に存在する未使用ポリシリコンゲートを用いて構成されるローパスフィルタを備えることにより、上記目的を達成する。

(もっと読む)

半導体装置の製造方法

【目的】ドライエッチングにより形成された白金や導電性酸化物の微細パターンの表面の炭素及びハロゲン元素等による汚染除去することにある。

【構成】白金や導電性酸化物の電極を選択的にハロゲン元素を含むガスを用いたプラズマを応用したドライエッチングによりエッチングして微細パターン形成後、引き続き酸素ガス、オゾンガス、水蒸気ガス、窒素酸化物ガスのうち少なくとも一種類以上のガスを選択し、プラズマにより前記材料の表面を処理する。

(もっと読む)

半導体記憶装置

【目的】強誘電体キャパシタの絶縁膜に対してスクリーニングを行う場合に、スクリーニング時間の短縮、スクリーニングコストの低減を図り得る強誘電体メモリを提供する。

【構成】通常動作モードおよびスクリーニングモードを有する強誘電体メモリにおいて、スクリーニングモード時に通常動作モード時に選択されるメモリセルMCより多数のメモリセルを同時に選択し、その強誘電体キャパシタCの絶縁膜の両端間に極性が交互に反転するパルス電圧を任意の回数印加するスクリーニング回路(21、22、23)を具備することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【目的】 多数の回路を内臓した半導体装置を小型化,高機能化,低消費電力化し、かつその製造工程を簡略化する。

【構成】 相異なる機能を有する複数の回路、例えば抵抗素子,容量素子等を含むアナログ回路と、DRAMとを同一のシリコン基板1上に形成し、この複数の回路の主要部を同時に形成された共通層で構成する。例えば、容量素子の容量下部電極131と、DRAMセルのストレージノード205とを、第3層ポリシリコン膜とアモルファスシリコン膜との2層膜で構成し、この2層膜を同時に堆積する。また、各部の容量絶縁膜132,206を同時に堆積されたシリコン窒化膜で、容量上部電極133,プレート電極207を同時に堆積されたポリシリコン膜でそれぞれ構成する。特に、DRAMの製造プロセスに他の回路の製造プロセスを適合させることで、工程が円滑に行われる。

(もっと読む)

3,771 - 3,780 / 3,785

[ Back to top ]