国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

3,731 - 3,740 / 3,785

ソース、ドレイン、及びゲートを有する電気機械的ナノチューブトンネル装置

本発明は、長手方向及び横方向の延長部を有するナノチューブと、ナノチューブの少なくとも第1部分を支持する構造と、その横方向の延長部によって定義されている第1方向においてナノチューブに対して力を作用させる第1手段と、を有するナノチューブ装置(100)に関するものである。ナノチューブの少なくとも第2部分は、力が一定のレベルを超過した際に、ナノチューブの第2部分がその横方向の延長部の方向において曲がり、これによって第1電気回路を閉じるように、構造の支持部を超えて突出している。好適には、力をナノチューブに対して作用させる第1手段は、電気的な手段であり、この力は、電圧をこの手段に印加することによって生成される。本装置は、ソース及びドレイン電極の両方において量子力学トンネル現象を実現する。  (もっと読む)

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

分割チャネルアンチヒューズアレイ構造

一般に、本発明は、不揮発性で、ワンタイム・プログラマブル(OTP)メモリーアレイ用途に用いられることが可能な可変厚さゲート酸化膜アンチヒューズトランジスタ装置を提供する。このアンチヒューズトランジスタは、標準CMOS技術で製造されることができ、ソース拡散、ゲート酸化膜、ポリシリコンゲート、及びオプショナルなドレーン拡散を有する標準トランジスタ素子として構成されている。ポリシリコンゲートの下の可変ゲート酸化膜は、厚いゲート酸化膜領域及び薄いゲート酸化膜領域から構成され、薄いゲート酸化膜領域は局所的破壊電圧ゾーンとして作動する。ポリシリコンゲートとチャネル領域との間の導電性チャネルは、プログラム操作の間、局所的破壊電圧ゾーンに形成されることができる。メモリーアレイ用途においては、ポリシリコンゲートに印加されたワードライン読み取り電流は、アンチヒューズトランジスタのチャネルを介してソース拡散に結合されたビットラインによって検出されることができる。さらに具体的には、本発明は、OTPメモリーに好適なアンチヒューズセルとして、分割チャネルMOS構造を利用する効率的な方法を提供する。

(もっと読む)

(もっと読む)

メモリエレメント配列を相互に接続するポリマー誘電体

ポリマー誘電体(103)を含む半導体デバイス(100)および有機半導体材料(112)と受動層(114)とを含む少なくとも1つのアクティブデバイス(104)が開示されている。導電性ポリマー(106および/または108)をさらに含む半導体デバイス(100)も開示されている。そのようなデバイスは、軽量であること、及び強固な信頼性により特徴づけられる。  (もっと読む)

(もっと読む)

可変抵抗を有するメモリデバイス

薄膜記憶デバイスは、第1電極(3)と、第1の可変抵抗薄膜(2)と、第2の電極(1)とを備える。第1の電極(3)は、基板(4)の表面上に形成される。第1の可変抵抗薄膜(2)は、第1の電極(3)の表面上に形成される。第2の電極(1)は、第1の可変抵抗薄膜(2)の表面上に形成される。第1の可変抵抗薄膜(2)は、格子歪みおよび電荷配列のうち少なくとも1つによってバルク状態における抵抗値が変化する材料を含む。 (もっと読む)

中性子変換層組み込み型半導体基板

【解決手段】シングル中性子イベントの測定を可能にするのに十分な感度のある中性子変換層を組み込んだ半導体基板。前記基板は、アクティブ半導体素子層と、ベース基板と、前記アクティブ半導体素子層と前記ベース基板との間に提供される絶縁層と、前記アクティブ半導体素子層と前記ベース基板との間に提供される中性子変換層を含む。前記中性子変換層は、前記絶縁層内に位置し、且つ同絶縁層と前記ベース基板との間、若しくは前記アクティブ半導体素子層と同絶縁層との間に位置する。前記中性子変換層と前記アクティブ半導体素子層との間、および前記中性子変換層と前記ベース基板との間の少なくとも1つの間に障壁層が提供され、前記中性子変換層中に提供される中性子変換材料の拡散を防ぐ。さらに、前記アクティブ半導体素子層に複数の溝を形成する場合がある。 (もっと読む)

ホット・キャリアでプログラムされるワン・タイム・プログラマブル(OTP)メモリのための方法および装置

ホット・キャリア誘導劣化を使用して1つまたは複数のトランジスタ特性を変更してプログラムされるワン・タイム・プログラマブル・メモリ・デバイスが開示されている。ワン・タイム・プログラマブル・メモリ・デバイスは、トランジスタのアレイから構成される。このアレイ中のトランジスタは、これらのトランジスタの飽和電流、しきい値電圧またはこれらの両方に対する変化など1つまたは複数のトランジスタ特性のホット・キャリアにより引き起こされる変化を使用して選択的にプログラムされる。これらのトランジスタ特性に対する変更は、知られているホット・キャリア・トランジスタ・エージング原理と同様にして達成される。これらの開示されたワン・タイム・プログラマブル・メモリ・デバイスは、小型であり、低電圧および小電流でプログラム可能である。

(もっと読む)

(もっと読む)

アレイ状に配置された垂直型カーボン・ナノチューブ電界効果トランジスタを製造する方法、並びに、それによって形成された電界効果トランジスタ及びアレイ

【課題】 カーボン・ナノチューブ電界効果トランジスタと、カーボン・ナノチューブ電界効果トランジスタのアレイと、デバイス構造体とを製造するための方法、及び、該方法によって形成されたデバイス構造体のアレイを提供する。

【解決手段】 本方法は、ゲート電極層と、各々がソース/ドレイン・コンタクトと電気的に結合された触媒パッドとを含む積層構造体を形成することを含む。ゲート電極層は多数のゲート電極に分割され、少なくとも1つの半導体カーボン・ナノチューブが、化学気相堆積プロセスによって触媒パッドの各々の上に合成される。完成したデバイス構造体は、ゲート誘電体によって覆われた側壁を有するゲート電極と、該ゲート電極の該側壁に隣接する少なくとも1つの半導体カーボン・ナノチューブとを含む。ソース/ドレイン・コンタクトを半導体カーボン・ナノチューブの両端と電気的に結合することによって、デバイス構造体が完成する。多数のデバイス構造体は、メモリ回路又は論理回路のいずれかとして構成することができる。

(もっと読む)

半導体装置

相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させること。

読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

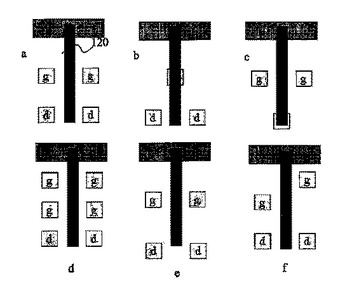

単一ポリ・2−トランジスタベースのヒューズ素子

ポリシリコンの単一層内に配置されたダブルゲート構造を有した、電気的にプログラム可能なトランジスタヒューズ(200)。このトランジスタヒューズ(200)では、第1のゲート(216)は、ソース領域(210)の一部と重なり合うように配置されていて、第2のゲート(215)は、第1のゲート(216)からは絶縁されていると共に、ドレイン領域(211)の一部と重なり合うように配置されている。第1のゲート(216)は、外部から供給されたコントロール信号を入力するための端子を有しており、第2のゲート(215)は、ドレイン領域(211)に容量結合されている。第2のゲート(215)は、第2のゲート(215)の容量結合を大きくするための結合装置(220)と、ヒューズプログラミング電圧を低くするためのドレイン領域(211)とを含んでいる。  (もっと読む)

(もっと読む)

3,731 - 3,740 / 3,785

[ Back to top ]