国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

3,761 - 3,770 / 3,785

1T‐nメモリセル積層構造体

本発明は、クロスポイントと1T‐1セルとの双方の設計に基づくある種の利点を導入するためのメモリ技術及びメモリアレイに関する新規な変更に関する。これらの設計のある特徴を組み合わせることにより、1T‐1セル設計における読出し時間の高速化及び信号対雑音比の増大と、クロスポイント設計における高記録密度化との双方が達成される。そのために、単一のアクセストランジスタ16を用いて、“Z”軸方向に配置された複数のメモリアレイ層で垂直方向に互いに上下に積み重ねうる多重メモリセルを読出すようにする。  (もっと読む)

(もっと読む)

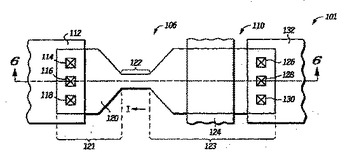

フューズ及びその形成方法

アクティブフューズはアクティブフューズ構造(120)を備え、この構造を使用して可変抵抗体(106)及び選択トランジスタ(110)の双方を形成する。一の実施形態では、アクティブフューズ構造は、半導体基板(140)の活性領域(160)の一部に形成され、選択ゲート(124)はアクティブフューズ構造の一方の端部(123)の上に配置されてアクティブフューズへの書き込みに使用する一体型選択トランジスタ(110)を形成する。共有型のアクティブフューズ構造を活性領域の内部に使用することによって、面積要件を縮小し、かつ検出マージンを大きくすることができる。  (もっと読む)

(もっと読む)

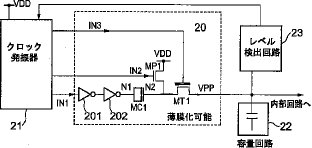

昇圧電位発生回路及び制御方法

【課題】 半導体メモリにおいて、外部電源電圧が低下しても、半導体メモリ内部では、高速動作を可能にすると共に、小型化をも可能にする昇圧電位発生回路を提供する。

【解決手段】 容量MOSトランジスタとトランスファMOSトランジスタとを備え、メモリセルを含むDRAMに使用される昇圧電位発生回路において、容量MOSトランジスタのゲート絶縁膜を、メモリセルを構成するMOSトランジスタのゲート絶縁膜の膜厚よりも薄い膜厚にすることにより、小面積で大容量の昇圧電位発生回路を実現する。この場合、トランスファMOSトランジスタのゲート絶縁膜の厚さを容量MOSトランジスタのゲート絶縁膜の厚さを同等以上に厚くすることが好ましい。

(もっと読む)

強誘電体膜を有する半導体装置の製造方法

【課題】強誘電体膜をエッチングする際に生じる反応副生成物を形成される素子に悪影響を与えることなく除去する。

【解決手段】強誘電体膜をエッチングしたあと、燐酸水溶液を用いてウェット処理をする。レジストをマスクとして強誘電体膜をエッチングしたあと、レジストアッシング後またはアッシング前後の両方に燐酸水溶液を用いてウェット処理をする。

(もっと読む)

半導体装置およびその製造方法

【課題】 強誘電体キャパシタに保護膜を設け、強誘電体膜の還元を抑制する。

【解決手段】 前記保護膜としてAl2 O3 膜を、3.0〜3.1g/cm3 、あるいはそれ以上の密度に形成する。

(もっと読む)

半導体装置の製造装置および製造方法

【課題】 加水分解性の液体材料が大気と接触するのを確実に防止できる液体自動供給システムを提供する。

【解決手段】 このCVD装置50は、処理室51にペンタエトキシタンタル(PET)を供給するための容器53に予備容器73を接続し、容器53内のペンタエトキシタンタル(PET)の残量が少なくなったときは、配管54と容器53とを切り離して新しい容器53と交換するのではなく、予備容器73からペンタエトキシタンタル(PET)を補充する。これにより、配管54と容器53とを切り離すためのジョイント61jを通じて配管54内に大気が侵入し、配管54内の残留ペンタエトキシタンタル(PET)が加水分解されて酸化タンタルが生成することはない。

(もっと読む)

半導体装置及びその製造方法

【課題】 実効的な素子特性を向上させ、または素子領域の基板表面が露出することを防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板101の表面上にシリコン酸化膜102を形成し、この表面上に埋め込み酸化膜の平坦化ストッパー材となるシリコン窒化膜103を形成する。半導体基板101にトレンチ105を形成した後、シリコン酸化膜102の側面にエッチングを行って後退させる。半導体基板101の露出している表面に酸化を行って素子領域の表面に丸みを付ける。これにより、素子領域の実効寸法を実寸法よりも大きくすることができる。

(もっと読む)

半導体記憶装置

【課題】チップサイズを増大させることなく特性の向上を図ることができる半導体記憶装置を提供する。

【解決手段】本発明の半導体記憶装置は、メモリセル領域50と周辺回路領域との間に配置されたセル形状の書込動作補助回路2を有し、書込動作補助回路2は、書込開始時にデジット線のディスチャージ動作を行い、書込終了時にデジット線のプリチャージ動作を行う第1の回路4と、デジット線のディスチャージ動作及びデジット線のプリチャージ動作の切替を行う第2の回路5とを有する。

(もっと読む)

半導体装置、その製造方法、及びそれを用いた応用システム

【課題】被覆性が良く、界面が安定な強誘電体薄膜を形成できる半導体装置の製造方法を提供する。

【解決手段】強誘電体薄膜を誘電体として用いたコンデンサと能動素子を電気回路的に組み合わせて構成される半導体装置の製造方法において、その強誘電体がゾル−ゲル法で作成される半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法、強誘電体キャパシタ、およびその製造方法

【課題】 強誘電体キャパシタを有する半導体装置の製造において、強誘電体膜の自発分極を最大化する。

【解決手段】 下側電極を形成後、強誘電体膜を堆積する前に、前記下側電極を不活性雰囲気中において急速熱処理する。

(もっと読む)

3,761 - 3,770 / 3,785

[ Back to top ]