国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

3,741 - 3,750 / 3,785

記憶素子、メモリ回路、半導体集積回路

【解決手段】第1の可変抵抗(5)は、第1の端子(7)と第3の端子(9)との間に接続され、第1の端子(7)と第3の端子(9)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第2の可変抵抗(6)は、第3の端子(9)と第2の端子(8)との間に接続され、第3の端子(9)と第2の端子(8)との間に印加されるパルス電圧の極性に応じてその抵抗値を増加/減少させる。第1の端子(7)と第3の端子(9)との間および第3の端子(9)と第2の端子(8)との間に所定のパルス電圧を印加して第1および第2の可変抵抗(5,6)の抵抗値を可逆的に変化させることにより1ビットあるいは多ビットの情報を記録する。 (もっと読む)

可塑的に変形可能な不可逆的ストレージ媒体と、このような一媒体を製造する方法

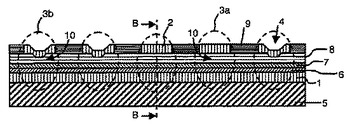

本発明は、第1の導体(1)および第2の導体(2)によってアドレス指定されることが可能なメモリ・セル(3)のアレイを備えるストレージ媒体に関する。各メモリ・セル(3)は、最初には電気的に絶縁しており、これらの第1の関連する導体(1)と、第2の関連する導体(2)とを選択的に接続するなど、局在化された可塑性変形(4)により導電性にされることが可能なアクティブ層(8)の1つのゾーン(10)を備える。本発明によれば、メモリ・セル(3)に記憶されるバイナリ情報は、アクティブ層(8)の対応するゾーン(10)の導電状態によって決定される。アクティブ層(8)は、帯電された(charged)レジンを使用して形成されてもよい。この媒体製造方法は、以降のステップ、すなわちこの初期の絶縁状態にある、アクティブ層(8)を有するブランク・ストレージ媒体のアセンブリと、記憶されるべき情報に対応するスタンピング・パターンを有するスタンピング・ダイの製造と、このスタンピング・ダイを使用したこのストレージ媒体のスタンピングとを含んでいる。  (もっと読む)

(もっと読む)

集積回路メモリーセル及びその製法

【課題】セルデザインや工程を不必要に複雑化せずにセルサイズを減少させる。

【解決手段】

チャンネル30は、組み合わされた第1電極と第1ソース/ドレーンの半導電性上方延長部を含むことができる。メモリーセルは複数のメモリーセルのアレイを含んでおり、第2電極は複数の電極の中の共通電極である。メモリーセルは、第1電極とデジット線との間に直線導電通路を提供することができ、その通路は垂直トランジスターを通過して延びている。

(もっと読む)

ノード・キャパシタンスを増加した半導体メモリ・デバイス

【課題】 ノード・キャパシタンスを増加した半導体メモリ・デバイスを提供することにある。

【解決手段】 集積回路半導体メモリ・デバイス(100)は、ゲートから基板へのキャパシタンスを増加し、それにより、ソフト・エラー率を低減するために、ストレージ・トランジスタのゲートの下に基板(112)の一部分(130)には存在しないBOX層として特徴付けられた第1の誘電体層(116)を有する。第1の誘電体層とは異なる特性を有する第2の誘電体層(132)は、基板のその部分(130)を少なくとも部分的に覆う。このデバイスは、フィン(122)と、ゲートとフィンとの間のゲート誘電体層(124、126)とを含むFinFETデバイスにすることができ、第2の誘電体層はゲート誘電体層より漏れが少ない。

(もっと読む)

他の種類の回路と共に集積されたMRAM装置

磁気抵抗ランダムアクセスメモリ(MRAM)(13)が、他の回路種(12)と共に埋め込まれている。演算装置のようなロジック(12)が、MRAM(13)と共に埋め込むのに特に適した回路種である。埋め込みを効率的に行うには、金属層(26)を他の回路(12)の相互接続部の一部として用い、更にMRAMセル(13)の一部として用いる。MRAMセル(13)は全て、プログラム線によって書き込まれる。プログラム線は、2本の線であり、交差して書き込むセルを規定する。このように、金属線(26)の共通使用があり、MRAMのプログラム線の一方に用いられ、更にロジック(12)の相互接続線の一方に用いられるので、設計が簡略化される。  (もっと読む)

(もっと読む)

スイッチング素子

スイッチングの再現性が高く、かつ、オン状態での高い電流値が得られるスイッチング素子を提供する。

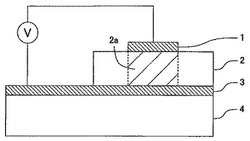

このスイッチング素子は、印加される電圧に対して2種類の安定な抵抗値を持つ双安定材料層30が、第1電極層20aと第2電極層20bとの間に薄膜として配置され、双安定材料層30がフラーレン類からなり、電極のうち少なくとも一方が金を含有する電極である。フラーレン類はC60及び/又はC70であることが好ましく、双安定材料層30の厚さが10オングストローム〜100μmであることがより好ましい。

(もっと読む)

スイッチング素子

転移確率を高くしてスイッチング特性を安定化した、双安定特性を持つスイッチング素子を提供する。

少なくとも2つの電極間に、印加される電圧に対して2種類の安定な抵抗値を持つ有機双安定化合物を含む有機双安定材料層30を配置してなるスイッチング素子であって、基板10上に、第1電極層20a、電荷注入抑制層40、有機双安定材料層30、第2電極層20bの順に薄膜として形成され、電荷注入抑制層40が、第1電極層20aから有機双安定材料層30への電荷注入量を、電荷注入抑制層40を設けずに第1電極層20aから有機双安定材料層30へ直接電荷注入する場合に比べて小さくする導電層からなる。

(もっと読む)

2構成要素整流接合メモリ素子

本発明の実施形態は、低コストで頑強な信頼性のあるWORMメモリにおいて使用される複雑さが低度で、効率的な2構成要素メモリ要素を対象とする。一実施形態のメモリ要素は、ドープ無機半導体層に接合された有機ポリマー層を備える有機オン無機ヘテロ接合ダイオードである。有機ポリマー層は、2層半導体ベース・ダイオードの1層、ならびにヒューズの両方として作用する。WRITE電圧パルスについて閾値時間間隔より長い期間、閾値WRITE電圧より大きい電圧を印加することにより、有機ポリマー層の抵抗率は不可逆的かつ劇的に増大する。本発明の一実施形態を示すメモリ要素は、以前に記述された別々のヒューズおよびダイオード・メモリ要素より容易に製造され、以前に記述されたメモリ要素より小さい電圧において、かつ著しく短い持続時間のWRITE電圧パルスで、切替え可能である望ましい特性を有する。 (もっと読む)

極薄シリコンにおけるNROM型フラッシュメモリデバイス

【課題】SOI技術を取り入れたCMOSデバイスにおける浮遊ボディの影響を抑制可能とする。

【解決手段】極薄シリコン・オン・インシュレータ構造においてNROMフラッシュメモリセルを実現する。平面型デバイスでは、ソース/ドレイン領域間のチャネルが通常時に完全空乏化されている。ソース/ドレイン領域と上方のゲート絶縁層との間に酸化物層を形成することで絶縁層を設ける。制御ゲートがゲート絶縁層の上部に形成される。縦型デバイスでは、ソース/ドレイン領域に側面が接する酸化物柱状体を基板から延伸させる。エピタキシャル再成長により、酸化物柱状体の側面に沿って極薄シリコンボディ領域が形成される。本構造の上部には、第2のソース/ドレイン領域が形成される。さらにその上部にゲート絶縁層及び制御ゲートが形成される。

(もっと読む)

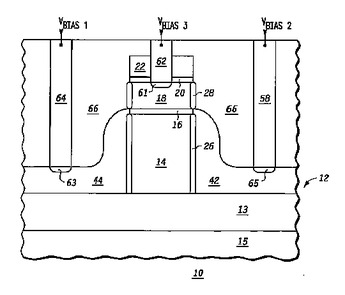

3つの電気絶縁電極を有するトランジスタ及びトランジスタの形成方法

トランジスタ(10)は別々に制御することができるゲート(44,42,18)を有するように形成される。3つのゲート領域は異なる電位でバイアスすることができ、かつこれらのゲート領域は異なる伝導特性を持つことができる。チャネルサイドウォール上の誘電体はチャネル上部の上の誘電体と異ならせることができる。ソース、ドレイン、及び3つのゲートとの電気コンタクトは別々に取る。ナノクラスター(143,144)のような電荷蓄積層をトランジスタのチャネルに隣接するように設け、そして電荷蓄積層を3つのゲート領域を通して制御することにより、揮発性メモリセル及び不揮発性メモリセルの両方を同じプロセスを使用して実現することにより世界共通のメモリプロセスを提供する。揮発性セルとして用いる場合、トランジスタの高さ、及びチャネルサイドウォール誘電体の特性によって記憶保持特性を制御する。不揮発性セルとして用いる場合、トランジスタの幅、及びチャネルを覆う誘電体の特性によって記憶保持特性を制御する。  (もっと読む)

(もっと読む)

3,741 - 3,750 / 3,785

[ Back to top ]