国際特許分類[H01L27/10]の内容

電気 (1,674,590) | 基本的電気素子 (808,144) | 半導体装置,他に属さない電気的固体装置 (445,984) | 1つの共通基板内または上に形成された複数の半導体構成部品または他の固体構成部品からなる装置 (52,733) | 整流,発振,増幅またはスイッチングに特に適用される半導体構成部品を含むものであり,少なくとも1つの電位障壁または表面障壁を有するもの;少なくとも1つの電位障壁または表面障壁を有する集積化された受動回路素子を含むもの (38,321) | 基板が半導体本体であるもの (36,153) | 複数の個々の構成部品を反復した形で含むもの (15,853)

国際特許分類[H01L27/10]の下位に属する分類

バイポーラ構成部品を含むもの (10)

電界効果構成部品を含むもの (11,969)

マスタースライス集積回路 (89)

国際特許分類[H01L27/10]に分類される特許

3,751 - 3,760 / 3,785

ツェナー−ザップメモリ

本発明は、NPNトランジスタを通過する電流を駆動することにより、集積回路内に情報を電気的に、かつ永久的にプログラムするための集積回路に関する。この集積回路は、抵抗器を介して前記NPNトランジスタに接続された出力端、第1供給電圧に接続可能な供給ポイントおよび前記NPNトランジスタのプログラミングを制御するための制御入力端を有する第1電流供給回路を備える。更にこの集積回路は前記第1電流供給回路の供給ポイントに接続された出力端と、供給電圧に接続可能な供給ポイントと、前記NPNトランジスタのプログラミングを制御するための制御入力端を有する少なくとも1つの第2電流供給回路を備える。最後にこの集積回路は、前記NPNトランジスタをプログラムするのに必要な電圧を前記第1電流供給回路と少なくとも第2電流供給回路の両端に分割するよう設けられた第1電圧レベルコントローラを備える。  (もっと読む)

(もっと読む)

抵抗変化素子、その製造方法、その素子を含むメモリ、およびそのメモリの駆動方法

本発明は、低消費電力、高速メモリとして期待されているRRAMの駆動電圧を低くし、かつ同じ抵抗変化を実現するための電気パルスの幅のバラツキを抑制する。本発明は、第1電極と、第1電極の上に形成され、電気パルスを印加することにより抵抗が変化しうる層と、この層の上に形成された第2電極と、を含み、上記層がペロブスカイト構造を含み、上記層が、第1電極および第2電極から選ばれる少なくとも一方の電極との界面において、凹部および凸部から選ばれる少なくとも一方を有する抵抗変化素子、を提供する。 (もっと読む)

スイッチング素子

スイッチング素子のon状態における電流密度を大きくし、かつ、遷移電圧が高いスイッチング素子を提供する。

電極間に印加される電圧に対して2種類の安定な抵抗値を持つスイッチング素子において、基板10上に第1電極層21a、有機双安定材料層30、第2電極層21bの順に薄膜として形成され、有機双安定材料層30が、電子輸送性の有機双安定材料からなる主成分と、電子供与性化合物からなる添加成分とを含む。

(もっと読む)

縦型ナノトランジスタおよび該トランジスタの製造方法ならびにメモリ装置

本発明の課題は、機械的応力に対し良好な耐性をもち、その製造が公知の従来技術よりも煩雑でない縦型ナノトランジスタを提供することである。本発明によればこの課題は、以下の特徴を備えた縦型ナノトランジスタによって解決される。すなわちソースコンタクトと、ドレインコンタクトと、ゲート領域と、ソースコンタクトとドレインコンタクトの間に配置され半導体特性をもつ円筒状のチャネル領域が設けられており、この円筒状チャネル領域は絶縁性フレキシブル基板に埋め込まれており、この領域は、ゲート領域とチャネル領域上部が同軸構造を成すよう、フレキシブル基板上およびチャネル領域上部の金属層により形成されたゲート領域により取り囲まれている。さらにソースコンタクトと半導体特性をもつチャネル領域とドレインコンタクトは縦方向に配置されていて、ソースコンタクトとドレインコンタクトと半導体特性をもつチャネル領域に対向するゲート領域と、基板の上側および下側は電気的に絶縁性の部材を有している。メモリ装置は多数のこの種の縦型ナノトランジスタから成る。本発明はこの種のトランジスタの製造方法にも関する。  (もっと読む)

(もっと読む)

縦型ナノトランジスタおよび該トランジスタの製造方法ならびにメモリ装置

本発明の課題は、機械適応力に対する耐性が良好であり、公知の従来技術よりも製造が煩雑でない縦型ナノトランジスタを提供することである。本発明によればこの課題は、以下の特徴を備えた縦型ナノトランジスタによって解決される。すなわちソース領域と、ドレイン領域と、ゲート領域と、ソース領域とドレイン領域との間に配置され半導体特性をもつチャネル領域が設けられており、ゲート領域は金属シートにより形成されており、ゲート領域と半導体特性をもつチャネル領域により同軸構造が形成されるよう、この金属シートにトランジスタが埋め込まれていている。この場合、ソース領域と半導体特性をもつチャネル領域とドレイン領域は垂直方向に配置されており、ゲート領域は、ソース領域とドレイン領域と半導体特性をもつチャネル領域に対向して電気的絶縁部材を有している。さらに本発明はこの種のトランジスタの製造方法ならびにメモリ装置にも関する。  (もっと読む)

(もっと読む)

不揮発性メモリを電荷トラッピングするための改善された消去および読み取り手法

本発明は、不揮発性電荷トラッピング型メモリデバイスのアレイを動作させるための方法を述べる。方法は、アレイの実質的に全ての不揮発性メモリデバイスのブロック消去ステップの前に、アレイの実質的に全ての不揮発性メモリデバイスにブロック書き込みするステップを備える。本発明の利点は、これを行なうことにより、さらなる電荷トラッピング型不揮発性メモリデバイスを、基準セルとして使用できることであり、基準セルは、アレイ内のメモリセルのブロック書き込みおよびブロック消去によって書き込みおよび消去され、したがって、基準セルは、アレイ内のメモリセルと同一の繰り返し履歴を示す。この特性を用いて、読み取りパラメータを目盛りセルの経年変化に適応させることができる。また、対応するデバイスも、提供される。  (もっと読む)

(もっと読む)

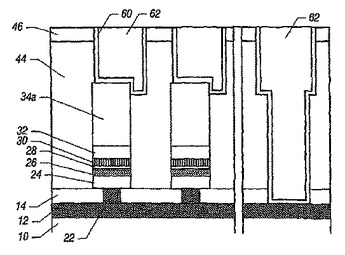

下地メモリ素子と接触するダマシン導線

ダマシン法を用いて、相変化メモリ内の底部導線に接続される電極が形成される。層変化メモリは、複数の分離されたメモリセルで構成されても良く、各メモリセルは、相変化メモリ閾値スイッチと、相変化メモリ記憶素子とを有する。  (もっと読む)

(もっと読む)

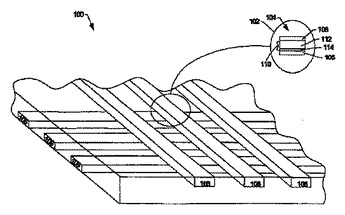

メモリデバイス及びこのデバイスの使用方法ないし製造方法

2つの電極(106、206、108、204)間に制御可能な導電媒体(110)を備える2つの電極で作られるメモリセル(104)を開示する。制御可能な導電媒体(110)は、活性低導電層(112)及び受動層(114)を備える。制御可能な導電媒体(110)は、電界の印加のような外部刺激が供給されると、インピーダンスか変わる。メモリデバイス/セルの作製方法、メモリデバイス/セルの使用方法、及び、メモリテバイス/セルを含むコンピュータのようなテバイスの使用方法も開示する。  (もっと読む)

(もっと読む)

三次元集積回路構造及びこれを作る方法

垂直方向の半導体装置は、電気装置そして/または相互接続を含む分離して作られた基板に付加される。多くの垂直方向の半導体装置は物理的に互いに分離され、そして同一半導体本体又は半導体基板内には配置されない。多くの垂直方向の半導体装置は取り付けられた後に個別のドープされたスタック構造を生成するため、エッチングされた数個のドーピングされた半導体領域を含む薄い層として分離して作られた基板へ付加される。あるいは多くの垂直方向の半導体装置が分離して作られた基板に取り付けるのに先立ち製作される。ドープされたスタック構造は、ダイオードキャパシタ、n‐MOSFET、p‐MOSFET、バイポーラトランジスタ、及び浮遊ゲートトランジスタのベースを形成する。強誘電体メモリー装置、強磁性体メモリー装置、カルコゲニド位相変更装置が分離して作られた基板と連結して使用するために、堆積可能なアッド‐オン層に形成される。堆積可能なアッド‐オン層は相互接続ラインを含む。

(もっと読む)

(もっと読む)

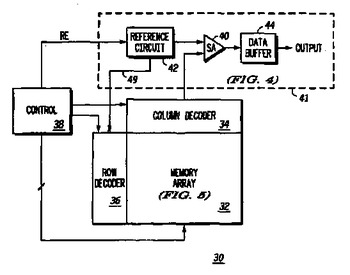

不揮発性メモリにおける基準トランジスタ用可変ゲート・バイアス

不揮発性メモリ(30)はナノクリスタルメモリセル(50、51、53)を備える。メモリセルトランジスタ(50、51、53)のプログラム及び消去閾値電圧は、プログラム/消去動作の回数の関数として上昇する。読み出し動作の間、基準トランジスタ(46)がセル電流と比較するための基準電流を供給する。基準トランジスタ(46)がナノクリスタルを含まないことを除いて、基準トランジスタ(46)は、メモリセルトランジスタ(50、51、53)を製造する際に用いるのと同様のプロセスで製造される。同様のプロセスを用いて基準トランジスタ(46)及びメモリセルトランジスタ(50、51、53)双方を製造することにより、基準トランジスタ(46)の閾値電圧は、メモリセルトランジスタ(50、51、53)の閾値電圧のずれに追従する。基準トランジスタ(46)のゲートにバイアスをかけるために、読み出し制御回路(42)が設けられている。読み出し制御回路(42)は、基準トランジスタ(46)のドレイン電流を検知し、基準電流をセル電流に対して実質的に一定値に維持するように、ゲートバイアス電圧を調節する。  (もっと読む)

(もっと読む)

3,751 - 3,760 / 3,785

[ Back to top ]