国際特許分類[H03C3/00]の内容

国際特許分類[H03C3/00]の下位に属する分類

細部 (11)

可変インピーダンスによるもの (6)

電子走行時間型電子管によるもの

電子管内での電子ビームの偏向によるもの

感光素子によるもの

振幅変調の角度変調への変換によるもの (7)

電気―機械素子によるもの (2)

国際特許分類[H03C3/00]に分類される特許

11 - 20 / 72

無線回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる無線回路、集積回路装置及び電子機器等を提供すること。

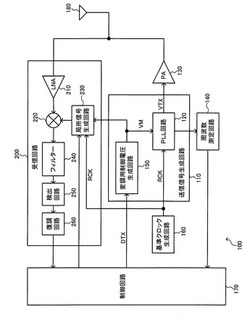

【解決手段】無線回路100は、電圧制御発振回路を有するPLL回路120を有し送信信号を生成して出力する送信信号生成回路110と、送信信号を増幅するパワーアンプ130と、周波数測定回路140とを含む。PLL回路120は、送信データ出力期間の前の期間ではクローズドループ動作に設定され、送信データ出力期間ではオープンループ動作に設定される。周波数測定回路140は、クローズドループ動作からオープンループ動作への切り換え時における送信信号の搬送波信号の周波数シフト量、及び送信データ出力期間における搬送波信号の周波数ドリフト量の少なくとも一方を測定する。

(もっと読む)

送信回路、集積回路装置及び電子機器

【課題】安定したデータ送信ができる送信回路、集積回路装置及び電子機器等を提供すること。

【解決手段】送信回路100は、電圧制御発振回路190を有し、搬送波の信号を生成するPLL回路110と、送信データDTXに基づいて、電圧制御発振回路190の変調用制御電圧信号入力ノードNBに対して、変調用制御電圧信号VMを出力する変調用制御電圧生成回路120と、電圧制御発振回路190の出力信号を増幅するパワーアンプ210とを含む。変調用制御電圧生成回路120は、送信データ出力期間の前の擬似信号出力期間に、擬似制御電圧信号を変調用制御電圧信号VMとして出力する。

(もっと読む)

通信装置及びその折り返し試験方法

【課題】SSCのジッタを抑制し、SSCの変調度を滑らかに遷移させることが可能なSSC生成機能を有するPLL回路及び通信装置を提供する。

【解決手段】SSCコントローラ18は、SSCの変調プロファイルに応じて予め定められたタイミングで位相シフト量を変更するよう位相補間器15を制御し、出力クロック信号C_OUTの変調度を周期的に変更させる。さらに、SSCコントローラ18は、帰還クロック信号C_FBの一周期内において位相補間器15より出力される位相シフト信号C_PSに与える総位相シフト量を、当該総位相シフト量と直前の一周期における総位相シフト量との差分が常に基本遅延量Δ以下となるよう制御する。ここで、基本遅延量Δは、出力クロック信号C_OUTの周期T_OUTを位相補間器15の位相分解能Nrで除算した値(つまり、T_OUT/Nr)である。

(もっと読む)

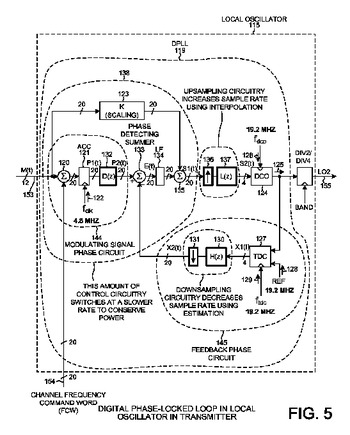

異なるサンプルレートで動作する部分を有するデジタル位相同期ループ

デジタル位相同期ループ(DPLL)は、DCO出力信号及び基準クロックを受信し及びデジタル値の第1のストリームを出力する時間−デジタル変換器(TDC)を含む。TDCを高レートでクロックすることによって量子化雑音が低減される。ダウンサンプリング回路は、第1のストリームを第2のストリームに変換する。第2のストリームは、DPLLの制御部が電力消費量を低減させるためにより低いレートで切り替わることができるようにDPLLの位相検出加算器に供給される。従って、DPLLは、マルチレートDPLLと呼ばれる。制御部によって出力されたデジタルチューニングワードの第3のストリームは、DCOをより高いレートでクロックし、それによってデジタルイメージを低減させることができるようにDCOに供給される前にアップサンプリングされる。受信機用途においては、アップサンプリングは行われず、DCOはより低いレートでクロックされ、それによって電力消費量をさらに低減させる。  (もっと読む)

(もっと読む)

広帯域位相変調器

位相変調のための装置は、参照信号から、各々が参照信号にロックされ、参照信号に関して他の位相シフト信号とは異なる位相シフトを有する複数の位相シフト信号を生成するように構成された遅延ロック・ループと、位相シフト信号のうちの1つを選択するように構成されたマルチプレクサとを含む。  (もっと読む)

(もっと読む)

変調回路の変調度調整方法

【課題】VCXOによって変調が行われる帯域の変調度と、VCOによって変調が行われる帯域の変調度とのバランス調整作業を改善すること。

【解決手段】本発明に係る変調回路の変調度調整方法では、

音声信号とトーン信号が合成された信号をVCXOとVCOの両方に入力して変調を行う変調回路であって、VCXOによる変調の変調度とVCOによる変調の変調度のバランスを調整する電子ボリュームを備えた変調回路の変調度調整方法において、

前記変調回路に、変調出力信号の変調度を計測する計測手段を接続し、

前記変調回路に、VCXOとVCOの通過帯域が重なる重複帯域の上端における周波数の正弦波を入力したときに前記計測手段にて計測される変調度と、前記重複帯域の下端における周波数の正弦波を入力したときに前記計測手段にて計測される変調度との差が、所定の範囲内に収まるように、前記電子ボリュームを調整する。

(もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

変調波生成装置

【課題】テレテキスト信号の位相歪みを軽減する。

【解決手段】デジタルデータのライジングエッジとフォーリングエッジを、周波数f1(f1=デジタルデータの伝送レート/2)の正弦波の立上り波形と立下り波形で夫々置換することにより変調波を生成する。具体的には、周波数f2(f2>f1)のクロック信号に同期して、Δθ(Δθ=360×f1/f2)を累積加算して第1の位相値を順次算出し、第1の位相値毎に、該第1の位相値に対応するレベルを選択する。選択に際して、第1の位相値が180度の整数倍を超えた時点を波形決定ポイントとして、各波形決定ポイントにおいて、該波形決定ポイントから、次の波形決定ポイントの直前までの間に、HIGHレベル、LOWレベル、上記立上り波形、立下り波形のいずれを選択するかを、デジタルデータの現在のビットと次のビットに応じて決定する。

(もっと読む)

2点FSK変調を用いる周波数シンセサイザのための自己較正方法

【課題】2点FSK変調を用いる周波数シンセサイザの自己較正方法の提供。

【解決手段】周波数シンセサイザ1が、第1の位相ロック・ループおよび高周波アクセス部を備え、高周波アクセス部は、電圧制御発振器の第2の入力に接続されたデジタル/アナログ変換器20を備える。較正動作のために、高周波アクセス部に、第1の位相ロック・ループ内の位相比較器3に接続された第2の電荷ポンプ14および第2のループ・フィルタ15を備える。第2の電荷ポンプ14が、オンに切り替えられると、第2の位相ロック・ループを形成する。デジタル/アナログ変換器20の利得を較正するために、決められた出力周波数に予めロックされた第2の位相ロック・ループの第2の電荷ポンプ14を切り離した後に、電圧比較器21が、デジタル/アナログ変換器20の出力電圧を、第2のループ・フィルタ内に蓄えられた電圧と比較する。

(もっと読む)

直交変調器

【課題】 2つの偶高調波ミクサを用いた直交変調器において、局部発振器と偶高調波ミクサの間を接続する低域通過フィルタの出力インピーダンスがほぼゼロとなり、2つのミクサ間のアイソレーションが極端に劣化するという問題が生じていた。

【解決手段】 抵抗とグラウンドの間にT型高域通過フィルタを接続し、π型の低域通過フィルタと2つの偶高調波ミクサの分岐接続部との間に1/4波長線路を付加することにより、π型の低域通過フィルタを使用しつつ、2つのミクサ間のアイソレーションを確保することができ、良好な変調精度を得ることができる。

(もっと読む)

11 - 20 / 72

[ Back to top ]