国際特許分類[H03K5/13]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 単一の出力をもち,かつ入力信号を変換して所望の時間間隔を有するパルスを与える配置 (668)

国際特許分類[H03K5/13]の下位に属する分類

時間参照信号,例.クロック信号の使用によるもの (174)

遅廷線の使用によるもの (118)

共振回路の使用によるもの

国際特許分類[H03K5/13]に分類される特許

11 - 20 / 376

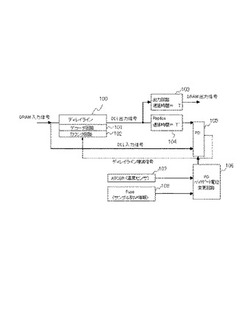

半導体装置

【課題】サンプル間、温度等の変位に伴い発生するロック位相の変動を補正し、ロック位相を一定とすることができるDLLを備えた半導体装置を提供する。

【解決手段】位相検出回路(PD)105を構成する複数のMOSFETのうち所定のMOSFETのバックゲート電位を変更するPDバックゲート電位変更回路106と、温度センサ107と、サンプル別閾値電圧(Vt)情報を記憶したFuse(ヒューズ)108を備える。温度センサ107の温度情報、Fuse(ヒューズ)108に記憶されたサンプル別閾値電圧(Vt)情報は、PDバックゲート電位変更回路106に読み出され、閾値電圧を制御し、ロック位相の変動を補正する。

(もっと読む)

遅延ロックループ/フェーズロックループにおける移相処理

【課題】

本開示は遅延ロックループ(DLL)及びフェーズロックループ(PLL)における移相処理に関する。

【解決手段】

DLLまたはPLLにおけるチャージポンプは、出力ノードに並列に接続されたキャパシタを備える。一次電流スイッチング回路は、ソース電流でキャパシタを充電し、シンク電流でキャパシタを放電する。補助ソース回路は、大きさの範囲を有する正の位相生成電流をソースする。正の移相生成電流の大きさは、少なくとも1つのソース選択信号により決定される。補助シンク回路は、大きさの範囲を有する負の移相生成電流をソースする。前記負の移相生成電流の大きさは、少なくとも1つのシンク選択信号により決定される。

(もっと読む)

半導体装置

【課題】出力クロック信号を生成して出力するまでに要する時間を短縮させる。

【解決手段】半導体装置は、第1のクロック信号のライズエッジ及び第2のクロック信号のライズエッジを合成して第1及び第2のクロック信号のライズエッジの間にライズエッジを有する第3のクロック信号を生成する第1の位相合成回路と、第1のクロック信号のフォールエッジ及び第2のクロック信号のフォールエッジを合成して第1及び第2のクロック信号のフォールエッジの間にフォールエッジを有する第4のクロック信号を生成する第2の位相合成回路と、第3のクロック信号のライズエッジを受けてライズ/フォールエッジの内の一方の位相を、第4のクロック信号のフォールエッジを受けてライズ/フォールエッジの内の他方の位相を其々調整した出力クロック信号を出力する第3の位相合成回路と、を備える。

(もっと読む)

遅延回路

【課題】遅延時間の精度を向上するとともに、回路面積の小型化を図る。

【解決手段】入力端子INを介して入力される入力信号に応じてオンオフするトランジスタ10と、トランジスタ10と電源端子VBの間に配置された抵抗20と、トランジスタ10と抵抗20の接続点の電位がハイレベルになるとオフするトランジスタ11と、トランジスタ11と接地端子VSS間に配置された抵抗21と、トランジスタ10と抵抗20の接続点の電圧を出力する出力端子OUTと、トランジスタ11と抵抗21の接続点にアノードが接続され、トランジスタ10と抵抗20の接続点にカソードが接続されたダイオード30と、を備えた。

(もっと読む)

相変化物質に基づくプログラマブル抵抗を用いた遅延発生器

【課題】 相変化物質に基づくプログラマブル抵抗を用いた遅延発生器を提供する。

【解決手段】 本発明は、カルコゲナイドに基づく相変化物質で作られる少なくとも1つのプログラマブル抵抗RPCM(11)を含み、前記抵抗RPCMが、遅延を発生させるために、抵抗RPCMの抵抗値が所定の初期値R0に等しく、そしてカルコゲナイドが非晶相であるようなやり方で初期化され、比較器(13、16、19)が、時間の経過に対して安定な基準電気量を、プログラマブル抵抗RPCM(11)の抵抗値を表わす可変電気量と比較し、比較器が特異信号sを発生させ、前記特異性が、その2つの電気量の間の差が符号を変えるときに生成される、遅延発生器に関する。

(もっと読む)

遅延回路およびシステム

【課題】 遅延段の数を切り換えるときの遅延時間の増加量および減少量を一定にすることで、高い精度を有する遅延回路を形成する。

【解決手段】 遅延回路は、直列に接続された複数の遅延段、検出回路および調整回路を有する。各遅延段は、前段からの信号を反転して後段に伝達する第1遅延素子と、後段からの信号を反転して前段に伝達し、または前段からの信号を反転した遅延信号を反転して前段に伝達する第2遅延素子とを含む。検出回路は、奇数段目および偶数段目の遅延段において、前段からの信号を受けてから遅延信号を経て第2遅延素子から信号が出力されるまでの伝搬遅延時間をそれぞれ検出する。調整回路は、検出回路の検出結果に基づいて、奇数段目および偶数段目の遅延段の伝搬遅延時間を互いに等しくする。

(もっと読む)

パルス発生回路

【課題】入力信号にジッタが含まれていても安定した時間幅のパルスを出力する。

【解決手段】パルス発生回路は、ゲートが入力端子2に接続され、ソースが電源電圧VDDに接続されたPMOSトランジスタQ1と、ゲートが入力端子2に接続され、ドレインがPMOSトランジスタQ1のドレインに接続され、ソースが出力端子3に接続されたNMOSトランジスタQ2と、一端が出力端子3に接続され、他端が接地電圧VSSに接続された負荷インピーダンスZout1とを有する。

(もっと読む)

遅延調整回路、遅延調整方法及び電子機器

【課題】分解能の高い遅延調整回路を提供する。

【解決手段】第1の素子と第2の素子とを有する第1の遅延調整部と、第3の素子を有する第2の遅延調整部と、前記第1の遅延調整部の出力又は前記第2の遅延調整部の出力を選択する出力選択部と、を含み、前記第2の素子の入力及び前記第3の素子の入力は前記第1の素子の出力であり、前記第1の遅延調整部の出力は前記第1の素子の出力及び前記第2の素子の出力であり、前記第2の遅延回路部の出力は前記第3の素子の出力であり、前記第3の素子は、第1の抵抗を介して第1の電源に接続されている第1の状態、及び、前記第1の抵抗を介して前記第1の電源に接続されていない第2の状態があることを特徴とする遅延調整回路。

(もっと読む)

可変遅延回路

【課題】 遅延時間の制御信号に対する線形性の高い可変遅延回路を提供する。

【解決手段】 遅延制御回路100は、インバータINV1およびINV3に与える電源電圧VDD1−VSS1の大きさを一定値VBに保ち、かつ、インバータINV2およびINV4に与える電源電圧VDD2−VSS2の大きさを同じ一定値VBに保った状態で、前者の電源電圧VDD1およびVSS1の各電位に対して後者の電源電圧VDD2およびVSS2の各電位を所望のシフト量ΔVだけ負方向にシフトさせる。この結果、シフト量ΔVとほぼ同じシフト量だけ、インバータINV1およびINV3の論理閾値に対して、インバータINV2およびINV4の論理閾値が負方向にシフトされる。そして、インバータINV1〜INV4からなる遅延回路の遅延時間に論理閾値のシフト量に比例した変化が発生する。

(もっと読む)

可変遅延回路

【課題】1段ごとの遅延時間変化の誤差が小さい高精度の可変遅延回路の実現。

【解決手段】直列に接続された複数個の遅延ユニット20-0,20-iを有し、各遅延ユニットは、第1から第3論理ゲートを有し、第1論理ゲートG1は、前段の出力が後段の一方の入力になるように直列に接続され、他方の入力には、折り返し位置を指示する第1制御データCTN0,CTNiが入力され、第2論理ゲートG2は、一方の入力が第1論理ゲートの入力に接続され、他方の入力には折り返し位置を指示する第2制御データCT0,CTiが入力され、第3論理ゲートSGは、後段の出力が前段の一方の入力になるように直列に接続され、他方の入力には第2論理ゲートの出力が入力され、第3論理ゲートにおいて、一方の入力M1から出力Zまでの経路の遅延時間と、他方の入力M2から前出力Zまでの経路の遅延時間は、等しい可変遅延回路。

(もっと読む)

11 - 20 / 376

[ Back to top ]