国際特許分類[H03K5/13]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 単一の出力をもち,かつ入力信号を変換して所望の時間間隔を有するパルスを与える配置 (668)

国際特許分類[H03K5/13]の下位に属する分類

時間参照信号,例.クロック信号の使用によるもの (174)

遅廷線の使用によるもの (118)

共振回路の使用によるもの

国際特許分類[H03K5/13]に分類される特許

61 - 70 / 376

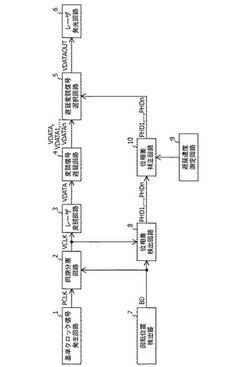

電子機器および画像形成装置

【課題】 画像形成装置などの電子機器において、電源電圧変動、温度変動などの要因で演算回路内の遅延回路による遅延量が動的に変動しても、後段の回路がその影響を受けないようにする。

【解決手段】 この電子機器は、遅延回路を含む演算回路8と、この遅延回路による信号遅延開始時における所定の遅延回路の第1信号進行速度、および演算回路8内の遅延回路による信号遅延開始後のあるタイミングにおける所定の遅延回路の第2信号進行速度を計測する遅延速度測定回路9と、遅延速度測定回路9により計測された第1信号進行速度および第2信号進行速度に基づいて、演算回路8による演算結果を補正する補正回路10とを備える。

(もっと読む)

半導体集積回路

【課題】複数の回路ブロックを有する半導体集積回路にて、電源ノイズにより発生するクロック信号におけるジッタを低減する。

【解決手段】第1の回路ブロックに供給される第1のクロック信号のクロックパスディレイを測定する遅延測定回路と、第2の回路ブロックの動作による電源電圧の変動時間を測定する時間測定回路と、第2の回路ブロックに供給される第2のクロック信号を遅延させる遅延調整回路と、第1のクロック信号と第2のクロック信号との位相差を測定する位相差測定回路と、遅延調整回路での遅延量を制御する位相制御回路とを備え、第2の回路ブロックの動作周波数が第1の回路ブロックの動作周波数より低い場合には、位相制御回路が、ジッタが最小となる電源ノイズと第1のクロック信号との設定位相差を算出し、位相差測定回路により測定した位相差が設定位相差になるように遅延量を制御する。

(もっと読む)

クロック生成装置、クロック生成方法およびデジタル放送受信装置

【課題】延回路を用いて低ジッタの周波数可変クロック生成システムを実現する。

【解決手段】クロック生成装置100は、CKinを遅延してCKoutを提供する遅延回路200,300と、稼動主遅延段選択部と、稼動補正遅延段選択部と、遅延制御部を具備する。遅延回路は、選択的に動作する複数の主遅延段D1〜Dnが縦続接続された主遅延部300および、この主遅延部に接続され選択的に動作する複数の補正遅延段C1〜Cmが縦続接続された補正遅延部(補正用ディレイ200)を含む。稼動主遅延段選択部は、主遅延段のうち遅延動作に用いられる稼動主遅延段を選択する。稼動補正遅延段選択部は、補正遅延段のうち遅延動作に用いられる稼動補正遅延段を選択する。遅延制御部(MPU120)は、稼動主遅延段を選択することでCKinに対するCKoutの遅延量を定め、稼動主遅延段の遅延値が均一化するように稼動補正遅延段を決定する。

(もっと読む)

遅延信号生成回路、及び、遅延回路

【課題】入力された信号に所定の遅延時間を安定的に挿入し得る遅延信号生成回路及び遅延回路を提供する。

【解決手段】遅延信号生成回路は、供給される電源の電圧によって、その遅延時間が変化する、1又は複数の第1遅延回路と、前記第1遅延回路と同一の回路構成を有しており、供給される電源の電圧によって、その遅延時間が変化する第2遅延回路と、前記第1遅延回路と前記第2遅延回路に電源を供給する、制御電源回路とを有する、電源供給回路と、を備えるとともに、前記制御電源回路は、入力クロック信号と遅延クロック信号との間の位相差を検出し、前記位相差に基づいて、前記入力クロック信号と前記遅延クロック信号との間の位相差が解消されるように、前記第1遅延回路と前記第2遅延回路に供給する電源の電圧を制御する。

(もっと読む)

遅延同期ループ回路およびインターフェース回路

【課題】外部クロック信号に対して所定の位相差を有する遅延クロック信号を精度良く生成することができるDLL回路を提供する。

【解決手段】DLL回路1は、制御部10と、第1および第2のノードND(0),ND(n)間に直列接続されたn個(nは2以上の整数)の遅延部D(1)〜D(n)とを含む。第1のノードND(0)には外部クロック信号CLKINが入力される。制御部10は、n個の遅延部D(1)〜D(n)のうち所定の2個の遅延部D(4),D(n)の出力信号CLKA,CLKBの位相差に応じた制御電圧VCを出力する。各遅延部Dは互いに同一の構成を有し、入力された信号に対して制御電圧VCに応じた遅延時間だけ遅延した信号を出力する遅延バッファIと、遅延バッファIの出力を電源電圧の振幅を有する矩形波に整形して出力する整形バッファJとを含む。遅延部D(4)〜D(n)の出力信号が遅延クロック信号として用いられる。

(もっと読む)

半導体集積回路装置

【課題】小さい面積で十分な遅延時間を確保する。

【解決手段】 入力に基づいて充電点に充電を行う第1のトランジスタと前記入力に基づいて放電点から放電を行う第2のトランジスタとにより構成される第1のインバータ(PT21,NT21)と、前記充電点と前記放電点との間に、ドレイン・ソース路が並列に設けられたP型の第3のトランジスタ及びN型の第4のトランジスタ(PT22,NT22)と、前記充電点又は前記放電点の電位を反転させて前記第3及び第4のトランジスタのゲートに供給して、前記充電点又は前記放電点から前記入力の遅延信号を得る第2のインバータ(INV21)とを具備したことを特徴とする。

(もっと読む)

クロックのデューティ・サイクルの自動制御

【課題】クロック信号の立ち下がりを調節して望ましいデューティ・サイクルを達成するデューティ・サイクル補正(DCC)回路を提供する。

【解決手段】幾つかの例では、DCC回路は、入力クロック信号の立ち下がりに応答してパルスを発生し、そのパルスを制御電圧に基づいて遅延し、遅延したパルスに基づいて入力クロック信号の立ち下がりを調節して出力クロック信号を生成し、出力クロック信号のデューティ・サイクルと望ましいデューティ・サイクルとの間の差に基づいて制御電圧を調節する。DCC回路は、望ましいデューティ・サイクルを達成するためにクロック・サイクルの立ち下がりを調節するので、クロック信号の立ち上がりを調節する既存のPLL制御ループへ、その動作に干渉することなく組み込むことができる。

(もっと読む)

遅延回路

【課題】PVT感度が自動的に緩和される遅延回路を提供する。

【解決手段】遅延回路100は、入力インバータ回路110と出力インバータ回路120との間にnMOSトランジスタ141、142からなる容量素子を備えている。入力インバータ回路110は、電源電位VDDと接地電位VSSとの間に抵抗R1を介して直列に接続されたpMOSトランジスタPM1とnMOSトランジスタNM1とを備えている。信号線130とnMOSトランジスタ141、142のゲートとの間にpMOSトランジスタ151、152が設けられている。この構成において、入力信号がLからHに変わる場合、遅延回路のPVT感度が自動的に緩和される。

(もっと読む)

遅延素子及び集積遅延素子

【課題】発振周波数に依らずに出力信号の電圧振幅を確保することができる遅延素子を提供すること。

【解決手段】本発明は、遅延回路1aと電流源回路2aとを備える。遅延回路2aは、NchトランジスタMN1〜8からなる。NchトランジスタMN1にはNchトランジスタMN3及びMN5が、NchトランジスタMN2にはNchトランジスタMN4及びMN7が接続される。NchトランジスタMN5とMN7とには、それぞれNchトランジスタMN6とMN8とが接続される。NchトランジスタMN3及び4は制御電圧VCにより制御される。NchトランジスタMN5のゲートは、出力ノードOUTBと接続される。NchトランジスタNM7のゲートは、出力ノードOUTと接続される。

(もっと読む)

クロック生成回路、電源供給システム及び遅延時間調整部

【課題】一方のクロック信号に対して他方のクロック信号の立ち上がりを遅延させる遅延時間を制御するため、例えば電波状況に応じて、輻射ノイズの低下を図るクロック生成回路、電源供給システム及び遅延時間調整部を提供すること。

【解決手段】コントロール部16は、ワンセグ受信機2から受信したBERデータDBに基づいて、ワンセグ受信機2のビットエラーレートを最も小さくするような、第1及び第2基準クロック信号Ck1,Ck2の周波数の設定周波数データDf、及び、第1基準クロック信号Ck1に対する第2基準クロック信号Ck2の立ち上がりの遅延時間の設定遅延時間データDtに設定し、その設定周波数データDf及び設定遅延時間データDtを基準クロック生成回路21に出力する。基準クロック生成回路21は、入力された設定周波数データDf及び設定遅延時間データDtに基づいて、第1及び第2基準クロック信号Ck1,Ck2を生成する。

(もっと読む)

61 - 70 / 376

[ Back to top ]