国際特許分類[H03K5/13]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | パルス技術 (16,231) | このサブクラス中の他のメイングループの1によっては包括されないパルス操作 (3,125) | 単一の出力をもち,かつ入力信号を変換して所望の時間間隔を有するパルスを与える配置 (668)

国際特許分類[H03K5/13]の下位に属する分類

時間参照信号,例.クロック信号の使用によるもの (174)

遅廷線の使用によるもの (118)

共振回路の使用によるもの

国際特許分類[H03K5/13]に分類される特許

41 - 50 / 376

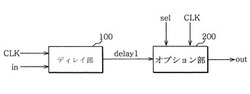

ディレイ回路及び信号遅延方法

【課題】 安定したディレイ時間を有するディレイ回路を提供する。また、面積を小さく占めるディレイ回路を提供する。

【解決手段】 クロック信号を受信して入力信号を順次所定時間の間隔で遅延させて複数の第1ディレイ信号を生成するディレイ部と、一つ以上の選択信号によって前記複数の第1ディレイ信号のうち一つを選択して第2ディレイ信号として出力するオプション部と、を含むディレイ回路を提供する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの確実な同期と再生クロックの適切なジッタ低減とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aは、外部から入力される駆動力制御信号に応じて駆動力が調整される駆動力調整機能付きバッファ増幅器である。

(もっと読む)

半導体装置

【課題】広い変動幅で入力信号を遅延させる一方、入力端に加えられるローディング及びその動作電流量を最小限に維持することができる遅延ラインを備える半導体装置を提供すること。

【解決手段】遅延制御コードONC_PUBに応じて、入力信号を遅延して第1の遅延入力信号及び第2の遅延入力信号を出力する共通遅延部200と、遅延制御コードCON_1に応じて、第1の遅延入力信号を遅延して第1の出力信号を出力する第1の遅延部220と、遅延制御コードCON_2に応じて、第2の遅延入力信号を遅延して第2の出力信号を出力する第2の遅延部240とを備え、共通遅延部から伝達される第1の遅延入力信号が第1の遅延部中を通過する長さである第1の遅延経路と、共通遅延部から伝達される第2の遅延入力信号が第2の遅延部中を通過する長さである第2の遅延経路とに、所定の長さの差があることを特徴とする。

(もっと読む)

デューティ補正回路、遅延同期ループ回路、カラムA/D変換器、固体撮像素子およびカメラシステム

【課題】デューティ比が50%より大きい場合も小さい場合も両方を一つの素子で対応が可能であり、素子数を削減できるだけではなく、スイッチング回数を削減することが可能で、消費電流を削減することができるデューティ補正回路、DLL回路、カラムA/D変換器、固体撮像素子、およびカメラシステムを提供する。

【解決手段】デューティ補正回路10は、第1入力および第2入力を有するC素子11と、C素子11の第2入力に接続されたインバータ12と、を有し、C素子11は、入力が両方とも論理“1”になると出力が論理“1”になり、入力が両方とも論理“0”になると出力が論理“0”になり、その他の状態では出力は前の状態を保持し、C素子11の第1入力およびインバータ12にそれぞれ互いに位相差がほぼ半周期の相補クロックが入力される。

(もっと読む)

電子回路

【課題】

内部電源回路からの内部電源電圧が安定状態となり、レベルシフタの入力が適正となった後に、レベルシフタを活性化させるパワーダウンモードの復帰シーケンスを備えた電子回路を提供する。

【解決手段】

電源電圧からシステム電圧を発生するシステム電圧発生回路10と、システム電圧を供給されて動作する内部回路30と、入出力回路24と、内部回路からの信号を入力し、電源電圧の電圧レベルに変換し入出力回路へ出力するレベルシフタ23と、レベルシフタを制御する制御回路40とを備え、システム電圧発生回路10が停止状態から動作状態へ移行するとき、制御回路は内部回路が動作状態であることを判定する第1の判定手段41と、システム電圧が所定値に達したか、または所定値に収束したかを判定する第2の判定手段42とを備え、双方の判定手段の結果に基づいてレベルシフタを活性化する構成とした。

(もっと読む)

遅延回路、及び電子機器

【課題】遅延回路のキャパシタの容量を増大させることなく、外来ノイズの影響による出力電圧の誤動作を防止する。

【解決手段】キャパシタと第1のノードを介して接続され、前記キャパシタを充電または放電する定電流源と、入力電圧が第1のレベルに変化したときに前記キャパシタを放電または充電し、入力電圧が第2のレベルに変化したときに前記キャパシタを充電または放電する充放電回路と、前記キャパシタの充放電の開始から、前記第1のノードの電圧が所定の検知電圧を超えるまでの時間遅延して、出力電圧のレベルを第1のレベルから第2のレベルに変化させる電圧検知回路とを有する遅延回路において、前記入力電圧が第2のレベルであって、かつ前記出力電圧が第2のレベルに変化したときに、前記第1のノードの電圧を前記検知電圧を超えるレベルに保持する電圧保持回路を備えることで出力電圧の誤動作を防止する。

(もっと読む)

遅延固定ループ及びその駆動方法

【課題】遅延固定にかかる時間を短縮し、遅延固定のための回路の電流消費を低減する遅延固定ループを提供すること。

【解決手段】特定パルス幅を有する遅延パルス(DPULSE)を生成する遅延パルス生成部(210)と、遅延パルスをコード化してコード値(CODE)を出力するコード化部(220)と、入力クロック(CLK)をコード値に該当する分だけ遅延させ、遅延された固定クロック(DLLCLK)を生成する遅延ライン(230)とを備える。遅延パルスが、入力クロックの整数倍に該当する第1の期間と特定レプリカ遅延期間である第2の期間との差に該当する第3の期間の間、ロジックハイレベル状態を有することを特徴とする。

(もっと読む)

遅延回路及び電圧制御発振回路

【課題】電源ノイズにより遅延時間が影響を受けにくい遅延回路及び遅延回路を用いた電圧制御発振回路を提供する。

【解決手段】第1及び第2の電源端子と一対の差動信号入力端子と一対の差動信号出力端子とを備え、一対の差動信号入力端子から入力した信号を遅延させて一対の差動信号出力端子から出力する遅延部と、電流制御端子により制御された電源電流を遅延部の第1の電源端子と第2の電源端子との間に流すように制御する電流制御部と、第1及び第2の電源端子の電圧が一定の電圧になるように制御する電圧制御部と、を備える。

(もっと読む)

半導体装置

【課題】 起動時に遅延回路部の遅延時間を調整する半導体装置を提供する。

【解決手段】 半導体装置は、電源立ち上げ動作時に遅延回路部の遅延時間を検出し、検出結果に基づいて遅延調整信号を生成する遅延制御部と、遅延回路部に設けられ、遅延調整信号に応じて遅延回路部の遅延時間を調整する遅延調整部とを備える。

(もっと読む)

半導体装置、半導体装置の制御方法及び該半導体装置を用いたシステム

【課題】電源電位変動に対する第1の遅延変動量を有するアナログ回路と、第1の遅延変動量より小さな第2の遅延変動量を有するデジタル回路とを備える半導体装置において、電源電位の変動に伴うアナログ回路とデジタル回路との間での遅延量のミスマッチを解消する。

【解決手段】アナログ回路は第1の電源電位に接続されている場合に、デジタル回路として、第1の電源電位に接続された第1の回路部分において発生した遅延量である第1の遅延量を検出する検出回路と、第1の電源電位よりも電位変動量が小さい第2の電源電位に接続され、アナログ回路を制御する制御信号を生成する第2の回路部分と、を設ける。第1の遅延量に相関させて第2の回路部分における遅延量である第2の遅延量を制御する。

(もっと読む)

41 - 50 / 376

[ Back to top ]