国際特許分類[H03L7/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

国際特許分類[H03L7/06]の下位に属する分類

いくつかのループを用いるもの,例.冗長クロック信号発生のためのもの

位相ロックループの細部 (2,372)

間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528)

国際特許分類[H03L7/06]に分類される特許

91 - 100 / 173

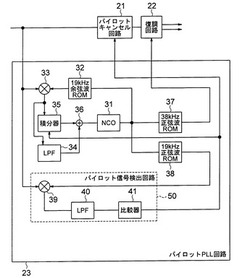

パイロットPLL回路及びFMステレオ復調回路

【課題】制御特性を向上させることが可能なパイロットPLL回路を提供することを目的とする。

【解決手段】制御データを与えられて出力周波数が変化するNCO31、出力周波数を与えられ第1の周波数の余弦波データを出力するROMテーブル32、FM復調データと第1の周波数の余弦波データとを与えられて乗算し乗算結果を出力する乗算器33、乗算結果を積分した累積加算データを出力する積分器35、乗算結果を与えられFM復調データと出力周波数との間の周波数偏差信号を出力するLPF34、累積加算データと周波数偏差信号とを加算して制御データを出力する加算器36、FM復調データのパイロット信号成分を検出してパイロット信号検出信号を出力するパイロット信号検出回路50を備え、積分器は累積加算データの値をパイロット信号検出信号に応じて制御する。

(もっと読む)

分周回路および分周方法

【課題】50%デューティ・サイクルを有するプログラマブル整数クロック分割の回路お

よび方法。

【解決手段】整数分割値により入力信号の周波数を分割する回路および方法。回路は一般

的に(a)入力信号を受信する第1の複数の直列接続された遅延要素および第1の設定可

能なフィードバック・ネットワークを含む第1周波数分割器、(b)入力信号の逆転を受

信する第2の複数の直列接続された遅延要素および第2の設定可能なフィードバック・ネ

ットワークを含む第2周波数分割器、(c)第1および第2周波数分割器の出力を選択し

および/あるいは組み合わせ、周波数分割出力信号を形成するよう構成される設定可能な

論理、および(d)第1および第2の設定可能なフィードバック・ネットワークおよび設

定可能な論理を選択可能な形で設定するよう構成されるプログラマブル回路、を含む。

(もっと読む)

周波数同期システム及び周波数同期方法

局部発振器からの局部信号と遠隔発振器からの基準クロック信号の間で周波数を同期させるデジタル周波数ロックループに関連するシステムおよび方法。基準カウンタは、基準クロック信号内のパルスごとにその計数を増分する。基準カウンタ内の値は、設定可能な基準値と比較される。基準カウンタ値と基準値の一致が発生するたびに、ヒット信号が生成され、基準カウンタ値が再初期化される。上記と同時に、局部信号からのパルスごとにフィードバックカウンタが増分される。ヒット信号が生成されると、フィードバックカウンタ内の値が設定可能なフィードバック値と比較(減算による)されて、差の値を生成する。次いで差の値が、局部発振器の周波数を増大または減少させるのに使用するための周波数調整信号に変換される。ヒット信号はまた、フィードバックカウンタを再初期化する。 (もっと読む)

受信機回路、電子機器および変調電波信号を回復する方法

【課題】ベースバンド周波数回復の際、電波信号に対して、広範囲な周波数差にわたり基準クロックを同期化する方法を提供する。

【解決手段】直接変換電波受信機における位相調節に遅延ロック・ループ(DLL)を用いる。受信機回路は、(1)基準クロックを提供する電圧制御発振器(VCO)と、(2)基準クロックを受信し遅延調節信号を提供することができる遅延要素と、(3)電波信号を受信し電波信号および遅延調節信号から回復電波信号を提供する第1チャンネルで、第1ミキサおよび第1フィルタを含む第1チャンネルと、(4)電波信号および遅延調節信号から引き出される位相調節信号を受信し、電波信号および位相調節信号から遅延制御信号を遅延要素に提供する第2チャンネルで、第2ミキサおよび第2フィルタを含む第2チャンネルと、を含む。

(もっと読む)

デジタルシンセサイザ

【課題】位相比較器および信号発振器をデジタル化することによって短時間に同期を確立し、同期状態を高精度でしかも高安定に保持することができるデジタルシンセサイザあるいはデジタル同期発振器を提供する。

【解決手段】少なくとも、デジタル位相比較器21と、デジタル制御発振器22と、分周器23から構成する。

【効果】通信システムにおいて同じ周波数であることが必須の2つの入力信号の間で短時間に同期を確立し、入力信号が停止した場合あるいは取去られた場合にも、同期状態を高精度でしかも高安定に保持する。

(もっと読む)

CDR回路

【課題】異なる複数のビットレートの入力データを再生できるようにしたCDR回路を提供する。

【解決手段】参照クロックCKの周波数に対応した制御信号Vrにより第2の電圧制御発振器3の発振周波数が決定されるPLL回路と、制御信号Vrにより第2の電圧制御発振器3の発振周波数と同じ周波数で再生クロックCLK1を発振し且つ入力データのタイミングに合わせて該再生クロックCLK1の発振位相が調整される第1の電圧制御発振器1と、入力データを再生クロックCLK1によりリタイミングするフリップフロップ回路2とを備えるCDR回路において、PLL回路に、分周比の異なる2個の分周器7A,7Bと、該分周器7A,7Bの内の1つを選択するセレクタ8とを備えさせる。

(もっと読む)

デューティサイクル補正機能を有する遅延ロックループ回路およびその制御方法

【課題】PVT変動が発生しても安定して正確な遅延ロックおよびデューティサイクル補正を可能とする。

【解決手段】外部クロックが入力されて第1内部クロックを生成し、前記第1内部クロックを内部の遅延手段によって遅延して複数の第2内部クロックを出力した後にフィードバックを受けて、前記第1内部クロックとの位相差によって前記遅延手段の遅延時間を調整することにより、前記第2内部クロックの遅延ロックがなされるようにする遅延ロックループブロックと、前記複数の第2内部クロックのデューティサイクルを補正したデューティサイクル補正クロックを出力するデューティサイクル補正ブロックと、前記複数の第2内部クロックの位相比較結果に応じてデューティ補正エラーの発生を判断して、前記デューティサイクル補正クロック又は前記複数の第2内部クロックのうちの1つを前記遅延ロックループブロックにフィードバックするエラー判断部とを備える。

(もっと読む)

カウンタ信号生成装置、クロック信号再構成装置及び通信装置

【課題】IPタイプなどのパケット交換ネットワークに接続されるリモート通信装置におけるPLLのロック又は同期を高速化する。

【解決手段】クロック信号を表すカウンタ信号を生成する装置であって、リファレンスクロック周波数に従ってクロック信号を提供するクロック手段と、提供クロック信号の個数を表す周期的なランプの信号を提供するカウンタと、カウンタ信号を構成するため、選択されたサンプリング周波数によりランプ信号をサンプリングするサンプラとを有し、クロック手段は、リファレンスクロック周波数と異なる少なくとも1つの他の周波数のクロック信号を提供するよう構成し、さらに受信したコマンドに従って提供可能なクロック周波数の1つを選択し、選択されたクロック周波数とリファレンスクロック周波数との間のレシオの値と乗算されたリファレンスサンプリング周波数に等しいサンプリング周波数を規定する制御手段を有する装置を提供する。

(もっと読む)

クロック発生回路

【課題】 DLL回路を用いたクロック発生回路においては、活性化される半導体装置が切り替わる場合に、DLL回路のロック時間が長くなるという問題がある。

【解決手段】 DLL回路の遅延調整回路を固定長遅延回路と、N個の可変長遅延回路で構成し、N個の半導体装置に内部クロックを供給する。N個の可変長遅延回路の遅延差をN個の半導体装置に対する遅延差と同じくする。選択された半導体装置に対し、遅延差がなくなるようにN個の可変長遅延回路からの遅延クロックを選択する。

(もっと読む)

CASレイテンシを利用してロッキングレゾリューション調節が可能な遅延同期ループ回路

【課題】単位遅延器の数を増やさなくとも広いロッキング範囲を有し、またロッキングサイクル時間を減らせる遅延同期ループ回路を提供する。

【解決手段】遅延ライン、位相検出器、制御回路を備える。遅延ラインは、直列連結された多数の単位遅延器を含んで制御信号に応答して選択される単位遅延器を通じて外部クロック信号を遅延させる。位相検出器は、前記外部クロック信号の位相と前記遅延ラインから出力される内部クロック信号の位相とを比較し、外部クロック信号と遅延ラインから出力される内部クロック信号間の位相差を検出する。制御回路は、前記位相検出器の出力信号に応答して前記制御信号を発して遅延制御信号に応答して前記遅延ラインのロッキング位相ステップを可変にする。

(もっと読む)

91 - 100 / 173

[ Back to top ]