国際特許分類[H03L7/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

国際特許分類[H03L7/06]の下位に属する分類

いくつかのループを用いるもの,例.冗長クロック信号発生のためのもの

位相ロックループの細部 (2,372)

間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528)

国際特許分類[H03L7/06]に分類される特許

131 - 140 / 173

安定クロック信号を供給する方法及び装置

本願に記載した実施例は、通信インタフェース(例えば、UARTポート(76))を駆動させるために使用する安定クロック信号を生成するための、低コストの信号調節又は信号校正の方法及び装置に関する。特に、マイクロコントローラ(60)内のプロセッサ(61)は、低周波水晶発振器(72)及びスケーリング・モジュール(78)を使用して、高周波RC発振器(64)によって生成される不安定クロック信号に含まれる周波数オフセット・エラーを除去する。特定のトリガ・イベントが生じた場合(マイクロコントローラの電源が投入された場合、マイクロコントローラが、スリープ・モード又は待機モードからウェイクアップされた場合、マイクロコントローラに通信エラーが生じた場合など)、プロセッサは周波数オフセット・エラーを検出し、除去する。  (もっと読む)

(もっと読む)

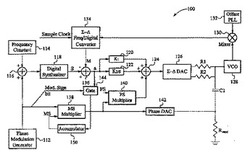

マルチパス角度変調器の利得を常時較正する方法

マルチパス角度変調は、メイン制御ループに追加されたクローズドの二次ループを含み、高周波利得に関して較正ファクタを自動的に調整する。メイン制御ループは、主要パスとして角度変調信号の低周波部分を処理するように構成され、二次ループは、補助ループとして角度変調信号の高周波部分を処理するように構成されている。二次ループは較正情報を検知し、システムが主要動作を行っている間、較正情報を用いて変調ループ内で常時利得をリアルタイムで較正する。その結果、中断時間などのシステム停止または較正に特異的なタイミングが必要でなくなり、変調パスのバランスがとれる。較正は背景プロセスとして常時行われる。角度変調はすべての変調タイプのシステムに適用可能である。 (もっと読む)

クロック信号を発生するクロック発生回路及び方法

【課題】クロック信号を発生するクロック発生回路及び方法を公開する。

【解決手段】クロック発生回路は、外部クロック信号を直接受信して、反転された外部クロック信号を発生するインバータと、一番目のループ回路が反転外部クロック信号を受信してn(nは2以上の定数)個のノードをそれぞれ備え、M−1(Mは1以上の定数)個のループ回路のそれぞれがn個のノードの対応する1つからn個の中間内部クロック信号それぞれを発生し、n個の中間内部クロック信号の周波数が外部クロック信号及び反転外部クロック信号の周波数の倍数であることを特徴とする直列に配列されたM個のループ回路と、それぞれが直列に接続されて以前のループ回路から対応する中間内部クロック信号を受信し、対応する中間内部クロック信号を次のループ回路に出力するM−1個のインバータそれぞれと、を具備するn個のインバータの集合で構成されている。

(もっと読む)

電気ヒューズを用いてPLL構成データを格納するための装置及び方法

【課題】電気ヒューズを用いてPLL構成データを格納するための装置及び方法を提供すること。

【解決手段】集積回路内に存在する電気ヒューズ150の一部分がPLL構成データのために取っておかれる。パワーアップ時に、パワーアップ・コントローラ及び電気ヒューズ・コントローラ120は、電気ヒューズ150の一部分におけるデータを感知し、基準クロック下のPLL回路195への直列転送を指示する。転送が完了すると、パワーアップ・コントローラは、構成データをロードし、開始するようにPLLロジックを指示する。製造にあたって、所与のデバイスの特性及び意図される用途に基づいて、そのデバイス上のPLLデフォルト値を適合させるようにすることを可能にする。同じPLL回路195を同じ又は異なるアーキテクチャにおいて用いて、電気ヒューズ150からPLL回路195に送られた構成データに基づいて、異なる動作を実行することができる。

(もっと読む)

デジタル位相検出器

【課題】 従来、デジタル位相検出器における位相検出限界は、遅延素子の遅延時間により決定されるため、例えば、PLL回路に低ジッタ特性が要求される場合には、全デジタルPLL回路は不適当であった。

【解決手段】 第1のクロックCLKfを遅延する複数の第1の遅延素子1011〜101nと、第2のクロックCLKrを遅延する複数の第2の遅延素子1021〜102nと、前記第2の遅延素子により順次遅延された前記第2のクロックREF1〜REFnに従って、前記第1の遅延素子により順次遅延された前記第1のクロックFB1〜FBnを取り込み、相対的な位相関係を表すデジタル値Q1〜Qnを保持する複数のデータ保持回路1031〜103nと、を備えるように構成する。

(もっと読む)

オンダイターミネーション制御装置

【課題】本発明はオンダイターミネーション制御装置に関し、特に、ODT(On−Die Termination)とDLL(Delay Locked Loop)のディセーブル状態でクロック信号を制御し電流の無駄使いを抑えることのできるオンダイターミネーション制御装置を提供すること。

【解決手段】本発明のオンダイターミネーション制御装置は、モード設定に応じて状態が異なるようにするクロック制御信号を出力するモードレジスタセットと、前記クロック制御信号のアクティブ状態に応じて第1内部クロックと第1同期クロックを受信し、第2内部クロックと第2同期クロックを選択的に出力するクロック制御部と、ODT制御信号を受信し、前記第2内部クロックと前記第2同期クロックに同期して、オンダイターミネーションブロックの動作を制御するオンダイターミネーション制御部とを備える。

(もっと読む)

信号処理装置、信号処理方法

【課題】デジタルPLLのループ遅延の短縮化と、そのデジタルPLLによって位相同期が取られた再生データの高精度化とを両立させる。

【解決手段】ビタビ検出用の位相補間フィルタ9と、PLL8にある位相誤差検出用の位相補間フィルタ81とを設ける。位相オフセット演算器84において位相誤差の積算値である位相オフセット量φに応じて、位相補間フィルタ9および位相補間フィルタ81では、タップ係数が逐次更新されるが、位相補間フィルタ81は、位相補間フィルタ9と比較して、タップ数/ビット幅が小さく設定され、PLL8内のループ遅延時間を短縮する。

(もっと読む)

クロックデータリカバリ回路

【課題】 データ信号とクロックとの周波数に差がある場合でも、2相の内部クロックを必要とせずに、データ信号とクロックとの同期が可能なCDR回路を提供すること。

【解決手段】 PD14は、DATAとVDL11からのVDL出力との位相差を検出する。CODE Operator13は、出力クロックの1周期と同じ遅延に相当する制御コードの値を検出する。そして、PD14による検出結果に応じて制御コードを変更しながら出力クロックをデータ信号に同期させる際、VDL11の遅延量がクロックの1周期分を超えるときに、制御コードに対して出力クロックの1周期と同じ遅延に相当する制御コードを一度に加算または減算する。したがって、データ信号とクロックとの周波数に差がある場合でも、同一のクロック位相を与えながらデータ信号とクロックとの同期をとることが可能となる。

(もっと読む)

クロック回復方法、記憶媒体を読出すためのドライブ、およびクロック回復回路

【課題】クロック/データ信号におけるクロック回復を改善するための方法、回路、およびドライブを提供する。

【解決手段】ロックループ回路、たとえばPLLにタイミング基準が提供される。このタイミング基準は、回復されているクロックの周波数の期待値に基づいて更新される。回復されている各クロックまで追従させたシステムクロックが出力される。各システムクロックの現在の周波数が見積られ、1つ以上のシステムクロックの見積られた現在の周波数に基づき、期待値が更新される。データストリームが一連のブロックに分離されるデータを含む場合、更新は、ブロックの終端の後、および、後続のブロックの開始部の前に行なわれ得る。見積りは、各ブロックに対して定期的におよび/または複数回行なわれ得る。

(もっと読む)

集積回路、再生装置及び再生方法

【課題】 本発明は、集積回路、再生装置及び再生方法に関し、例えば非接触型のICカードシステムに適用して、クロックの周波数がばらついた状態で、デューティー比が50〔%〕から変化した場合でも、正しくデータを再生することができるようにする。

【解決手段】 本発明は、ペイロードの部分に比して速く収束するようにPLL回路の動作を切り換えて、90度位相の異なる基準信号の一方を入力信号に位相同期させるようにこれら基準信号を位相制御し、他方の基準信号が入力信号に位相同期したとの位相比較結果が得られた場合に、直前の制御を継続する。

(もっと読む)

131 - 140 / 173

[ Back to top ]