国際特許分類[H03L7/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

国際特許分類[H03L7/06]の下位に属する分類

いくつかのループを用いるもの,例.冗長クロック信号発生のためのもの

位相ロックループの細部 (2,372)

間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528)

国際特許分類[H03L7/06]に分類される特許

61 - 70 / 173

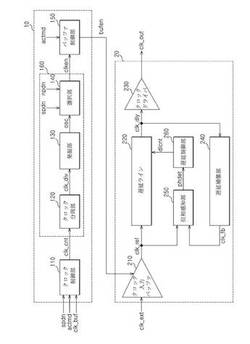

半導体集積回路及びその制御方法

【課題】本発明は、安定ているクロックを生成するために、DLL回路のスマートパワーダウンモードを具現する半導体集積回路及びその制御方法を提供する。

【解決手段】本発明の半導体集積回路は、スマートパワーダウン信号がイネーブルされると、周期的にイネーブルされるパルス信号であるバッファイネーブル信号を生成するDLL制御手段;及び、バッファイネーブル信号に応じて外部クロックの位相を制御して、出力クロックを生成するDLL回路を含む。

(もっと読む)

PLL回路、無線端末装置およびPLL回路の制御方法

【課題】ディジタル制御される発振器を有するPLL回路において、ループ利得を切り替える際に生じるオフセットを補償し、高速にロックさせることが可能なPLL回路を提供すること。

【解決手段】基準周波数の各周期において、ディジタル値に変換された分周比の累積加算値と、ディジタル値を用いて制御される発振器からの発振信号の累積加算値とを比較する位相比較部と、利得を可変させる可変利得増幅部を備え、位相比較部の出力を任意の設定値に収束させるデータ変換部と、位相比較部の出力を用いて可変利得増幅部の利得の変化によって生じるオフセットを検出するオフセット検出部と、オフセット検出部で検出されたオフセットを、可変利得増幅部の利得が変化するタイミングで補償するオフセット補償部と、を含む、PLL回路が提供される。

(もっと読む)

TDC回路、PLL回路、並びに無線通信装置

【課題】入力信号とトリガ信号の間に遅延時間が存在するというフリップフロップ自身の特性に起因した検出誤差を改善するTDC回路を提供する。

【解決手段】各フリップフロップ105−1、…は、CLKREF、B2からDelay1だけ遅延したタイミングをトリガにして入力信号A0、A1、A2をそれぞれ保持し、データ系列[C0:C3]として“1110”を得る。例えば、[C0:C1]が“11”の場合は遅延量の符号をマイナスとし、[C2:C3]を左から1から0に変化する点をカウントすることでデコードされる。よって、この例では、“−1”とデコードされ、Delay=−Dを検出する。

(もっと読む)

グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステム

【課題】 グローバルPLLベース・タイミング・リカバリ・ループの遅延補償方法及びシステムを提供する。

【解決手段】 一実施形態のシステムは、個々のチャネルに関連する誤差信号をそれぞれ受け取る複数の入力を備えたグローバルPLL回路と、前記グローバルPLL回路と結合された遅延補償回路と、を含む。一実施形態の方法は、個々のチャネルにそれぞれ関連する複数の誤差信号を受け取るステップと、前記誤差信号に1つ又は複数の遅延補償信号を適用するステップと、前記チャネルのそれぞれに関する位相誤差出力信号を出力するステップと、を含む。

(もっと読む)

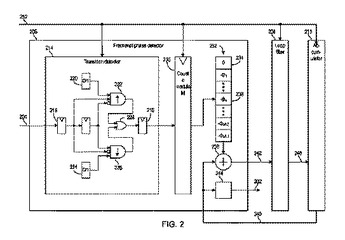

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

小数位相検出器を用いたクロック生成

入力信号から、低減されたスキューを有する1つまたはより多くの出力クロック信号を生成する回路が提供される。入力信号は、出力クロック信号の周波数とは異なった周波数を有するオリジナルクロックの遷移から導き出される遷移を有する。出力クロック信号の周波数は、入力信号についての周波数と、整数比との乗算からの積である。回路は、積算器と、小数位相検出器と、ループフィルタを含む。積算器は、数値的オフセット値を数値的位相値に周期的に追加する。出力クロック信号は、この数値的位相値から生成される。小数位相検出器は、数値的位相値から、入力信号の遷移の各々についてのそれぞれの数値的位相誤差を生成する。ループフィルタは、それぞれの数値的位相誤差のフィルタリングから数値的オフセット値を生成する。  (もっと読む)

(もっと読む)

位相同期回路及び半導体チップ

【課題】 複数のチップ内の内部回路に供給される動作タイミング用のクロック信号の位相を正確に同期させることができる位相同期回路を提供する。

【解決手段】 第1チップ内において第1クロック信号を遅延させて第2クロック信号を生成し、2クロック信号を第1内部回路の動作タイミング用として第1内部回路に供給する第1遅延手段と、第2クロック信号を遅延させて第3クロック信号を生成する第2遅延手段と、第2チップ内において第1クロック信号を第1チップとの間の第1配線を介して入力し、その入力した第1クロック信号を第2内部回路の動作タイミング用として第2内部回路に供給する入力手段と、第1入力手段によって入力された第1クロック信号を第2配線を介して帰還クロック信号として第1チップに帰還させる帰還手段と、第3クロック信号と帰還クロック信号との位相差が減少するように第1及び第2遅延手段各々の遅延時間を制御する位相比較手段とを備える。

(もっと読む)

デジタル位相ロックループ(DPLL)における電力消費を制御するシステム及び方法

【解決手段】相異なる周波数クロックの組から選択された参照クロックを生成するように適合されたプログラマブル周波数デバイスを備えた装置であって、プログラマブル周波数デバイスは更に、相異なる周波数クロック間での切り替えの際に、参照クロックのトリガエッジの同じ時間的関係を維持するように適合される。装置は更に、入力信号と出力信号との間の所定の位相関係を確立するために選択された参照クロックを使用する、デジタルPLL(DPLL)のような位相ロックループを備える。相異なる周波数クロック間の切り替えの際に参照信号の同じ時間的関係を実質的に維持することで、参照クロックが変化しても、位相ロックループ(PLL)の連続且つ有効な動作は、大きくはディスターブされない。これは、装置の電力消費を制御するために使用され得る。 (もっと読む)

ディジタル位相同期ループ(DPLL)の時間対ディジタル変換器(TDC)のパワーオンゲーティング窓を較正するためのシステム及び方法

ディジタル位相同期ループ(DPLL)の時間対ディジタル変換器(TDC)のパワーオンゲーティング窓を較正するのに関係するシステム及び方法が開示される。ゲーティング窓は同時に電力の効率的方法でTDCを動作させながらDPLLの適切な動作を保証するために較正される。特に、その技術はTDCゲーティング窓の幅を既定値に設定すること;制御ループが実質的にロックされるまで、DPLLを動作させること;DPLLの位相誤差デバイスによって生成される位相誤差信号をモニターしながら、TDCゲーティング窓の幅を所定の量だけ減少させること;位相誤差が所定の閾値に実質的に到達するか、或いは横切るときにTDCゲーティング窓の現在の幅を決定すること;及びTDCゲーティング窓の動作幅の誤差のマージンに組込む所定の量だけTDCゲーティング窓の現在の幅を増加させることを要する。  (もっと読む)

(もっと読む)

クロックデータリカバリ回路

【課題】本発明はクロックデータリカバリ回路に関し,受信データに同期したクロックを生成し,データのタイミングを調整し,ジッタ特性を改善することを目的とする。

【解決手段】入力データ変化を検出し,パルス生成するデータ変化パルス生成手段とこの信号を平滑化する第1ループフィルタと第2クロック信号の間の位相差信号を生成する位相差信号生成手段と,この信号を平滑化する第2ループフィルタと制御信号生成手段の信号を平滑化する第3ループフィルタと,第1及び第2ループフィルタの信号から制御信号を生成する制御信号生成手段と,位相差信号生成手段の信号に基づき第1クロック信号周期に応じた時間幅の第3クロック信号を供給する高周波ジッタ吸収用クロック生成手段と,第3ループフィルタからの信号の電圧レベルに応じて第1クロック周波数を可変供給する電圧制御発振手段で入力データに同期した第1クロック信号を再生するよう構成する。

(もっと読む)

61 - 70 / 173

[ Back to top ]