国際特許分類[H03L7/06]の内容

電気 (1,674,590) | 基本電子回路 (63,536) | 電子的振動またはパルス発生器の自動制御,起動,同期または安定化 (3,550) | 周波数または位相の自動制御;同期 (3,453) | 周波数または位相ロックループに加えられる基準信号を用いるもの (3,073)

国際特許分類[H03L7/06]の下位に属する分類

いくつかのループを用いるもの,例.冗長クロック信号発生のためのもの

位相ロックループの細部 (2,372)

間接的な周波数の合成,すなわち周波数または位相ロックループを用いる予じめ決められた多数の周波数の内の所望の一つを発生するもの (528)

国際特許分類[H03L7/06]に分類される特許

41 - 50 / 173

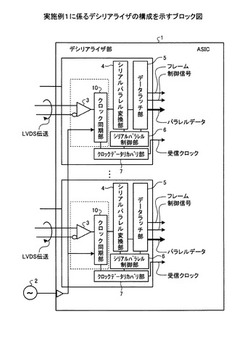

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、ジッタを低減する。

【解決手段】第1の発振回路および第2の発振回路はそれぞれ2つの周波数制御端子を備え、それぞれの一方の周波数制御端子に周波数制御信号Aを入力する構成であり、第2の発振回路の他方の周波数制御端子に固定の周波数制御信号Bを与え、第1の発振回路および第2の発振回路の各発振周波数を比較し、その周波数誤差に応じた周波数制御信号Cを第1の発振回路の他方の周波数制御端子に与えるばらつき補償回路を備える。

(もっと読む)

オーバーサンプリング回路

【課題】オーバーサンプリング型CDR回路で用いる多相クロックの相互の位相差が等間隔になるように高精度に位相を補正できるオーバーサンプリング回路を提供する。

【解決手段】多相クロックを生成する多相クロック生成部200と、多相クロックの位相差を検出して、該検出結果に基づいて位相制御信号を発生する位相制御部205と、多相クロックの本数分の遅延回路を有し、多相クロックをそれぞれの遅延素子に入力された信号の通過時間を、位相制御信号に基づいて調整することで多相クロック間の位相差を調整する位相調整部203と、を備え、各遅延回路300は、直列に接続されたサイズの異なる複数のインバーターと、該複数のインバーターの後段に接続したインバーターと、からなり、複数のインバーターから選択される一つインバーターの出力抵抗と、後段に接続したインバーターの入力容量の積に基づいて通過時間を調整する。

(もっと読む)

アキュムレータおよび位相デジタル変換器を使用する2ポイント変調のデジタル位相同期ループ

2ポイント変調をサポートするデジタル位相同期ループ(DPLL)が説明される。1つの設計において、DPLLは、位相デジタル変換器、ループ内で動作するループフィルタ、ローパス変調パスのための第1の処理ユニットおよびハイパス変調パスのための第2の処理ユニットを含む。第1の処理ユニットは、入力変調信号を受信し、位相デジタル変換器の後でループフィルタより前のループの内部の第1のポイントに対して第1の変調信号を供給する。第2の処理ユニットは、入力変調信号を受信し、ループフィルタより後のループの内部の第2のポイントに対して第2の変調信号を供給する。第1の処理ユニットは、周波数を位相に変換するために入力変調信号を累算するアキュムレータを含み得る。第2の処理ユニットは、可変利得で入力変調信号をスケールするスケーリングユニットを含み得る。 (もっと読む)

位相調整装置及び無線受信装置

【課題】効率的に且つ低消費電力で目的の信号との位相を調整するのに好適な位相調整装置及び無線受信装置を提供する。

【解決手段】位相調整装置100を、制御電圧によって遅延量を可変可能なインバーター回路IV1〜IVNをループ構成に接続してなる遅延段回路10と、遅延段回路10の遅延量を一定に保持する位相同期用回路20と、遅延段回路10の各接続部に入力端子が電気的に接続された接続切替回路SW1〜SWMを含む接続切替回路群30と、切替制御回路40とを含む構成とし、切替制御回路40は、遅延段回路10における1つおきに且つ周回して順に並ぶ各インバーター回路に対応する接続切替回路を1つずつ選択し、選択した接続切替回路が、遅延信号を後段の回路に供給するように、その他の接続切替回路が遅延信号を後段の回路に供給しないようにする切替制御信号を生成し、これを各接続切替回路に供給する。

(もっと読む)

発振器

【課題】劣化が少なく目的とする周波数のクロックパルスを出力することのできる発振器を提供すること。

【解決手段】発振器1は、固定電極212と空隙を隔てて配置された可動電極214とを有する振動子21を用いた発振器であって、基準電圧を供給する基準電圧供給回路3と、

クロックパルスの入力によって作動する昇圧回路41を備え、基準電圧を所定の大きさの電圧に変換して出力する電圧調整回路4とを有し、前記振動子21は、電圧調整回路4から出力された前記所定の大きさの電圧が固定電極212と可動電極214との間に印加されるように構成されており、昇圧回路41に入力される前記クロックパルスは、振動子21を発信源として得られたものであることを特徴とする。

(もっと読む)

クロック位相調整回路

【課題】実装面積や消費電力を低減させることができるクロック位相調整回路を提供すること。

【解決手段】n個の第1の遅延素子15を多段に接続し、入力クロック信号INCLKをその周期の1/nずつ遅延させたクロック信号をそれぞれ出力するDLL回路2と、n個の第1の遅延素子15から出力されるクロック信号のうち1つのクロック信号を選択して出力する第1のセレクタ回路3と、この第1のセレクタ回路3から出力されるクロック信号CLK1を遅延させる遅延部4を備えている。遅延部4は、1又は複数の直列に接続された遅延回路20を有しており、この遅延回路20は、前段の遅延回路10に設けられた第1の遅延素子15の遅延量に対して1/2の遅延量を有する第2の遅延素子21と、入力されたクロック信号CLK1と第2の遅延素子21により遅延されたクロック信号のいずれかを選択して出力する第2のセレクタ回路22とを備える。

(もっと読む)

発振器制御装置

【課題】安定したPLL動作を確立できる発振器制御装置を提供する。

【解決手段】発振器制御装置は、発振器調整信号OTWに応じた発振周波数の発振信号を出力するデジタル制御発振器100と、発振信号で同期化された基準信号に基づいてカウント値を出力するカウンタ120と、発振信号と基準信号との位相差dを算出する時間デジタル変換器130と、カウント値と位相差とを加算し、加算値を第1位相情報として出力する加算器140と、発振信号の立ち上がりタイミングと基準信号の立ち上がりタイミングとの時間差が所定時間未満である場合に、デジタル制御発振器の発振周波数を設定するための位相制御信号Acc1に基づいて第1位相情報を補正し、第2位相情報を出力する補正部160と、位相制御信号と第2位相情報との差分を平滑化するフィルタ180と、フィルタ出力にパラメータKを乗算して発振器調整信号OTWを出力する乗算器190と、を備える。

(もっと読む)

クロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路

【課題】動作信頼性を向上させるクロックリカバリ回路、及びそれを備えるクロックデータリカバリ回路を提供すること。

【解決手段】受信信号を再生するタイミング情報が重畳された前記受信信号とリカバリクロックとの位相差に基づいて、前記受信信号とリファレンスクロックとの周波数オフセット情報を検知する周波数差検知部34と、前記周波数検知部34が検知した前記周波数オフセット情報に基づいて、前記受信信号と前記リカバリクロックとの位相差を補正する補正部30とを具備する。

(もっと読む)

デジタルPLL回路及びデジタルPLL動作方法

【課題】CLVスピンドル制御のランダムシーク時でもスループット低下を抑え、かつ安価で消費電力を抑えたワイドキャプチャ対応のデジタルPLL回路を提供する。

【解決手段】本発明のデジタルPLL回路10Aは、周波数値fq’に応じてマスタクロックsclkの周波数を切り替えるマスタクロック切り替え手段10Bと、周波数値fq’に一定の倍率を乗じて数値制御発振器6へ出力するとともに、マスタクロックsclkの周波数が切り替わる前後で同期クロックgclkの周波数が一定になるように前記倍率を切り替える倍率切り替え手段10Cと、を備えたことを特徴とする。

(もっと読む)

41 - 50 / 173

[ Back to top ]