国際特許分類[H05K3/34]の内容

電気 (1,674,590) | 他に分類されない電気技術 (122,472) | 印刷回路;電気装置の箱体または構造的細部,電気部品の組立体の製造 (64,965) | 印刷回路を製造するための装置または方法 (27,705) | 電気部品,例.抵抗器,を印刷回路に取り付けること (5,488) | 印刷回路に対する電気部品または電線の電気的接続 (5,485) | ハンダ付けによるもの (4,578)

国際特許分類[H05K3/34]に分類される特許

4,561 - 4,570 / 4,578

ペースト特性測定方法とそのペースト特性測定機

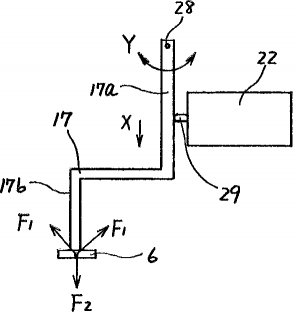

【目的】 従来の垂直方向のペ−ストの作用応力以外に水平分力を含む作用応力を検出すると共に、プリント基板上の微量なペ−ストであってもその応力を正確に測定できるようにすることで正確にペ−ストのぬれ特性を測定する。

【構成】 プリント基板に設けたペ−ストにチップ部品の金属端子を上記プリント基板に接触しないように定圧で、あるいは定量を相対的に挿入し引き離すまでの過程において、ペ−ストが溶融から上記チップ部品の金属端子にぬれる全過程において当該ペ−ストと上記チップ部品の金属端子との間に働く応力の変化を検出し、溶け時間、ぬれ時間、ぬれ応力を検出測定する。

(もっと読む)

プリント配線板

【目的】 実装部品ネジ止め個所のランドに対する前記実装部品あるいはネジ止め用ワッシャの密着性を向上させこと、また、大電流を流した際の放熱特性を高めることにある。

【構成】 実装部品ネジ止め用のランド3に格子形状またはトーン形状の半田瘤発生防止部31を形成し、また、導電性パターン4の平坦な表面に放熱用の凹凸部41,42を設けたものである。

【効果】 ランド上にコーティングされた半田瘤の発生を未然に防止でき、前記ランドに対する実装部品あるいはネジ止め用ワッシャの密着性が高くなる。また、導電性パターンの表面積が凹凸部によって拡大され、大電流を流した際の放熱特性が高くなる。

(もっと読む)

高速信号伝送用回路基板

【目的】 信号線とVIAランド間におけるインピーダンスの不連続点での影響を抑え、信号の反射の少ない高速信号伝送用回路基板構造を提供すること。

【構成】 符号1a,1bは多層基板である高速信号伝送用回路基板の層間を電気的に接続するためのVIA、符号2a,2b,2cはそれぞれ第1層、第2層、第3層の概ね十字形をしたVIAランドである。各層のVIAランド2の形状をこのように十字型とすることにより、VIAランドの面積が減少し、高速信号伝送用回路基板内に高周波信号を伝送させた場合でも、キャパシタンス成分が抑えられ、インピーダンスの不連続点の発生を減少させることができる。

(もっと読む)

半田付け検査方法及び装置

【目的】 X線の投射により,半田付け部の良否を精度良く判定すること。

【構成】 半田付け部の断面形状の良否を,半田付け部の基板と部品とのそれぞれの接点に対応する接点対応点を通過する直線と透過量分布曲線との比較において行うので,半田付け部の断面形状の良否が正確に判断される。また、半田付け部の断面形状の良否を,検出した断面形状と理想状態の断面形状とを形状を示す各パラメータの定量的比較において行うので,半田付け部の断面形状の良否が正確に判断される。

(もっと読む)

表面実装プリント回路基板

【構成】 ファインピッチパッド3とラフピッチパッド4を有するプリント回路基板1の、各パッド3、4上に電子部品の半田付けに必要な厚さの半田層5、6を形成し、このプリント回路基板に半田層5を覆うように半田付け用フラックス7を塗布し、その上に剥離性シート8を張り付けた。

【効果】 剥離性シートを剥がして電子部品を載せ、加熱するだけで、電子部品を実装できる。半田層は電子部品のない状態で形成されるので、ブリッジやボールをなくすことができ、この半田層で電子部品の半田付けを行うので、確実にブリッジやボールによる不良発生のない部品実装を行える。半田層は部品実装までの間に酸化や汚れで劣化することがない。

(もっと読む)

はんだ付け用チャンバの雰囲気形成方法

水性液体洗浄剤組成物

【構成】 界面活性剤および炭素数8〜16のパラフィン系炭化水素あるいは更に短鎖アルコールのアルキレンオキシド付加物を含有する水性液体洗浄剤。

【効果】 環境破壊を起こさない水系の安全な洗浄剤であり、液晶物質、半田フラックス、油脂類等に対して高度な洗浄性能を示し、液晶セル用洗浄剤、半田フラックス用洗浄剤、金属部品・治工具等の脱脂用洗浄剤など、電子部品用洗浄剤として好適である。

(もっと読む)

印刷配線板

【目的】 主に高密度実装された電子機器に使用する印刷配線板に関し、大電流が流せてしかも小型化された印刷配線板を提供することを目的としている。

【構成】 基板11と、基板11上に敷設された大電流を流すための第1の配線パターン12と、小電流を流すための第2の配線パターン13とを備え、前記第1の配線パターン12の略中央部には、電流の流れる方向と並行に線状のレジスト印刷18を設けているので、第1の配線パターン12の略中央部に設けた線状のレジスト印刷18の部分には半田が付着せず、この線状のレジスト印刷を避けるようにして半田が盛り上がって付着することになる。したがって、電流通路の断面積が大きくなり、結果として印刷配線板の小型化が図れる。

(もっと読む)

ベアチツプLSIの実装構造

【目的】 直接ベアチップLSIを多層構成の回路基板に密封実装するベアチップLSIの実装構造に関し、小形化、高密度実装化及び高放熱化が図れ、EMI対策も講じられるベアチップLSIの実装構造を提供することを目的とする。

【構成】 多層構成の回路基板1のベアチップLSI9の搭載部が段付凹部2を成し、底面には内層の広範囲に広がり面を有し、ベアチップLSI9をダイボンディングさせる内層導体3が露出し、段部21にはベアチップLSI9と接続する回路端子4が、対向位置に内層導体により配設してあり、段付凹部2の表面縁部には接地回路に通じる環状の導体パターン11を有し、一面が全導体面51を成し、他の面に絶縁して回路パターン52を形成させたキャップ5にて、段付凹部2を覆い、全導体面51を前記導体パターン11に密着固定させて段付凹部2内部を密封し、回路パターン52を回路基板1の表面回路パターン12に接続させて成るように構成する。

(もっと読む)

プリント配線板の配線構造

【目的】部品実装密度の高いプリント配線板の配線構造を提供する。

【構成】プリント配線板の表面に設けられた表面実装用パッド1の直下に非貫通スルーホール4を形成し、これにより内部配線層5に接続する。

(もっと読む)

4,561 - 4,570 / 4,578

[ Back to top ]