発光素子の駆動回路およびそれを用いた発光装置および電子機器

【課題】スキャニング動作時の発光素子の輝度を安定化する。

【解決手段】誤差増幅器10は、n個のLED端子それぞれの電圧VLED1〜VLEDnのうち最も低い電圧と所定の基準電圧VREFの誤差にもとづき、基準電圧VREFの方が高いときに誤差に応じたソース電流ISRCを生成し、基準電圧VREFの方が低いときに誤差に応じたシンク電流ISINKを生成し、FB端子に生ずるフィードバック電圧VFBを変化させる。誤差増幅器10は、ソース電流ISRCとシンク電流ISINKの両方を生成可能な第1状態φ1と、ソース電流ISRCのみ生成可能な第2状態φ2と、が切りかえ可能に構成される。

【解決手段】誤差増幅器10は、n個のLED端子それぞれの電圧VLED1〜VLEDnのうち最も低い電圧と所定の基準電圧VREFの誤差にもとづき、基準電圧VREFの方が高いときに誤差に応じたソース電流ISRCを生成し、基準電圧VREFの方が低いときに誤差に応じたシンク電流ISINKを生成し、FB端子に生ずるフィードバック電圧VFBを変化させる。誤差増幅器10は、ソース電流ISRCとシンク電流ISINKの両方を生成可能な第1状態φ1と、ソース電流ISRCのみ生成可能な第2状態φ2と、が切りかえ可能に構成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発光素子の駆動回路に関する。

【背景技術】

【0002】

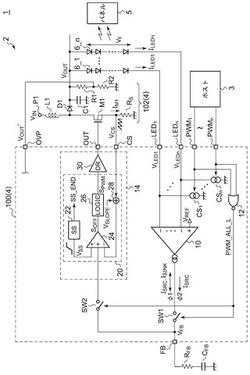

近年、液晶パネルのバックライトや照明機器として、LED(発光ダイオード)をはじめとする発光素子を利用した発光装置が利用される。図1は、本発明者が検討した発光装置の構成を示す回路図である。発光装置2rは、複数のLEDストリング6_1〜6_nと、その駆動回路100r、出力回路102、ホストプロセッサ3を備える。

【0003】

各LEDストリング6は、直列に接続された複数のLEDを含む。DC/DCコンバータ4rは、入力電圧VINを昇圧してLEDストリング6_1〜6_nの一端に駆動電圧VOUTを供給する。

【0004】

駆動回路100rは、LEDストリング6_1〜6_nごとに設けられた電流源CS1〜CSnを備える。各電流源CSiは、対応するLEDストリング6_iに、目標輝度に応じた駆動電流ILEDiを供給する。

【0005】

駆動回路100rの一部と出力回路102は、DC/DCコンバータ4rを構成する。出力回路102は、インダクタL1、スイッチングトランジスタM1、整流ダイオードD1、出力キャパシタC1、抵抗R1、R2、検出抵抗Rsを含む。駆動回路100rは、スイッチングトランジスタM1のオン、オフのデューティ比を制御することにより、駆動電圧VOUTを調節する。具体的には、複数チャンネルのLEDストリング6_1〜6_nそれぞれのカソード端子の電圧VLED1〜VLEDnのうち最も低い電圧が所定の基準電圧VREFと一致するように、スイッチングトランジスタM1のデューティ比をフィードバック制御する。

【0006】

フィードバック端子(FB端子ともいう)には、位相補償用の抵抗RFBおよびキャパシタCFBが接続される。誤差増幅器10はトランスコンダクタンスアンプであり、カソード端子の電圧VLED1〜VLEDnのうち最も低い電圧が所定の基準電圧VREFの誤差を増幅し、誤差に応じた電流を生成して、フィードバック端子FBにフィードバック電圧VFBを発生させる。

【0007】

DC/DCコンバータ制御部14は、パルス変調器20、ドライバ30を含む。

パルス変調器20は、フィードバック電圧VFBを受け、フィードバック電圧VFBにもとづいて、スイッチングトランジスタM1を駆動するためのパルス信号SPWMを生成する。図1のパルス変調器20は、いわゆるピーク電流モードのパルス幅変調器である。ソフトスタート回路22は、ホストプロセッサ3からのスタンバイ信号に応じて、時間とともに上昇するソフトスタート電圧VSSを生成する。コンパレータ24は、スイッチングトランジスタM1に流れる電流IMに応じた検出信号VCSを、フィードバック電圧VFBとソフトスタート電圧VSSのうち低い電圧と比較し、比較結果に応じたオフ信号SOFFを生成する。スロープ補償回路28は、検出信号VCSにスロープ信号VSLOPEを重畳する。

【0008】

ロジック部26は、オフ信号SOFFがアサートされると、パルス信号SPWMを、スイッチングトランジスタM1のオフに対応するレベル(以下、オフレベルという)に遷移させる。また所定のクロック信号と同期して、あるいは所定のオフ時間経過後に、パルス信号SPWMをスイッチングトランジスタM1のオンに対応するレベル(以下、オンレベルという)に遷移させる。ドライバ30は、ロジック部26からのパルス信号SPWMにもとづいてスイッチングトランジスタM1をスイッチングする。

【0009】

こうした発光装置2rにおいて、LEDストリング6の輝度を調節するために、駆動電流ILEDをPWM(Pulse Width Modulation)制御する場合がある。具体的には、ホストプロセッサ3は、各チャンネルのLEDストリング6の輝度に応じたデューティ比を有するパルス調光信号PWM1〜PWMnを生成する。各チャンネルの電流源CS1〜CSnは、対応するパルス調光信号PWM1〜PWMnにもとづいてスイッチング制御される。このような制御を、バースト調光、バースト制御とも称する。

【0010】

バースト調光を行う場合、あるチャンネルの電流源CSiがオフとなる期間、そのチャンネルのLEDストリング6のカソード端子の電位VLEDiは、ハイレベル電圧にプルアップされて、フィードバックの対象から外される。なぜなら消灯期間のチャンネルのカソード端子VLEDiは、負荷の状態とは無関係のレベルをとるからである。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2008−186668号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

複数チャンネルのLEDストリング6_1〜6_nを、ある位相差で駆動する場合がある。これをスキャニング動作という。このときのパルス調光信号PWM1〜PWMnは、ある位相差を有している。

【0013】

図2は、図1の駆動回路100rのスキャニング動作時の波形図である。上から順に、パルス調光信号PWM1、PWM2、PWM3、フィードバック電圧VFB、出力電圧VOUT、全チャンネルの駆動電流の合計ILEDが示される。n=3チャンネルであり、パルス調光信号PWM1、PWM2、PWM3が120°の位相差でハイレベル(点灯期間)となる。

【0014】

LEDストリング6の電圧降下(順方向電圧)VFは、チャンネルごとにばらつく。図2の波形図は、LEDストリング6_1の電圧降下VF1、LEDストリング6_2の電圧降下VF2、LEDストリング6_3の電圧降下VF3の間に、関係式(1)が成り立つとする。

VF1>VF3>VF2 …(1)

【0015】

時刻t0以前は、第1チャンネルと第2チャンネルが点灯期間であり、第1チャンネルのカソード電圧VLED1が基準電圧VREFと一致するようにフィードバックがかかる。

期間t0−t1は、第2チャンネルが点灯期間であり、第2チャンネルのカソード電圧VLED2が基準電圧VREFと一致するようにフィードバックがかかる。

期間t1−t2は、第2チャンネルと第3チャンネルが点灯期間であり、第3チャンネルのカソード電圧VLED3が基準電圧VREFと一致するようにフィードバックがかかる。

【0016】

また、点灯期間のチャンネルにおいては、以下の関係式(2)が成り立つ。

VOUT=VF1+VLED1=VF2+VLED2=VF3+VLED3 …(2)

【0017】

時刻t0以前、LEDストリング6_1のカソード端子LED1の電位が基準電圧VREFと一致するように出力電圧VOUTが調節される。時刻t0にパルス調光信号PWM1がローレベルとなると、第1チャンネルがフィードバック対象から除外され、第2チャンネルがフィードバック対象となる。

VF1>VF2が成り立つため、時刻t0におけるLEDストリング6_2のカソード電圧VLED2は、基準電圧VREFより高くなっている。このとき誤差増幅器10は、カソード電圧VLED2が基準電圧VREFと一致するように電流を吸い込み(シンク)、フィードバック電圧VFBを低下させ、出力電圧VOUTを低下させる。

【0018】

続いて時刻t1において、第3チャンネルが点灯期間となる。これにより、第3チャンネルのカソード電圧VLED3が基準電圧VREFと一致するようにフィードバックがかかる。

VF3>VF2が成り立つため、時刻t1におけるLEDストリング6_3のカソード電圧VLED3は、基準電圧VREFより低くなっている。したがって誤差増幅器10は、カソード電圧VLED3が基準電圧VREFと一致するように電流を吐き出す(ソース)ことにより、フィードバック電圧VFBを上昇させ、それにより出力電圧VOUTを上昇させようとする。

【0019】

ところがFB端子には、位相補償用のキャパシタCFBおよび抵抗RFBが接続されており、フィードバック電圧VFBは、カソード電圧VLEDと基準電圧VREFの誤差に直ちに追従せず、遅れて変化する。つまり出力電圧VOUTは、時刻t1に直ちに上昇に転ずることなくさらに低下し続け、出力電圧VOUTの変動量が大きくなる。

その結果、時刻t1の直後に、第3チャンネルのカソード端子VLED3が基準電圧VREFを大きく下回って、電流源CS3が生成する駆動電流ILED3が減少し、LEDストリング6の輝度が低下してしまう。

【0020】

この問題を解決するためには、フィードバック抵抗RFBの抵抗値を大きくすることが考えられる。しかしながら、抵抗RFBを大きくすると、ラッシュ電流やコイル鳴きなど、別の問題を誘発する。

【0021】

なお以上の考察を、本発明の分野における共通の一般知識の範囲として捉えてはならない。さらに言えば、上記考察自体が、本出願人がはじめて想到したものである。

【0022】

本発明はこうした課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、スキャニング動作時の発光素子の輝度の安定化にある。

【課題を解決するための手段】

【0023】

本発明のある態様は、n個(nは自然数)の発光素子の共通接続された第1端子に駆動電圧を生成するためのDC/DCコンバータを制御するとともに、n個の発光素子それぞれに駆動電流を供給する駆動回路に関する。この駆動回路は、それぞれが発光素子ごとに設けられ、それぞれが対応する発光素子の第2端子と接続されるべき、n個の駆動端子と、それぞれが駆動端子ごとに設けられ、それぞれが対応するパルス調光信号を受け、対応するパルス調光信号がアサートされる期間、対応する駆動端子を介して対応する発光素子に駆動電流を供給する、n個の電流源と、フィードバックキャパシタが接続されるフィードバック端子と、n個の駆動端子それぞれの電圧のうち最も低い電圧と所定の基準電圧の誤差にもとづき、基準電圧の方が高いときに誤差に応じたソース電流を生成し、基準電圧の方が低いときに誤差に応じたシンク電流を生成し、フィードバック端子に生ずるフィードバック電圧を変化させる誤差増幅器と、少なくともフィードバック電圧にもとづいてパルス信号を生成するパルス変調器を含み、パルス信号にもとづき、DC/DCコンバータのスイッチングトランジスタを駆動するDC/DCコンバータ制御部と、を備える。誤差増幅器は、ソース電流とシンク電流の両方を生成可能な第1状態と、ソース電流のみ生成可能な第2状態と、が切りかえ可能に構成される。

【0024】

スキャニング動作時において、フィードバック対象が電圧降下VFの大きなチャンネルから小さなチャンネルに遷移する際に、誤差増幅器を第2状態に設定すると、フィードバック端子から電流が引き抜かれなくなる。つまりフィードバック電圧VFBは、電圧降下VFが最も大きなチャンネルの駆動端子の電位と基準電圧が一致するレベルに安定化されることになる。その結果、スキャニング動作時に、フィードバック電圧が必要以上に低下して出力電圧が低下するのを防止でき、発光素子の輝度を安定化できる。

【0025】

誤差増幅器は、n個の駆動端子それぞれの電圧のうち最も低い電圧と所定の基準電圧の誤差にもとづき、ソース電流およびシンク電流を生成するトランスコンダクタンスアンプと、トランスコンダクタンスアンプの出力端子に接続された入力端子を有する整流素子と、トランスコンダクタンスアンプの出力端子に接続された第1入力端子と、整流素子の出力端子に接続された第2入力端子と、第1状態において第1入力端子と接続され、第2状態において第2入力端子に接続される出力端子と、を有するセレクタと、を含んでもよい。

【0026】

誤差増幅器は、フィードバック電圧が所定のしきい値電圧より高いときに第1状態となってもよい。

フィードバック電圧が高くなりすぎると、出力電圧が高くなり、電流源における損失および発熱が大きくなる。そこでフィードバック電圧がある程度まで高くなったときには、誤差増幅器を第1状態に戻すことにより、フィードバック電圧を低下させることができ、損失や発熱を低減できる。

【0027】

誤差増幅器は、すべてのチャンネルの駆動端子の電位が基準電圧より高くなったときに、第1状態となってもよい。

すべてのチャンネルの駆動端子の電位が基準電圧より高い状態は、電流源における損失が大きく好ましくない。この場合に、誤差増幅器を第1状態とすることにより、複数の駆動端子のうち最も低い電位が基準電圧と一致するようにフィードバックがかかり、損失を低減できる。

【0028】

誤差増幅器は、起動時のソフトスタート動作の完了前において第1状態となってもよい。

起動時にソフトスタート制御を行う場合、駆動端子の電位は、ゼロから基準電圧に向けて上昇していく。つまり起動直後においてフィードバック電圧が最も高くなり、その後フィードバック電圧が低くなっていくはずである。ところが誤差増幅器が第2状態に設定されていると、フィードバック電圧は、起動直後の最も高いレベルを維持し続けるため、出力電圧を目標レベルに保つことができなくなる。この態様によれば、ソフトスタート動作中は、誤差増幅器を第1状態とすることにより、出力電圧を適切に立ち上げることができる。

【0029】

誤差増幅器は、少なくともひとつの駆動端子においてオープン故障が検出されるときに、第1状態となってもよい。

あるチャンネルにおいてオープン故障が発生した場合、そのチャンネルはフィードバック対象から除外される。誤差増幅器を第1状態に設定することにより、故障チャンネルを除くチャンネルの中で、電圧降下が大きいチャンネルを基準として、出力電圧およびフィードバック電圧を最適化することができる。

【0030】

誤差増幅器は、各チャンネルの電流源が生成する駆動電流がその設定値より小さいときに、第1状態となってもよい。

【0031】

ある態様の駆動回路は、ひとつの半導体基板上に一体集積化されてもよい。

「一体集積化」とは、回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが半導体基板の外部に設けられていてもよい。制御回路を1つのICとして集積化することにより、回路面積を削減することができるとともに、回路素子の特性を均一に保つことができる。

【0032】

本発明の別の態様は、発光装置に関する。発光装置は、n個(nは自然数)の発光素子と、n個の発光素子の共通接続された一端に駆動電圧を供給するDC/DCコンバータの出力回路と、DC/DCコンバータを制御するとともに、n個の発光素子それぞれに駆動電流を供給する、上述のいずれかの態様の駆動回路と、を備える。

【0033】

本発明のさらに別の態様は電子機器もしくはディスプレイ装置に関する。電子機器もしくはディスプレイ装置は、液晶パネルと、液晶パネルのバックライトとして設けられた発光装置と、を備える。

【0034】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0035】

本発明のある態様によれば、スキャニング動作時の発光素子の輝度を安定化できる。

【図面の簡単な説明】

【0036】

【図1】本発明者が検討した発光装置の構成を示す回路図である。

【図2】図1の駆動回路のスキャニング動作時の波形図である。

【図3】実施の形態に係る電子機器の構成を示す回路図である。

【図4】誤差増幅器の具体的な構成を示す回路図である。

【図5】図3の駆動回路のスキャニング動作時の波形図である。

【発明を実施するための形態】

【0037】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0038】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0039】

図3は、実施の形態に係る電子機器1の構成を示す回路図である。電子機器1は、ノートPC、デジタルカメラ、デジタルビデオカメラ、携帯電話端末、PDA(Personal Digital Assistant)、ポータブルオーディオプレイヤなどの電池駆動型の機器であり、発光装置2、ホストプロセッサ3、LCD(Liquid Crystal Display)パネル5などを備える。発光装置2はLCDパネル5のバックライトとして設けられる。ホストプロセッサ3は、電子機器1全体を制御するIC(Integrated Circuit)である。

【0040】

発光装置2は、主としてnチャンネルのLEDストリング6_1〜6_nと、駆動回路100と、出力回路102と、を備える。駆動回路100の一部と出力回路102は、入力電圧VINを昇圧し、LEDストリング6の共通に接続された一端(アノード)に駆動電圧VOUTを供給するDC/DCコンバータ4を形成する。

【0041】

出力回路102は、インダクタL1、スイッチングトランジスタM1、整流ダイオードD1、出力キャパシタC1、抵抗R1、R2、検出抵抗Rsを含む。出力回路102のトポロジーは一般的なものであるため説明を省略する。スイッチングトランジスタM1のゲートは、出力端子(OUT端子)と接続され、検出抵抗Rsに生ずる検出信号VCSは、電流検出端子(CS端子)に入力される。

【0042】

駆動回路100は、スイッチングトランジスタM1のオン、オフのデューティ比を制御することにより、駆動電圧VOUTを調節する。具体的には、複数チャンネルのLEDストリング6_1〜6_nそれぞれのカソード端子の電圧VLED1〜VLEDnのうち最も低い電圧が所定の基準電圧VREFと一致するように、スイッチングトランジスタM1のデューティ比をフィードバック制御する。

【0043】

駆動回路100は、ひとつ、あるいは複数の半導体基板上に一体集積化された機能ICであり、n個(nは自然数)のLEDストリング6_1〜6_nの共通接続された第1端子(アノード)に駆動電圧VOUTを供給するDC/DCコンバータ4を制御するとともに、n個のLEDストリング6_1〜6_nそれぞれに駆動電流ILED1〜ILEDnを供給する。「一体集積化」とは、回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが半導体基板の外部に設けられていてもよい。あるいは駆動回路100は、複数の半導体基板に分割して構成されてもよい。

【0044】

駆動回路100は、n個の駆動端子LED1〜LEDn(以下、LED端子ともいう)、n個の電流源CS1〜CSn、誤差増幅器10、論理ゲート12、フィードバック端子FB(以下、FB端子ともいう)、DC/DCコンバータ制御部14、第1スイッチSW1、第2スイッチSW2を備える。

【0045】

n個のLED端子LED1〜LEDnは、それぞれがLEDストリング6_1〜6_nごとに設けられ、i番目のLED端子LEDiは、対応するLEDストリング6_iの第2端子(カソード)と接続される。

【0046】

n個の電流源CS1〜CSnは、それぞれがLED端子LED1〜LEDnごとに設けられる。i番目の電流源CSiは、対応するパルス調光信号PWMiを受け、対応するパルス調光信号PWMiがアサート(本実施の形態においてハイレベル)される期間、対応するLED端子LEDiを介して、対応するLEDストリング6_iに駆動電流ILEDiを供給する。

【0047】

誤差増幅器10は、n個のLED端子LED1〜LEDnそれぞれの電圧VLED1〜VLEDnのうち最も低い電圧と、所定の基準電圧VREFとの誤差を増幅する。FB端子と、外部の接地端子の間には、位相補償用のフィードバックキャパシタCFBおよびフィードバック抵抗RFBが直列に設けられる。誤差増幅器10は、最も低いカソード電圧VLEDと所定の基準電圧VREFの誤差にもとづき、基準電圧VREFの方が高いときに誤差に応じたソース電流ISRCを生成し、基準電圧VREFの方が低いときに誤差に応じたシンク電流ISINKを生成し、FB端子に生ずるフィードバック電圧VFBを変化させる。

【0048】

論理ゲート12は、n個のパルス調光信号PWM1〜PWMnにもとづいて、全チャンネルオフ信号(以下、PWM_ALL_L信号ともいう)を生成する。PWM_ALL_L信号は、すべてのチャンネルのパルス調光信号PWM1〜PWMnがネゲート(本実施の形態においてローレベル)されるときにアサートされる。たとえば論理ゲート12は、n個のパルス調光信号PWM1〜PWMnの否定論理和を生成するNORゲートを含む。

【0049】

第1スイッチSW1および第2スイッチSW2は、PWM_ALL_L信号がアサートされる期間、オフ状態となる。

【0050】

出力回路102の抵抗R1、R2は、駆動電圧VOUTを分圧し、検出電圧VOUT’を生成する。検出電圧VOUT’は、駆動回路100のOVP(過電圧保護)端子に入力される。

【0051】

DC/DCコンバータ制御部14は、パルス変調器20、ドライバ30を含む。パルス変調器20は、少なくともフィードバック電圧VFBにもとづいてパルス信号SPWMを生成する。パルス変調器20は、PWM_ALL_L信号がネゲートされるとき、パルス信号SPWMにもとづき、DC/DCコンバータ4のスイッチングトランジスタM1を駆動する。

パルス変調器20は、PWM_ALL_L信号がアサートされるときに、スイッチングトランジスタM1の駆動を停止する。

【0052】

パルス変調器20は、ピーク電流モードの変調器であり、ソフトスタート回路22、コンパレータ24、ロジック部26、スロープ補償回路28、ドライバ30、を備える。パルス変調器20の構成および動作は、図1を参照して説明した通りである。

【0053】

ソフトスタート回路22は、ホストプロセッサ3からのスタンバイ信号に応答して、時間とともに上昇するソフトスタート電圧VSSを生成する。ソフトスタート電圧VSSの遷移が終了すると、ソフトスタート終了信号(SS_END信号)がアサートされる。

【0054】

コンパレータ24は、スイッチングトランジスタM1に流れる電流IMに応じた検出信号VCSを、フィードバック電圧VFBとソフトスタート電圧VSSのうち低い電圧と比較し、比較結果に応じたオフ信号SOFFを生成する。スロープ補償回路28は、検出信号VCSにスロープ信号VSLOPEを重畳する。

【0055】

ロジック部26は、オフ信号SOFFがアサートされると、パルス信号SPWMを、スイッチングトランジスタM1のオフに対応するレベル(以下、オフレベルという)に遷移させる。また所定のクロック信号と同期して、あるいは所定のオフ時間経過後に、パルス信号SPWMをスイッチングトランジスタM1のオンに対応するレベル(以下、オンレベルという)に遷移させる。

【0056】

ドライバ30は、ロジック部26からのパルス信号SPWMにもとづいてスイッチングトランジスタM1をスイッチングする。

【0057】

誤差増幅器10は、ソース電流ISRCとシンク電流ISINKの両方を生成可能な第1状態φ1と、ソース電流ISRCのみ生成可能な第2状態φ2と、が切りかえ可能に構成される。誤差増幅器10は、第1状態φ1においてフィードバック電圧VFBを上昇、低下させることができ、第2状態φ2ではフィードバック電圧VFBを上昇させることはできるが、低下させることができない。

【0058】

図4は、誤差増幅器10の具体的な構成を示す回路図である。誤差増幅器10は、トランスコンダクタンス(gm)アンプ11と、整流素子D11と、セレクタSEL1、制御部13を含む。

gmアンプ11は、n個のLED端子それぞれの電圧VLED1〜VLEDnのうち最も低い電圧と所定の基準電圧VREFの誤差にもとづき、ソース電流ISRCおよびシンク電流ISINKを生成する。整流素子D11の入力端子は、gmアンプ11の出力端子に接続される。たとえば整流素子D11はダイオードであり、アノードがgmアンプの出力端子と接続される。セレクタSEL1の第1入力端子P1は、gmアンプ11の出力端子と接続され、その第2入力端子P2は、整流素子D11の出力端子(カソード)と接続される。セレクタSEL1の出力端子P3は、第1状態φ1において第1入力端子P1と接続され、第2状態φ2において第2入力端子P2に接続される。

【0059】

制御部13は、駆動回路100およびLEDストリング6の状態に応じて、第1状態φ1と第2状態φ2を切りかえる。

【0060】

制御部13は、通常時には誤差増幅器10を第2状態φ2で動作させ、LEDストリング6の駆動に何らかの異常が生ずる場合、あるいは電流源の損失が大きくなる場合には、誤差増幅器10を第1状態φ1に設定する。

【0061】

たとえば制御部は、以下のいずれかの条件(a)〜(e)の少なくともひとつを満たすときに、異常であるものと判定し、誤差増幅器10を第1状態φ1とし、それ以外のときに第2状態φ2とする。

(a) フィードバック電圧VFBが所定のしきい値電圧VTH1より高いとき

(b) 起動時のソフトスタート動作の完了前

(c) すべてのチャンネルのLED端子の電位VLED1〜VLEDnが基準電圧VREFより高くなったとき

(d) 少なくともひとつのLED端子においてオープン故障が検出されたとき

(e) 各チャンネルの電流源CS1〜CSnが生成する駆動電流ILED1〜ILEDnがその設定値より小さいとき

【0062】

制御部13は、条件(a)〜(e)それぞれに対応するフラグ信号(ステータス信号)FB_CMP、SS_END、LED_ALL_H、LED_OPEN、ILED_OKを受ける。

FB_CMP信号は、条件(a)に対応している。コンパレータ15は、フィードバック電圧VFBを所定のしきい値電圧VTH1と比較し、VFB>VTH1のときにアサートされるFB_CMP信号を生成する。

SS_END信号は、条件(b)に対応しており、ソフトスタートが完了するとアサートされ、ソフトスタート期間中はネゲートされる。SS_END信号は、図3のソフトスタート回路22から出力される。

【0063】

LED_ALL_H信号は、条件(c)に対応しており、すべてのチャンネルのLED端子の電位VLED1〜VLEDnが基準電圧VREFより高くなったときにアサートされる。このLED_ALL_H信号は、基準電圧VREFを、LED端子の電圧VLED1〜VLEDnのうち最も低い電圧と比較するコンパレータよって生成できる。なお、コンパレータ17には、基準電圧VREFよりも高いしきい値電圧VTH2を入力してもよい。

【0064】

LED_OPEN信号は、条件(d)に対応しており、いずれかのチャンネルにおいてオープン故障が検出されるとアサートされる。オープン故障の検出手段は特に限定されず、公知の技術を用いればよい。たとえばオープン故障は、LED端子の電圧VLEDを所定のしきい値電圧VTH3と比較することにより検出できる。

【0065】

ILED_OK信号は、条件(e)に対応しており、すべてのチャンネルの電流源CS1〜CSnが生成する駆動電流ILED1〜ILEDnがその設定値であるときにアサートされ、いずれかのチャンネルの駆動電流ILEDが設定値より低いときにネゲートされる。

【0066】

なお、条件(d)、(e)を満たすことは、回路が異常であることを示すため、本実施の形態では、これらの条件を制御部13の状態制御に考慮している。しかしながら実際には、オープン故障時あるいは駆動電流の不足時には、誤差増幅器10はソース動作となるため、条件(d)、(e)は除外してもよい。

【0067】

制御部13は、SS_END信号、ILED_OK信号を反転した信号#SS_END、#ILED_OK信号と、その他のLED_OPEN信号、FB_CMP信号、LED_ALL_H信号の論理和CNTを生成する論理ゲートOR1を含む。条件(a)〜(e)の少なくともひとつが満たされるとき、論理和CNTがハイレベルとなり、セレクタSEL1は第1状態φ1となり、それ以外のとき論理和CNTはローレベルとなり、セレクタSEL1は第2状態φ2となる。

【0068】

以上が実施の形態に係る駆動回路100の構成である。続いてその動作を説明する。図5は、図3の駆動回路100のスキャニング動作時の波形図である。上から順に、パルス調光信号PWM1、PWM2、PWM3、フィードバック電圧VFB、出力電圧VOUT、全チャンネルの駆動電流の合計ILEDが示される。図2と同様に、n=3チャンネルであり、パルス調光信号PWM1、PWM2、PWM3が120°の位相差でハイレベル(点灯期間)となる。また図2と同様に関係式(1)が成り立つとする。

VF1>VF3>VF2 …(1)

【0069】

誤差増幅器10は第2状態φ2に設定される。時刻t0以前は、第1チャンネルと第2チャンネルが点灯期間であり、第1チャンネルのカソード電圧VLED1が基準電圧VREFと一致するようにフィードバックがかかる。

時刻t0以前、LEDストリング6_1のカソード端子LED1の電位が基準電圧VREFと一致するように出力電圧VOUTが調節される。時刻t0にパルス調光信号PWM1がローレベルとなると、第1チャンネルがフィードバック対象から除外され、第2チャンネルがフィードバック対象となる。

【0070】

VF1>VF2が成り立つため、時刻t0におけるLEDストリング6_2のカソード電圧VLED2は、基準電圧VREFより高くなっている。図1の駆動回路100rでは、誤差増幅器10は、カソード電圧VLED2が基準電圧VREFと一致するように電流を吸い込み、フィードバック電圧VFBが低下するところ、図3の駆動回路100においては誤差増幅器10が第2状態φ2であるため、シンク電流ISINKが流れず、したがってフィードバック電圧VFBは低下せず、時刻t0以前のレベルを維持する。

【0071】

続いて時刻t1において、第3チャンネルが点灯期間となる。これにより、第3チャンネルのカソード電圧VLED3が基準電圧VREFと一致するようにフィードバックがかかる。ところが、誤差増幅器10はシンク電流ISINKを生成できないため、フィードバック電圧VFBは低下せず、もとのレベルを維持する。

以上が駆動回路100の動作である。

【0072】

このように駆動回路100によれば、スキャニング動作時において、フィードバック対象が電圧降下VFの大きなチャンネルから小さなチャンネルに遷移する際に、誤差増幅器10を第2状態φ2に設定することで、FB端子から電流が引き抜かれなくなる。つまりフィードバック電圧VFBは、電圧降下VFが最も大きなチャンネル(図5では第1チャンネル)のLED端子の電位VLED1と基準電圧VREFが一致するレベルに安定化されることになる。

【0073】

その結果、図5に示すように、スキャニング動作時に、フィードバック電圧VFBが必要以上に低下して出力電圧VOUTが低下するのを防止でき、LEDストリング6の輝度を安定化できる。

【0074】

また、誤差増幅器10は、必要に応じて誤差増幅器10を第1状態φ1に設定する。その結果、LEDストリング6の駆動に支障が生じたり、あるいは電流源の損失が大きくなるのを防止できる。

【0075】

たとえばフィードバック電圧VFBが高くなりすぎると、出力電圧VOUTが高くなり、電流源CSにおける損失および発熱が大きくなる。条件(a)に応じて、フィードバック電圧VFBがある程度まで高くなったときには、誤差増幅器10を第1状態φ1に戻すことにより、フィードバック電圧VFBを低下させることができ、損失や発熱を低減できる。

【0076】

また、すべてのチャンネルのLED端子の電位VLED1〜VLEDnが基準電圧VREFより高い状態は、電流源CSにおける損失が大きく好ましくない。そこで条件(b)に応じて誤差増幅器10を第1状態φ1とすることにより、複数のLED端子のうち最も低い電位が基準電圧VREFと一致するようにフィードバックがかかり、損失を低減できる。

【0077】

また、起動時にソフトスタート制御を行う場合、LED端子の電位VLEDは、ゼロから基準電圧VREFに向けて上昇していく。つまり起動直後においてフィードバック電圧VFBが最も高くなり、その後フィードバック電圧VFBが低くなっていくはずである。ところがソフトスタート時に誤差増幅器10が第2状態φ2に設定されていると、フィードバック電圧VFBは、起動直後の最も高いレベルを維持し続けるため、出力電圧VOUTを目標レベルに保つことができなくなる。そこで条件(c)に応じてソフトスタート動作中は、誤差増幅器10を第1状態φ1とすることにより、出力電圧VOUTを適切に立ち上げることができる。

【0078】

また、あるチャンネルにおいてオープン故障が発生した場合、そのチャンネルはフィードバック対象から除外される。このときに誤差増幅器10を第1状態φ1に設定することにより、故障チャンネルを除くチャンネルの中で、電圧降下VFが大きいチャンネルを基準として、出力電圧VOUTおよびフィードバック電圧VFBを最適化することができる。

【0079】

以上、本発明について、実施の形態をもとに説明した。この実施の形態は例示であり、それらの各構成要素や各処理プロセス、それらの組み合わせには、さまざまな変形例が存在しうる。以下、こうした変形例について説明する。

【0080】

第1状態φ1と第2状態φ2を切りかえ可能な誤差増幅器10の構成は図3のそれには限定されない。一般的なgmアンプは、ハイサイドトランジスタとローサイドトランジスタからなるプッシュプル形式の出力段を有する。そしてgmアンプの出力電流IOUTは、出力段のハイサイドトランジスタに流れる電流IHと、ローサイドトランジスタに流れる電流ILの差分で与えられる。

IOUT=IH−IL

そして出力電流IOUTが正のときにソース電流ISRCとなり、負のときにシンク電流ISINKとなる。

【0081】

つまり、IH>ILを満たすように、gmアンプの構成を変更することにより、第2状態φ2を実現できる。これはgmアンプのハイサイドトランジスタ、ローサイドトランジスタの少なくとも一方のバイアス状態を変更したり、ハイサイドトランジスタ、ローサイドトランジスタのサイズを可変とすることにより実現できる。

【0082】

実施の形態では、ピーク電流モードのパルス変調器20を説明したが、パルス変調器20は、平均電流モード、あるいは電圧モードであってもよい。

【0083】

実施の形態ではインダクタを用いた非絶縁型のDC/DCコンバータを説明したが、本発明はトランスを用いた絶縁型のDC/DCコンバータにも適用可能である。

【0084】

実施の形態では、発光装置2のアプリケーションとして電子機器を説明したが、用途は特に限定されず、照明などにも利用できる。

【0085】

また、本実施の形態において、ハイレベル、ローレベルの論理信号の設定は一例であって、インバータなどによって適宜反転させることにより自由に変更することが可能である。

【0086】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0087】

1…電子機器、2…発光装置、3…ホストプロセッサ、4…DC/DCコンバータ、5…LCDパネル、6…LEDストリング、100…駆動回路、102…出力回路、10…誤差増幅器、11…gmアンプ、12…論理ゲート、14…DC/DCコンバータ制御部、20…パルス変調器、22…ソフトスタート回路、24…コンパレータ、26…ロジック部、28…スロープ補償回路、30…ドライバ、L1…インダクタ、C1…出力キャパシタ、D1…整流ダイオード、M1…スイッチングトランジスタ。

【技術分野】

【0001】

本発明は、発光素子の駆動回路に関する。

【背景技術】

【0002】

近年、液晶パネルのバックライトや照明機器として、LED(発光ダイオード)をはじめとする発光素子を利用した発光装置が利用される。図1は、本発明者が検討した発光装置の構成を示す回路図である。発光装置2rは、複数のLEDストリング6_1〜6_nと、その駆動回路100r、出力回路102、ホストプロセッサ3を備える。

【0003】

各LEDストリング6は、直列に接続された複数のLEDを含む。DC/DCコンバータ4rは、入力電圧VINを昇圧してLEDストリング6_1〜6_nの一端に駆動電圧VOUTを供給する。

【0004】

駆動回路100rは、LEDストリング6_1〜6_nごとに設けられた電流源CS1〜CSnを備える。各電流源CSiは、対応するLEDストリング6_iに、目標輝度に応じた駆動電流ILEDiを供給する。

【0005】

駆動回路100rの一部と出力回路102は、DC/DCコンバータ4rを構成する。出力回路102は、インダクタL1、スイッチングトランジスタM1、整流ダイオードD1、出力キャパシタC1、抵抗R1、R2、検出抵抗Rsを含む。駆動回路100rは、スイッチングトランジスタM1のオン、オフのデューティ比を制御することにより、駆動電圧VOUTを調節する。具体的には、複数チャンネルのLEDストリング6_1〜6_nそれぞれのカソード端子の電圧VLED1〜VLEDnのうち最も低い電圧が所定の基準電圧VREFと一致するように、スイッチングトランジスタM1のデューティ比をフィードバック制御する。

【0006】

フィードバック端子(FB端子ともいう)には、位相補償用の抵抗RFBおよびキャパシタCFBが接続される。誤差増幅器10はトランスコンダクタンスアンプであり、カソード端子の電圧VLED1〜VLEDnのうち最も低い電圧が所定の基準電圧VREFの誤差を増幅し、誤差に応じた電流を生成して、フィードバック端子FBにフィードバック電圧VFBを発生させる。

【0007】

DC/DCコンバータ制御部14は、パルス変調器20、ドライバ30を含む。

パルス変調器20は、フィードバック電圧VFBを受け、フィードバック電圧VFBにもとづいて、スイッチングトランジスタM1を駆動するためのパルス信号SPWMを生成する。図1のパルス変調器20は、いわゆるピーク電流モードのパルス幅変調器である。ソフトスタート回路22は、ホストプロセッサ3からのスタンバイ信号に応じて、時間とともに上昇するソフトスタート電圧VSSを生成する。コンパレータ24は、スイッチングトランジスタM1に流れる電流IMに応じた検出信号VCSを、フィードバック電圧VFBとソフトスタート電圧VSSのうち低い電圧と比較し、比較結果に応じたオフ信号SOFFを生成する。スロープ補償回路28は、検出信号VCSにスロープ信号VSLOPEを重畳する。

【0008】

ロジック部26は、オフ信号SOFFがアサートされると、パルス信号SPWMを、スイッチングトランジスタM1のオフに対応するレベル(以下、オフレベルという)に遷移させる。また所定のクロック信号と同期して、あるいは所定のオフ時間経過後に、パルス信号SPWMをスイッチングトランジスタM1のオンに対応するレベル(以下、オンレベルという)に遷移させる。ドライバ30は、ロジック部26からのパルス信号SPWMにもとづいてスイッチングトランジスタM1をスイッチングする。

【0009】

こうした発光装置2rにおいて、LEDストリング6の輝度を調節するために、駆動電流ILEDをPWM(Pulse Width Modulation)制御する場合がある。具体的には、ホストプロセッサ3は、各チャンネルのLEDストリング6の輝度に応じたデューティ比を有するパルス調光信号PWM1〜PWMnを生成する。各チャンネルの電流源CS1〜CSnは、対応するパルス調光信号PWM1〜PWMnにもとづいてスイッチング制御される。このような制御を、バースト調光、バースト制御とも称する。

【0010】

バースト調光を行う場合、あるチャンネルの電流源CSiがオフとなる期間、そのチャンネルのLEDストリング6のカソード端子の電位VLEDiは、ハイレベル電圧にプルアップされて、フィードバックの対象から外される。なぜなら消灯期間のチャンネルのカソード端子VLEDiは、負荷の状態とは無関係のレベルをとるからである。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2008−186668号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

複数チャンネルのLEDストリング6_1〜6_nを、ある位相差で駆動する場合がある。これをスキャニング動作という。このときのパルス調光信号PWM1〜PWMnは、ある位相差を有している。

【0013】

図2は、図1の駆動回路100rのスキャニング動作時の波形図である。上から順に、パルス調光信号PWM1、PWM2、PWM3、フィードバック電圧VFB、出力電圧VOUT、全チャンネルの駆動電流の合計ILEDが示される。n=3チャンネルであり、パルス調光信号PWM1、PWM2、PWM3が120°の位相差でハイレベル(点灯期間)となる。

【0014】

LEDストリング6の電圧降下(順方向電圧)VFは、チャンネルごとにばらつく。図2の波形図は、LEDストリング6_1の電圧降下VF1、LEDストリング6_2の電圧降下VF2、LEDストリング6_3の電圧降下VF3の間に、関係式(1)が成り立つとする。

VF1>VF3>VF2 …(1)

【0015】

時刻t0以前は、第1チャンネルと第2チャンネルが点灯期間であり、第1チャンネルのカソード電圧VLED1が基準電圧VREFと一致するようにフィードバックがかかる。

期間t0−t1は、第2チャンネルが点灯期間であり、第2チャンネルのカソード電圧VLED2が基準電圧VREFと一致するようにフィードバックがかかる。

期間t1−t2は、第2チャンネルと第3チャンネルが点灯期間であり、第3チャンネルのカソード電圧VLED3が基準電圧VREFと一致するようにフィードバックがかかる。

【0016】

また、点灯期間のチャンネルにおいては、以下の関係式(2)が成り立つ。

VOUT=VF1+VLED1=VF2+VLED2=VF3+VLED3 …(2)

【0017】

時刻t0以前、LEDストリング6_1のカソード端子LED1の電位が基準電圧VREFと一致するように出力電圧VOUTが調節される。時刻t0にパルス調光信号PWM1がローレベルとなると、第1チャンネルがフィードバック対象から除外され、第2チャンネルがフィードバック対象となる。

VF1>VF2が成り立つため、時刻t0におけるLEDストリング6_2のカソード電圧VLED2は、基準電圧VREFより高くなっている。このとき誤差増幅器10は、カソード電圧VLED2が基準電圧VREFと一致するように電流を吸い込み(シンク)、フィードバック電圧VFBを低下させ、出力電圧VOUTを低下させる。

【0018】

続いて時刻t1において、第3チャンネルが点灯期間となる。これにより、第3チャンネルのカソード電圧VLED3が基準電圧VREFと一致するようにフィードバックがかかる。

VF3>VF2が成り立つため、時刻t1におけるLEDストリング6_3のカソード電圧VLED3は、基準電圧VREFより低くなっている。したがって誤差増幅器10は、カソード電圧VLED3が基準電圧VREFと一致するように電流を吐き出す(ソース)ことにより、フィードバック電圧VFBを上昇させ、それにより出力電圧VOUTを上昇させようとする。

【0019】

ところがFB端子には、位相補償用のキャパシタCFBおよび抵抗RFBが接続されており、フィードバック電圧VFBは、カソード電圧VLEDと基準電圧VREFの誤差に直ちに追従せず、遅れて変化する。つまり出力電圧VOUTは、時刻t1に直ちに上昇に転ずることなくさらに低下し続け、出力電圧VOUTの変動量が大きくなる。

その結果、時刻t1の直後に、第3チャンネルのカソード端子VLED3が基準電圧VREFを大きく下回って、電流源CS3が生成する駆動電流ILED3が減少し、LEDストリング6の輝度が低下してしまう。

【0020】

この問題を解決するためには、フィードバック抵抗RFBの抵抗値を大きくすることが考えられる。しかしながら、抵抗RFBを大きくすると、ラッシュ電流やコイル鳴きなど、別の問題を誘発する。

【0021】

なお以上の考察を、本発明の分野における共通の一般知識の範囲として捉えてはならない。さらに言えば、上記考察自体が、本出願人がはじめて想到したものである。

【0022】

本発明はこうした課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、スキャニング動作時の発光素子の輝度の安定化にある。

【課題を解決するための手段】

【0023】

本発明のある態様は、n個(nは自然数)の発光素子の共通接続された第1端子に駆動電圧を生成するためのDC/DCコンバータを制御するとともに、n個の発光素子それぞれに駆動電流を供給する駆動回路に関する。この駆動回路は、それぞれが発光素子ごとに設けられ、それぞれが対応する発光素子の第2端子と接続されるべき、n個の駆動端子と、それぞれが駆動端子ごとに設けられ、それぞれが対応するパルス調光信号を受け、対応するパルス調光信号がアサートされる期間、対応する駆動端子を介して対応する発光素子に駆動電流を供給する、n個の電流源と、フィードバックキャパシタが接続されるフィードバック端子と、n個の駆動端子それぞれの電圧のうち最も低い電圧と所定の基準電圧の誤差にもとづき、基準電圧の方が高いときに誤差に応じたソース電流を生成し、基準電圧の方が低いときに誤差に応じたシンク電流を生成し、フィードバック端子に生ずるフィードバック電圧を変化させる誤差増幅器と、少なくともフィードバック電圧にもとづいてパルス信号を生成するパルス変調器を含み、パルス信号にもとづき、DC/DCコンバータのスイッチングトランジスタを駆動するDC/DCコンバータ制御部と、を備える。誤差増幅器は、ソース電流とシンク電流の両方を生成可能な第1状態と、ソース電流のみ生成可能な第2状態と、が切りかえ可能に構成される。

【0024】

スキャニング動作時において、フィードバック対象が電圧降下VFの大きなチャンネルから小さなチャンネルに遷移する際に、誤差増幅器を第2状態に設定すると、フィードバック端子から電流が引き抜かれなくなる。つまりフィードバック電圧VFBは、電圧降下VFが最も大きなチャンネルの駆動端子の電位と基準電圧が一致するレベルに安定化されることになる。その結果、スキャニング動作時に、フィードバック電圧が必要以上に低下して出力電圧が低下するのを防止でき、発光素子の輝度を安定化できる。

【0025】

誤差増幅器は、n個の駆動端子それぞれの電圧のうち最も低い電圧と所定の基準電圧の誤差にもとづき、ソース電流およびシンク電流を生成するトランスコンダクタンスアンプと、トランスコンダクタンスアンプの出力端子に接続された入力端子を有する整流素子と、トランスコンダクタンスアンプの出力端子に接続された第1入力端子と、整流素子の出力端子に接続された第2入力端子と、第1状態において第1入力端子と接続され、第2状態において第2入力端子に接続される出力端子と、を有するセレクタと、を含んでもよい。

【0026】

誤差増幅器は、フィードバック電圧が所定のしきい値電圧より高いときに第1状態となってもよい。

フィードバック電圧が高くなりすぎると、出力電圧が高くなり、電流源における損失および発熱が大きくなる。そこでフィードバック電圧がある程度まで高くなったときには、誤差増幅器を第1状態に戻すことにより、フィードバック電圧を低下させることができ、損失や発熱を低減できる。

【0027】

誤差増幅器は、すべてのチャンネルの駆動端子の電位が基準電圧より高くなったときに、第1状態となってもよい。

すべてのチャンネルの駆動端子の電位が基準電圧より高い状態は、電流源における損失が大きく好ましくない。この場合に、誤差増幅器を第1状態とすることにより、複数の駆動端子のうち最も低い電位が基準電圧と一致するようにフィードバックがかかり、損失を低減できる。

【0028】

誤差増幅器は、起動時のソフトスタート動作の完了前において第1状態となってもよい。

起動時にソフトスタート制御を行う場合、駆動端子の電位は、ゼロから基準電圧に向けて上昇していく。つまり起動直後においてフィードバック電圧が最も高くなり、その後フィードバック電圧が低くなっていくはずである。ところが誤差増幅器が第2状態に設定されていると、フィードバック電圧は、起動直後の最も高いレベルを維持し続けるため、出力電圧を目標レベルに保つことができなくなる。この態様によれば、ソフトスタート動作中は、誤差増幅器を第1状態とすることにより、出力電圧を適切に立ち上げることができる。

【0029】

誤差増幅器は、少なくともひとつの駆動端子においてオープン故障が検出されるときに、第1状態となってもよい。

あるチャンネルにおいてオープン故障が発生した場合、そのチャンネルはフィードバック対象から除外される。誤差増幅器を第1状態に設定することにより、故障チャンネルを除くチャンネルの中で、電圧降下が大きいチャンネルを基準として、出力電圧およびフィードバック電圧を最適化することができる。

【0030】

誤差増幅器は、各チャンネルの電流源が生成する駆動電流がその設定値より小さいときに、第1状態となってもよい。

【0031】

ある態様の駆動回路は、ひとつの半導体基板上に一体集積化されてもよい。

「一体集積化」とは、回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが半導体基板の外部に設けられていてもよい。制御回路を1つのICとして集積化することにより、回路面積を削減することができるとともに、回路素子の特性を均一に保つことができる。

【0032】

本発明の別の態様は、発光装置に関する。発光装置は、n個(nは自然数)の発光素子と、n個の発光素子の共通接続された一端に駆動電圧を供給するDC/DCコンバータの出力回路と、DC/DCコンバータを制御するとともに、n個の発光素子それぞれに駆動電流を供給する、上述のいずれかの態様の駆動回路と、を備える。

【0033】

本発明のさらに別の態様は電子機器もしくはディスプレイ装置に関する。電子機器もしくはディスプレイ装置は、液晶パネルと、液晶パネルのバックライトとして設けられた発光装置と、を備える。

【0034】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0035】

本発明のある態様によれば、スキャニング動作時の発光素子の輝度を安定化できる。

【図面の簡単な説明】

【0036】

【図1】本発明者が検討した発光装置の構成を示す回路図である。

【図2】図1の駆動回路のスキャニング動作時の波形図である。

【図3】実施の形態に係る電子機器の構成を示す回路図である。

【図4】誤差増幅器の具体的な構成を示す回路図である。

【図5】図3の駆動回路のスキャニング動作時の波形図である。

【発明を実施するための形態】

【0037】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0038】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0039】

図3は、実施の形態に係る電子機器1の構成を示す回路図である。電子機器1は、ノートPC、デジタルカメラ、デジタルビデオカメラ、携帯電話端末、PDA(Personal Digital Assistant)、ポータブルオーディオプレイヤなどの電池駆動型の機器であり、発光装置2、ホストプロセッサ3、LCD(Liquid Crystal Display)パネル5などを備える。発光装置2はLCDパネル5のバックライトとして設けられる。ホストプロセッサ3は、電子機器1全体を制御するIC(Integrated Circuit)である。

【0040】

発光装置2は、主としてnチャンネルのLEDストリング6_1〜6_nと、駆動回路100と、出力回路102と、を備える。駆動回路100の一部と出力回路102は、入力電圧VINを昇圧し、LEDストリング6の共通に接続された一端(アノード)に駆動電圧VOUTを供給するDC/DCコンバータ4を形成する。

【0041】

出力回路102は、インダクタL1、スイッチングトランジスタM1、整流ダイオードD1、出力キャパシタC1、抵抗R1、R2、検出抵抗Rsを含む。出力回路102のトポロジーは一般的なものであるため説明を省略する。スイッチングトランジスタM1のゲートは、出力端子(OUT端子)と接続され、検出抵抗Rsに生ずる検出信号VCSは、電流検出端子(CS端子)に入力される。

【0042】

駆動回路100は、スイッチングトランジスタM1のオン、オフのデューティ比を制御することにより、駆動電圧VOUTを調節する。具体的には、複数チャンネルのLEDストリング6_1〜6_nそれぞれのカソード端子の電圧VLED1〜VLEDnのうち最も低い電圧が所定の基準電圧VREFと一致するように、スイッチングトランジスタM1のデューティ比をフィードバック制御する。

【0043】

駆動回路100は、ひとつ、あるいは複数の半導体基板上に一体集積化された機能ICであり、n個(nは自然数)のLEDストリング6_1〜6_nの共通接続された第1端子(アノード)に駆動電圧VOUTを供給するDC/DCコンバータ4を制御するとともに、n個のLEDストリング6_1〜6_nそれぞれに駆動電流ILED1〜ILEDnを供給する。「一体集積化」とは、回路の構成要素のすべてが半導体基板上に形成される場合や、回路の主要構成要素が一体集積化される場合が含まれ、回路定数の調節用に一部の抵抗やキャパシタなどが半導体基板の外部に設けられていてもよい。あるいは駆動回路100は、複数の半導体基板に分割して構成されてもよい。

【0044】

駆動回路100は、n個の駆動端子LED1〜LEDn(以下、LED端子ともいう)、n個の電流源CS1〜CSn、誤差増幅器10、論理ゲート12、フィードバック端子FB(以下、FB端子ともいう)、DC/DCコンバータ制御部14、第1スイッチSW1、第2スイッチSW2を備える。

【0045】

n個のLED端子LED1〜LEDnは、それぞれがLEDストリング6_1〜6_nごとに設けられ、i番目のLED端子LEDiは、対応するLEDストリング6_iの第2端子(カソード)と接続される。

【0046】

n個の電流源CS1〜CSnは、それぞれがLED端子LED1〜LEDnごとに設けられる。i番目の電流源CSiは、対応するパルス調光信号PWMiを受け、対応するパルス調光信号PWMiがアサート(本実施の形態においてハイレベル)される期間、対応するLED端子LEDiを介して、対応するLEDストリング6_iに駆動電流ILEDiを供給する。

【0047】

誤差増幅器10は、n個のLED端子LED1〜LEDnそれぞれの電圧VLED1〜VLEDnのうち最も低い電圧と、所定の基準電圧VREFとの誤差を増幅する。FB端子と、外部の接地端子の間には、位相補償用のフィードバックキャパシタCFBおよびフィードバック抵抗RFBが直列に設けられる。誤差増幅器10は、最も低いカソード電圧VLEDと所定の基準電圧VREFの誤差にもとづき、基準電圧VREFの方が高いときに誤差に応じたソース電流ISRCを生成し、基準電圧VREFの方が低いときに誤差に応じたシンク電流ISINKを生成し、FB端子に生ずるフィードバック電圧VFBを変化させる。

【0048】

論理ゲート12は、n個のパルス調光信号PWM1〜PWMnにもとづいて、全チャンネルオフ信号(以下、PWM_ALL_L信号ともいう)を生成する。PWM_ALL_L信号は、すべてのチャンネルのパルス調光信号PWM1〜PWMnがネゲート(本実施の形態においてローレベル)されるときにアサートされる。たとえば論理ゲート12は、n個のパルス調光信号PWM1〜PWMnの否定論理和を生成するNORゲートを含む。

【0049】

第1スイッチSW1および第2スイッチSW2は、PWM_ALL_L信号がアサートされる期間、オフ状態となる。

【0050】

出力回路102の抵抗R1、R2は、駆動電圧VOUTを分圧し、検出電圧VOUT’を生成する。検出電圧VOUT’は、駆動回路100のOVP(過電圧保護)端子に入力される。

【0051】

DC/DCコンバータ制御部14は、パルス変調器20、ドライバ30を含む。パルス変調器20は、少なくともフィードバック電圧VFBにもとづいてパルス信号SPWMを生成する。パルス変調器20は、PWM_ALL_L信号がネゲートされるとき、パルス信号SPWMにもとづき、DC/DCコンバータ4のスイッチングトランジスタM1を駆動する。

パルス変調器20は、PWM_ALL_L信号がアサートされるときに、スイッチングトランジスタM1の駆動を停止する。

【0052】

パルス変調器20は、ピーク電流モードの変調器であり、ソフトスタート回路22、コンパレータ24、ロジック部26、スロープ補償回路28、ドライバ30、を備える。パルス変調器20の構成および動作は、図1を参照して説明した通りである。

【0053】

ソフトスタート回路22は、ホストプロセッサ3からのスタンバイ信号に応答して、時間とともに上昇するソフトスタート電圧VSSを生成する。ソフトスタート電圧VSSの遷移が終了すると、ソフトスタート終了信号(SS_END信号)がアサートされる。

【0054】

コンパレータ24は、スイッチングトランジスタM1に流れる電流IMに応じた検出信号VCSを、フィードバック電圧VFBとソフトスタート電圧VSSのうち低い電圧と比較し、比較結果に応じたオフ信号SOFFを生成する。スロープ補償回路28は、検出信号VCSにスロープ信号VSLOPEを重畳する。

【0055】

ロジック部26は、オフ信号SOFFがアサートされると、パルス信号SPWMを、スイッチングトランジスタM1のオフに対応するレベル(以下、オフレベルという)に遷移させる。また所定のクロック信号と同期して、あるいは所定のオフ時間経過後に、パルス信号SPWMをスイッチングトランジスタM1のオンに対応するレベル(以下、オンレベルという)に遷移させる。

【0056】

ドライバ30は、ロジック部26からのパルス信号SPWMにもとづいてスイッチングトランジスタM1をスイッチングする。

【0057】

誤差増幅器10は、ソース電流ISRCとシンク電流ISINKの両方を生成可能な第1状態φ1と、ソース電流ISRCのみ生成可能な第2状態φ2と、が切りかえ可能に構成される。誤差増幅器10は、第1状態φ1においてフィードバック電圧VFBを上昇、低下させることができ、第2状態φ2ではフィードバック電圧VFBを上昇させることはできるが、低下させることができない。

【0058】

図4は、誤差増幅器10の具体的な構成を示す回路図である。誤差増幅器10は、トランスコンダクタンス(gm)アンプ11と、整流素子D11と、セレクタSEL1、制御部13を含む。

gmアンプ11は、n個のLED端子それぞれの電圧VLED1〜VLEDnのうち最も低い電圧と所定の基準電圧VREFの誤差にもとづき、ソース電流ISRCおよびシンク電流ISINKを生成する。整流素子D11の入力端子は、gmアンプ11の出力端子に接続される。たとえば整流素子D11はダイオードであり、アノードがgmアンプの出力端子と接続される。セレクタSEL1の第1入力端子P1は、gmアンプ11の出力端子と接続され、その第2入力端子P2は、整流素子D11の出力端子(カソード)と接続される。セレクタSEL1の出力端子P3は、第1状態φ1において第1入力端子P1と接続され、第2状態φ2において第2入力端子P2に接続される。

【0059】

制御部13は、駆動回路100およびLEDストリング6の状態に応じて、第1状態φ1と第2状態φ2を切りかえる。

【0060】

制御部13は、通常時には誤差増幅器10を第2状態φ2で動作させ、LEDストリング6の駆動に何らかの異常が生ずる場合、あるいは電流源の損失が大きくなる場合には、誤差増幅器10を第1状態φ1に設定する。

【0061】

たとえば制御部は、以下のいずれかの条件(a)〜(e)の少なくともひとつを満たすときに、異常であるものと判定し、誤差増幅器10を第1状態φ1とし、それ以外のときに第2状態φ2とする。

(a) フィードバック電圧VFBが所定のしきい値電圧VTH1より高いとき

(b) 起動時のソフトスタート動作の完了前

(c) すべてのチャンネルのLED端子の電位VLED1〜VLEDnが基準電圧VREFより高くなったとき

(d) 少なくともひとつのLED端子においてオープン故障が検出されたとき

(e) 各チャンネルの電流源CS1〜CSnが生成する駆動電流ILED1〜ILEDnがその設定値より小さいとき

【0062】

制御部13は、条件(a)〜(e)それぞれに対応するフラグ信号(ステータス信号)FB_CMP、SS_END、LED_ALL_H、LED_OPEN、ILED_OKを受ける。

FB_CMP信号は、条件(a)に対応している。コンパレータ15は、フィードバック電圧VFBを所定のしきい値電圧VTH1と比較し、VFB>VTH1のときにアサートされるFB_CMP信号を生成する。

SS_END信号は、条件(b)に対応しており、ソフトスタートが完了するとアサートされ、ソフトスタート期間中はネゲートされる。SS_END信号は、図3のソフトスタート回路22から出力される。

【0063】

LED_ALL_H信号は、条件(c)に対応しており、すべてのチャンネルのLED端子の電位VLED1〜VLEDnが基準電圧VREFより高くなったときにアサートされる。このLED_ALL_H信号は、基準電圧VREFを、LED端子の電圧VLED1〜VLEDnのうち最も低い電圧と比較するコンパレータよって生成できる。なお、コンパレータ17には、基準電圧VREFよりも高いしきい値電圧VTH2を入力してもよい。

【0064】

LED_OPEN信号は、条件(d)に対応しており、いずれかのチャンネルにおいてオープン故障が検出されるとアサートされる。オープン故障の検出手段は特に限定されず、公知の技術を用いればよい。たとえばオープン故障は、LED端子の電圧VLEDを所定のしきい値電圧VTH3と比較することにより検出できる。

【0065】

ILED_OK信号は、条件(e)に対応しており、すべてのチャンネルの電流源CS1〜CSnが生成する駆動電流ILED1〜ILEDnがその設定値であるときにアサートされ、いずれかのチャンネルの駆動電流ILEDが設定値より低いときにネゲートされる。

【0066】

なお、条件(d)、(e)を満たすことは、回路が異常であることを示すため、本実施の形態では、これらの条件を制御部13の状態制御に考慮している。しかしながら実際には、オープン故障時あるいは駆動電流の不足時には、誤差増幅器10はソース動作となるため、条件(d)、(e)は除外してもよい。

【0067】

制御部13は、SS_END信号、ILED_OK信号を反転した信号#SS_END、#ILED_OK信号と、その他のLED_OPEN信号、FB_CMP信号、LED_ALL_H信号の論理和CNTを生成する論理ゲートOR1を含む。条件(a)〜(e)の少なくともひとつが満たされるとき、論理和CNTがハイレベルとなり、セレクタSEL1は第1状態φ1となり、それ以外のとき論理和CNTはローレベルとなり、セレクタSEL1は第2状態φ2となる。

【0068】

以上が実施の形態に係る駆動回路100の構成である。続いてその動作を説明する。図5は、図3の駆動回路100のスキャニング動作時の波形図である。上から順に、パルス調光信号PWM1、PWM2、PWM3、フィードバック電圧VFB、出力電圧VOUT、全チャンネルの駆動電流の合計ILEDが示される。図2と同様に、n=3チャンネルであり、パルス調光信号PWM1、PWM2、PWM3が120°の位相差でハイレベル(点灯期間)となる。また図2と同様に関係式(1)が成り立つとする。

VF1>VF3>VF2 …(1)

【0069】

誤差増幅器10は第2状態φ2に設定される。時刻t0以前は、第1チャンネルと第2チャンネルが点灯期間であり、第1チャンネルのカソード電圧VLED1が基準電圧VREFと一致するようにフィードバックがかかる。

時刻t0以前、LEDストリング6_1のカソード端子LED1の電位が基準電圧VREFと一致するように出力電圧VOUTが調節される。時刻t0にパルス調光信号PWM1がローレベルとなると、第1チャンネルがフィードバック対象から除外され、第2チャンネルがフィードバック対象となる。

【0070】

VF1>VF2が成り立つため、時刻t0におけるLEDストリング6_2のカソード電圧VLED2は、基準電圧VREFより高くなっている。図1の駆動回路100rでは、誤差増幅器10は、カソード電圧VLED2が基準電圧VREFと一致するように電流を吸い込み、フィードバック電圧VFBが低下するところ、図3の駆動回路100においては誤差増幅器10が第2状態φ2であるため、シンク電流ISINKが流れず、したがってフィードバック電圧VFBは低下せず、時刻t0以前のレベルを維持する。

【0071】

続いて時刻t1において、第3チャンネルが点灯期間となる。これにより、第3チャンネルのカソード電圧VLED3が基準電圧VREFと一致するようにフィードバックがかかる。ところが、誤差増幅器10はシンク電流ISINKを生成できないため、フィードバック電圧VFBは低下せず、もとのレベルを維持する。

以上が駆動回路100の動作である。

【0072】

このように駆動回路100によれば、スキャニング動作時において、フィードバック対象が電圧降下VFの大きなチャンネルから小さなチャンネルに遷移する際に、誤差増幅器10を第2状態φ2に設定することで、FB端子から電流が引き抜かれなくなる。つまりフィードバック電圧VFBは、電圧降下VFが最も大きなチャンネル(図5では第1チャンネル)のLED端子の電位VLED1と基準電圧VREFが一致するレベルに安定化されることになる。

【0073】

その結果、図5に示すように、スキャニング動作時に、フィードバック電圧VFBが必要以上に低下して出力電圧VOUTが低下するのを防止でき、LEDストリング6の輝度を安定化できる。

【0074】

また、誤差増幅器10は、必要に応じて誤差増幅器10を第1状態φ1に設定する。その結果、LEDストリング6の駆動に支障が生じたり、あるいは電流源の損失が大きくなるのを防止できる。

【0075】

たとえばフィードバック電圧VFBが高くなりすぎると、出力電圧VOUTが高くなり、電流源CSにおける損失および発熱が大きくなる。条件(a)に応じて、フィードバック電圧VFBがある程度まで高くなったときには、誤差増幅器10を第1状態φ1に戻すことにより、フィードバック電圧VFBを低下させることができ、損失や発熱を低減できる。

【0076】

また、すべてのチャンネルのLED端子の電位VLED1〜VLEDnが基準電圧VREFより高い状態は、電流源CSにおける損失が大きく好ましくない。そこで条件(b)に応じて誤差増幅器10を第1状態φ1とすることにより、複数のLED端子のうち最も低い電位が基準電圧VREFと一致するようにフィードバックがかかり、損失を低減できる。

【0077】

また、起動時にソフトスタート制御を行う場合、LED端子の電位VLEDは、ゼロから基準電圧VREFに向けて上昇していく。つまり起動直後においてフィードバック電圧VFBが最も高くなり、その後フィードバック電圧VFBが低くなっていくはずである。ところがソフトスタート時に誤差増幅器10が第2状態φ2に設定されていると、フィードバック電圧VFBは、起動直後の最も高いレベルを維持し続けるため、出力電圧VOUTを目標レベルに保つことができなくなる。そこで条件(c)に応じてソフトスタート動作中は、誤差増幅器10を第1状態φ1とすることにより、出力電圧VOUTを適切に立ち上げることができる。

【0078】

また、あるチャンネルにおいてオープン故障が発生した場合、そのチャンネルはフィードバック対象から除外される。このときに誤差増幅器10を第1状態φ1に設定することにより、故障チャンネルを除くチャンネルの中で、電圧降下VFが大きいチャンネルを基準として、出力電圧VOUTおよびフィードバック電圧VFBを最適化することができる。

【0079】

以上、本発明について、実施の形態をもとに説明した。この実施の形態は例示であり、それらの各構成要素や各処理プロセス、それらの組み合わせには、さまざまな変形例が存在しうる。以下、こうした変形例について説明する。

【0080】

第1状態φ1と第2状態φ2を切りかえ可能な誤差増幅器10の構成は図3のそれには限定されない。一般的なgmアンプは、ハイサイドトランジスタとローサイドトランジスタからなるプッシュプル形式の出力段を有する。そしてgmアンプの出力電流IOUTは、出力段のハイサイドトランジスタに流れる電流IHと、ローサイドトランジスタに流れる電流ILの差分で与えられる。

IOUT=IH−IL

そして出力電流IOUTが正のときにソース電流ISRCとなり、負のときにシンク電流ISINKとなる。

【0081】

つまり、IH>ILを満たすように、gmアンプの構成を変更することにより、第2状態φ2を実現できる。これはgmアンプのハイサイドトランジスタ、ローサイドトランジスタの少なくとも一方のバイアス状態を変更したり、ハイサイドトランジスタ、ローサイドトランジスタのサイズを可変とすることにより実現できる。

【0082】

実施の形態では、ピーク電流モードのパルス変調器20を説明したが、パルス変調器20は、平均電流モード、あるいは電圧モードであってもよい。

【0083】

実施の形態ではインダクタを用いた非絶縁型のDC/DCコンバータを説明したが、本発明はトランスを用いた絶縁型のDC/DCコンバータにも適用可能である。

【0084】

実施の形態では、発光装置2のアプリケーションとして電子機器を説明したが、用途は特に限定されず、照明などにも利用できる。

【0085】

また、本実施の形態において、ハイレベル、ローレベルの論理信号の設定は一例であって、インバータなどによって適宜反転させることにより自由に変更することが可能である。

【0086】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0087】

1…電子機器、2…発光装置、3…ホストプロセッサ、4…DC/DCコンバータ、5…LCDパネル、6…LEDストリング、100…駆動回路、102…出力回路、10…誤差増幅器、11…gmアンプ、12…論理ゲート、14…DC/DCコンバータ制御部、20…パルス変調器、22…ソフトスタート回路、24…コンパレータ、26…ロジック部、28…スロープ補償回路、30…ドライバ、L1…インダクタ、C1…出力キャパシタ、D1…整流ダイオード、M1…スイッチングトランジスタ。

【特許請求の範囲】

【請求項1】

n個(nは自然数)の発光素子の共通接続された第1端子に駆動電圧を生成するためのDC/DCコンバータを制御するとともに、前記n個の発光素子それぞれに駆動電流を供給する駆動回路であって、

それぞれが前記発光素子ごとに設けられ、それぞれが対応する前記発光素子の第2端子と接続されるべき、n個の駆動端子と、

それぞれが前記駆動端子ごとに設けられ、それぞれが対応するパルス調光信号を受け、対応するパルス調光信号がアサートされる期間、対応する前記駆動端子を介して対応する前記発光素子に駆動電流を供給する、n個の電流源と、

フィードバックキャパシタが接続されるフィードバック端子と、

前記n個の駆動端子それぞれの電圧のうち最も低い電圧と所定の基準電圧の誤差にもとづき、前記基準電圧の方が高いときに前記誤差に応じたソース電流を生成し、前記基準電圧の方が低いときに前記誤差に応じたシンク電流を生成し、フィードバック端子に生ずるフィードバック電圧を変化させる誤差増幅器と、

少なくとも前記フィードバック電圧にもとづいてパルス信号を生成するパルス変調器を含み、前記パルス信号にもとづき、前記DC/DCコンバータのスイッチングトランジスタを駆動するDC/DCコンバータ制御部と、

を備え、

前記誤差増幅器は、前記ソース電流と前記シンク電流の両方を生成可能な第1状態と、前記ソース電流のみ生成可能な第2状態と、が切りかえ可能に構成されることを特徴とする駆動回路。

【請求項2】

前記誤差増幅器は、

前記n個の駆動端子それぞれの電圧のうち最も低い電圧と所定の基準電圧の誤差にもとづき、前記ソース電流および前記シンク電流を生成するトランスコンダクタンスアンプと、

前記トランスコンダクタンスアンプの出力端子に接続された入力端子を有する整流素子と、

前記トランスコンダクタンスアンプの出力端子に接続された第1入力端子と、前記整流素子の出力端子に接続された第2入力端子と、前記第1状態において前記第1入力端子と接続され、前記第2状態において前記第2入力端子に接続される出力端子と、を有するセレクタと、

を含むことを特徴とする請求項1に記載の駆動回路。

【請求項3】

前記誤差増幅器は、前記フィードバック電圧が所定のしきい値電圧より高いときに前記第1状態となることを特徴とする請求項1または2に記載の駆動回路。

【請求項4】

前記誤差増幅器は、起動時のソフトスタート動作の完了前において前記第1状態となることを特徴とする請求項1から3のいずれかに記載の駆動回路。

【請求項5】

前記誤差増幅器は、すべてのチャンネルの駆動端子の電位が前記基準電圧より高くなったときに、前記第1状態となることを特徴とする請求項1から4のいずれかに記載の駆動回路。

【請求項6】

前記誤差増幅器は、少なくともひとつの駆動端子においてオープン故障が検出されるときに、前記第1状態となることを特徴とする請求項1から5のいずれかに記載の駆動回路。

【請求項7】

前記誤差増幅器は、各チャンネルの電流源が生成する駆動電流がその設定値より小さいときに、前記第1状態となることを特徴とする請求項1から5のいずれかに記載の駆動回路。

【請求項8】

ひとつの半導体基板上に一体集積化されることを特徴とする請求項1から7のいずれかに記載の駆動回路。

【請求項9】

n個(nは自然数)の発光素子と、

前記n個の発光素子の共通接続された一端に駆動電圧を供給するDC/DCコンバータの出力回路と、

前記DC/DCコンバータを制御するとともに、前記n個の発光素子それぞれに駆動電流を供給する、請求項1から8のいずれかに記載の駆動回路と、

を備えることを特徴とする発光装置。

【請求項10】

液晶パネルと、

前記液晶パネルのバックライトとして設けられた請求項9に記載の発光装置と、

を備えることを特徴とする電子機器。

【請求項1】

n個(nは自然数)の発光素子の共通接続された第1端子に駆動電圧を生成するためのDC/DCコンバータを制御するとともに、前記n個の発光素子それぞれに駆動電流を供給する駆動回路であって、

それぞれが前記発光素子ごとに設けられ、それぞれが対応する前記発光素子の第2端子と接続されるべき、n個の駆動端子と、

それぞれが前記駆動端子ごとに設けられ、それぞれが対応するパルス調光信号を受け、対応するパルス調光信号がアサートされる期間、対応する前記駆動端子を介して対応する前記発光素子に駆動電流を供給する、n個の電流源と、

フィードバックキャパシタが接続されるフィードバック端子と、

前記n個の駆動端子それぞれの電圧のうち最も低い電圧と所定の基準電圧の誤差にもとづき、前記基準電圧の方が高いときに前記誤差に応じたソース電流を生成し、前記基準電圧の方が低いときに前記誤差に応じたシンク電流を生成し、フィードバック端子に生ずるフィードバック電圧を変化させる誤差増幅器と、

少なくとも前記フィードバック電圧にもとづいてパルス信号を生成するパルス変調器を含み、前記パルス信号にもとづき、前記DC/DCコンバータのスイッチングトランジスタを駆動するDC/DCコンバータ制御部と、

を備え、

前記誤差増幅器は、前記ソース電流と前記シンク電流の両方を生成可能な第1状態と、前記ソース電流のみ生成可能な第2状態と、が切りかえ可能に構成されることを特徴とする駆動回路。

【請求項2】

前記誤差増幅器は、

前記n個の駆動端子それぞれの電圧のうち最も低い電圧と所定の基準電圧の誤差にもとづき、前記ソース電流および前記シンク電流を生成するトランスコンダクタンスアンプと、

前記トランスコンダクタンスアンプの出力端子に接続された入力端子を有する整流素子と、

前記トランスコンダクタンスアンプの出力端子に接続された第1入力端子と、前記整流素子の出力端子に接続された第2入力端子と、前記第1状態において前記第1入力端子と接続され、前記第2状態において前記第2入力端子に接続される出力端子と、を有するセレクタと、

を含むことを特徴とする請求項1に記載の駆動回路。

【請求項3】

前記誤差増幅器は、前記フィードバック電圧が所定のしきい値電圧より高いときに前記第1状態となることを特徴とする請求項1または2に記載の駆動回路。

【請求項4】

前記誤差増幅器は、起動時のソフトスタート動作の完了前において前記第1状態となることを特徴とする請求項1から3のいずれかに記載の駆動回路。

【請求項5】

前記誤差増幅器は、すべてのチャンネルの駆動端子の電位が前記基準電圧より高くなったときに、前記第1状態となることを特徴とする請求項1から4のいずれかに記載の駆動回路。

【請求項6】

前記誤差増幅器は、少なくともひとつの駆動端子においてオープン故障が検出されるときに、前記第1状態となることを特徴とする請求項1から5のいずれかに記載の駆動回路。

【請求項7】

前記誤差増幅器は、各チャンネルの電流源が生成する駆動電流がその設定値より小さいときに、前記第1状態となることを特徴とする請求項1から5のいずれかに記載の駆動回路。

【請求項8】

ひとつの半導体基板上に一体集積化されることを特徴とする請求項1から7のいずれかに記載の駆動回路。

【請求項9】

n個(nは自然数)の発光素子と、

前記n個の発光素子の共通接続された一端に駆動電圧を供給するDC/DCコンバータの出力回路と、

前記DC/DCコンバータを制御するとともに、前記n個の発光素子それぞれに駆動電流を供給する、請求項1から8のいずれかに記載の駆動回路と、

を備えることを特徴とする発光装置。

【請求項10】

液晶パネルと、

前記液晶パネルのバックライトとして設けられた請求項9に記載の発光装置と、

を備えることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−109921(P2013−109921A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253078(P2011−253078)

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月18日(2011.11.18)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]