電圧比較装置、電子システム

【課題】入力電圧の電圧降下に対応した電圧比較装置を提供する。

【解決手段】本発明の電圧比較装置は、所定の基準電圧VREFと入力電圧VCCINとを比較して、入力電圧VCCINが基準電圧VREFよりも低い場合に第1状態になり、入力電圧VCCINが基準電圧VREFよりも高い場合に第2状態になる検知信号VCCOKを出力する比較器2と、入力電圧VCCINの候補となる複数の候補電圧V1〜V5を出力可能とし、検知信号VCCOKが第1状態の場合に入力電圧VCCINよりも低い候補電圧を入力電圧VCCINとして比較器2へ出力し、検知信号VCCINが第2状態の場合に入力電圧VCCINよりも高い候補電圧を入力電圧VCCINとして比較器2へ出力する入力電圧生成回路3とを備える。

【解決手段】本発明の電圧比較装置は、所定の基準電圧VREFと入力電圧VCCINとを比較して、入力電圧VCCINが基準電圧VREFよりも低い場合に第1状態になり、入力電圧VCCINが基準電圧VREFよりも高い場合に第2状態になる検知信号VCCOKを出力する比較器2と、入力電圧VCCINの候補となる複数の候補電圧V1〜V5を出力可能とし、検知信号VCCOKが第1状態の場合に入力電圧VCCINよりも低い候補電圧を入力電圧VCCINとして比較器2へ出力し、検知信号VCCINが第2状態の場合に入力電圧VCCINよりも高い候補電圧を入力電圧VCCINとして比較器2へ出力する入力電圧生成回路3とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メモリなどの大量の素子を備えた半導体装置に印加される電源電圧を基準電圧と比較して、電源電圧が基準電圧よりも高電圧か否かを検知する電圧比較装置、及びこのような電圧比較装置を備えた電子システムに関する。

【背景技術】

【0002】

従来の電圧比較装置として、例えば半導体装置に入力される電源電圧と所定の基準電圧とを比較して、電源電圧が半導体装置の正常動作に充分な電圧であるかを検知するものがある。検知結果を表す検知信号は、例えば半導体装置のロックアウト(lockout)信号として用いることができる。ロックアウト信号により、電源電圧が正常動作に充分であれば半導体装置が動作状態になり、電源電圧が正常動作に不充分であれば半導体装置が非動作状態になる。

【0003】

電源電圧は、フラッシュメモリなどのように大量の素子を有する半導体装置に印加される場合に、不安定な動きになることがある。例えば、ロックアウト信号により半導体装置が動作状態になると、負荷が急激に増加するために、電源電圧が降下する。電源電圧が基準電圧以上になると半導体装置が動作状態になるので、このような電圧降下は、電源電圧が基準電圧以上になった直後に発生する。電圧降下により、電源電圧が再び基準電圧以下になる。電圧比較装置がこれを検知すると、ロックアウト信号がすぐに切り替わる。これにより、半導体装置は動作状態になった直後に非動作状態になり、動作が不安定になって半導体装置の誤動作の原因になる。同様のことは、電源電圧を下げて半導体装置を非動作状態にする場合にも発生する。

【0004】

このような電源電圧による半導体装置の不安定動作を防止するために、特許文献1、2の発明が提案されている。特許文献1、2には、基準電圧を2種類用意しておき、これを切り換えて用いる技術が記載されている。特許文献1、2では、電源電圧が基準電圧以上になると基準電圧を下げる。これにより、電源電圧の電圧降下があっても、電源電圧が基準電圧以下になることを防止して検知信号が切り替わらないようになっている。

【特許文献1】特開2005−141811号公報

【特許文献2】特開2007−306648号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

特許文献1、2の発明では、基準電圧は予め決められた2種類しか取ることができない。そのために、電源電圧の電圧降下が予想以上であれば、上記の問題を解決することができず、半導体装置の動作を安定させることができない。

【0006】

本発明は、このような問題に鑑みて、電源電圧のような入力電圧の電圧降下及び電圧上昇に対応した電圧比較装置を提供することを主たる課題とする。

【課題を解決するための手段】

【0007】

以上の課題を解決する本発明の電圧比較装置は、所定の基準電圧と入力電圧とを比較して、前記入力電圧が前記基準電圧よりも低い場合に第1状態になり、前記入力電圧が前記基準電圧よりも高い場合に第2状態になる検知信号を出力する比較器と、前記入力電圧の候補となる複数の候補電圧を出力可能とし、前記検知信号が前記第1状態の場合は前記複数の候補電圧のうち前記入力電圧よりも低い候補電圧を新たな入力電圧として前記比較器へ出力し、前記検知信号が前記第2状態の場合は前記複数の候補電圧のうち前記入力電圧よりも高い候補電圧を新たな入力電圧として前記比較器へ出力する入力電圧生成回路と、を備える。

【0008】

従来のこの種の電圧比較装置は、上述の通り、基準電圧よりも電源電圧が高くなった場合に基準電圧を下げて、電源電圧の電圧降下があっても、電源電圧が基準電圧より低くなることを防止している。

本発明の電圧比較装置は、従来とは逆に、入力電圧が基準電圧よりも高い場合に入力電圧をさらに高くする。これにより入力電圧が電源電圧と同様に電圧降下があっても、基準電圧以下になることを防止できる。また、入力電圧が基準電圧よりも低い場合に入力電圧をさらに低くする。これにより入力電圧に電圧上昇があっても、基準電圧以上になることを防止できる。

【0009】

本発明では、前記入力電圧生成回路が、例えば、電源電圧を分圧して前記複数の候補電圧を出力する分圧回路と、前記検知信号が前記第1状態の場合に、最も低電圧の候補電圧を出力し、前記検知信号が前記第2状態の場合に、残りの候補電圧で前記入力電圧よりも高い候補電圧の一つを出力する切替回路と、を備える。電源電圧を分圧することで候補電圧を生成するために、容易に電源電圧の変化に応じて電圧値が変化する候補電圧を得ることができる。

前記切替回路は、例えば、前記残りの候補電圧で前記入力電圧よりも高い候補電圧の一つが入力される第1トランスファゲートと、前記最も低電圧の候補電圧が入力される第2トランスファゲートとを有している。前記検知信号が前記第1状態の場合に前記第2トランスファゲートが導通状態になり、前記検知信号が前記第2状態の場合に前記第1トランスファゲートが導通状態になる。

【0010】

また、入力電圧生成回路は、前記残りの候補電圧で前記入力電圧より高い候補電圧を一つ選択して前記切替回路に入力する選択回路をさらに備えてもよい。

このような選択回路は、例えば、前記残りの候補電圧がそれぞれ一つずつ入力される前記残りの候補電圧と同数のトランスファゲートを備え、いずれか一つのトランスファゲートが常に導通状態になるように構成される。

【0011】

本発明の電子システムは、以上のような本発明の電圧比較装置と、前記検知信号が第2状態の場合に動作状態になる半導体装置と、を備えている。上記のような電圧比較装置を用いるために、検知信号が電源電圧の不安定さに影響を受けることなく安定しており、半導体装置の誤動作も防止できる。半導体装置は、メモリ装置、CPU(Central Processing Unit)など、どのような装置であってもよい。

【発明の効果】

【0012】

以上のような本発明により、基準電圧よりも入力電圧が高くなった場合にはさらに高い入力電圧に切り替え、基準電圧よりも入力電圧が低くなった場合にはさらに低い入力電圧に切り替えるので、電源電圧の電圧降下或いは電圧上昇の影響を抑えることができる。そのために、電源電圧で動作する半導体装置の動作を安定化させることができる。

【発明を実施するための最良の形態】

【0013】

以下、図面を参照して本発明の実施形態を説明する。

【0014】

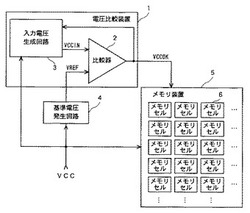

図1は、本発明の一実施形態である電子システムの構成図である。

この電子システムは、比較器2及び入力電圧VCCINを生成する入力電圧生成回路3を備える電圧比較装置1と、電子システム内で用いられる基準電圧VREFを発生する基準電圧発生回路4と、多数のメモリセル6によるメモリセルアレイを有する半導体装置の一例であるメモリ装置5とを有するものである。

本例では、電圧比較装置1、基準電圧発生回路4及びメモリ装置5が、一つの半導体基板上に形成されるものとして説明する。

【0015】

電圧比較装置1は、基準電圧発生回路4で生成された基準電圧VREFと入力電圧生成回路3で生成された入力電圧VCCINとを、比較器2で比較する。入力電圧VCCINは、電源電圧VCCの変化に応じて電圧値が変化する。比較器2からは、比較結果として検知信号VCCOKが出力される。検知信号VCCOKは、メモリ装置5のロックアウト信号として用いることができる。

【0016】

基準電圧発生回路4は、電源電圧VCCから基準電圧VREFを発生させる。基準電圧VREFは、電圧比較装置1及びメモリ装置5の他に、電子システム内の図示しない他の装置にも供給される。

【0017】

メモリ装置5には、メモリセル6の他に各メモリセル6にデータを書き込む、或いはメモリセル6からデータを読み出すための図示しない周辺回路が含まれている。メモリセル6及びこれらの周辺回路は、検知信号VCCOKによって動作状態及び非動作状態が切り替わるようになっている。メモリ装置5の一部には、後述する第1〜第4制御信号のような設定情報が記憶されている。このような設定情報は動作状態時に読み出される。

検知信号VCCOKが基準電圧VREFよりも入力電圧VCCINが低いことを表している場合(第1状態)、メモリ装置5は非動作状態になる。非動作状態時には、メモリ装置5に電源電圧VCCが印加されない。検知信号VCCOKが基準電圧VREFよりも入力電圧VCCINが高いことを表している場合(第2状態)、メモリ装置5は動作状態になる。動作状態時には、すべてのメモリセル6と周辺回路に電源電圧VCCが印加される。

【0018】

図2は、電圧比較装置1に含まれる入力電圧生成回路3の詳細な構成図である。

入力電圧生成回路3は、負荷回路31及び第1〜第6抵抗R1〜R6が直列に接続された分圧回路30と、第1、第2トランスファゲート33、34及び第1インバータ35を有する切替部32と、選択回路36とを備えている。

【0019】

分圧回路30は、電源電圧VCCを分圧して、入力電圧VCCINの候補となる候補電圧を出力する。この実施形態では、第1〜第5候補電圧V1〜V5を出力する。分圧回路30は、負荷回路31により電圧降下された電源電圧VCCを第1〜第6抵抗R1〜R6により分圧する。各抵抗間のノードN1〜N5には、第1〜第5候補電圧V1〜V5が生成される。第1〜第4候補電圧V1〜V4は、選択回路36に入力される。最も電圧値の低い第5候補電圧V5は、切替回路32に入力される。第1〜第5候補電圧V1〜V5は、例えば後述する図4の関係を満たすようになっている。第1〜第6抵抗R1〜R6は、このような第1〜第5候補電圧V1〜V5の関係を満たすような抵抗値である。

【0020】

切替回路32は、第5候補電圧V5と、選択回路36により第1〜第4候補電圧V1〜V4から選択された選択電圧VDIDと、のいずれか一方を、検知信号VCCOKに応じて、入力電圧VCCINとして出力する。第1、第2トランスファゲート33、34は、いずれもn型MOS(Metal Oxide Semiconductor)トランジスタとp型MOSトランジスタとが並列に接続されて構成される。第1トランスファゲート33を構成する各MOSトランジスタのソースが選択回路36に接続される。第1トランスファゲート33には、選択電圧VDIDが入力される。第2トランスファゲート34を構成するMOSトランジスタのソースが、分圧回路30のノードN5に接続される。第2トランスファゲート34には、第5候補電圧V5が入力される。

【0021】

検知信号VCCOKは、第1トランスファゲート33のn型MOSトランジスタのゲート及び第2トランスファゲート34のp型MOSトランジスタのゲートに入力される。また、検知信号VCCOKは、第1インバータ35により論理が反転して、第1トランスファゲート33のp型MOSトランジスタのゲート及び第2トランスファゲート34のn型MOSトランジスタのゲートに入力される。

【0022】

このような構成のために、切替回路32は、検知信号VCCOKが論理レベル「H」の場合に、第1トランスファゲート33を導通状態にして、選択電圧VDIDを入力電圧VCCINとして出力する。切替回路32は、検知信号VCCOKが論理レベル「L」の場合に、第2トランスファゲート34を導通状態にして、第5候補電圧V5を入力電圧VCCINとして出力する。

【0023】

選択回路36の構成を、図3の構成図を用いて説明する。

選択回路36は、第2〜第5インバータ360〜363及び第3〜第6トランスファゲート364〜367を備える。第3〜第6トランスファゲート364〜367は、第1、第2トランスファゲート33、34と同様に、n型MOSトランジスタとp型MOSトランジスタとが並列に接続されて構成される。

第3トランスファゲート364を構成する各MOSトランジスタのソースは、ノードN1に接続される。第4トランスファゲート365を構成する各MOSトランジスタのソースは、ノードN2に接続される。第5トランスファゲート366を構成する各MOSトランジスタのソースは、ノードN3に接続される。第6トランスファゲート367を構成する各MOSトランジスタのソースは、ノードN4に接続される。

【0024】

第2〜第5インバータ360〜363には、第1〜第4制御信号のいずれかが一つずつ入力される。第1〜第4制御信号は、通常、メモリ装置5に記憶されており、メモリ装置5が動作状態になる図示しない制御装置に読み出される。制御装置から第2〜第5インバータ360〜363に第1〜第4制御信号が入力される。第1〜第4制御信号は、使用者により設定可能である。第1〜第4制御信号は、いずれか一つが論理レベル「L」であり残りが論理レベル「H」である。

なお、メモリ装置5が非動作状態の場合には、制御装置により、初期設定として第1〜第4制御信号のいずれか一つが論理レベル「L」に設定される。そのために、メモリ装置5が非動作状態の場合でも、第1〜第4制御信号は、一つを除いて論理レベル「H」である。

【0025】

第2〜第5インバータ360〜363と第3〜第6トランスファゲート364〜367とは、それぞれ一つずつ「組」として構成される。第3〜第6トランスファゲート364〜367は、それぞれ組になる第2〜第5インバータ360〜363から第1〜第4制御信号の反転信号がn型MOSトランジスタのゲートに入力されるとともに、第1〜第4制御信号がp型MOSトランジスタゲートに入力される。

【0026】

第1〜第4制御信号のうち、論理レベル「L」が入力されるトランスファゲートが導通状態になる。そのために、常に第3〜第6トランスファゲート364〜367のいずれか一つが導通状態になる。

【0027】

図4は、ノードN1〜N5の電圧である第1〜第5候補電圧V1〜V5、電源電圧VCC、及び基準電圧VREFのそれぞれの例示図である。

基準電圧VREFは、電源電圧VCCに追従して変位するが、所定の電圧値(この実施形態では1.2V)以上にはならない。基準電圧VREFは、理想的には、所定の電圧値以下では、電源電圧VCCと同値になる。しかし、実際には、電源電圧VCCより0.2〜0.3V低い電圧値となる。所定の電圧値が1.2Vの場合、電源電圧が1.4〜1.5V以上であれば、基準電圧VREFが所定の電圧値で一定になる。

これに対して、第1〜第5候補電圧V1〜V5は、電源電圧VCCを分圧して得られるので、電源電圧VCCに常に追従して変位する。図2からもわかるように、第1候補電圧V1が最も高電圧であり、以下、第2候補電圧V2、第3候補電圧V3、第4候補電圧V4、第5候補電圧V5の順に、電圧値が低くなる。

図4の例では、第1候補電圧V1が基準電圧VREFと等しい場合に、電源電圧VCCが2.20Vである。第2候補電圧V2が基準電圧VREFと等しい場合に、電源電圧VCCが2.25Vである。第3候補電圧V3が基準電圧VREFと等しい場合に、電源電圧VCCが2.30Vである。第4候補電圧V4が基準電圧VREFと等しい場合に、電源電圧VCCが2.35Vである。第5候補電圧V5が基準電圧VREFと等しい場合に、電源電圧VCCが2.40Vである。

【0028】

図5aは、従来のこの種の電圧比較装置による電源電圧VCCの遷移に応じた検知信号VCCOKの動きを説明するためのタイムチャート図である。図5b、cは、本実施形態の電圧比較装置1による電源電圧VCCの遷移に応じて変化する基準電圧VREF、入力電圧VCCIN、及び検知信号VCCOKの動作を説明するためのタイムチャート図である。

【0029】

図5aでは、電源電圧VCCが基準電圧VREFよりも高電圧になると検知信号VCCOKが論理レベル「H」になる。

時刻t0で電源電圧VCCの供給が開始される。時刻t1になると、電源電圧VCCが基準電圧VREFよりも高電圧になる。これにより検知信号VCCOKが論理レベル「H」になり、メモリ装置5が動作状態になる。メモリ装置5が動作状態になるので、電源電圧VCCが電圧降下して、時刻t2で電源電圧VCCが基準電圧VREFよりも低電圧になる。これにより検知信号VCCOKが論理レベル「L」になり、メモリ装置5が非動作状態になる。その後、電源電圧VCCは上昇するために、再び基準電圧VREFより高電圧になり、メモリ装置5が動作状態になる。このようにメモリ装置5の動作が不安定である。同様のことは電源電圧VCCの供給を終了する場合にも起こる(時刻t3、t4)。

なお、特許文献1、2では、検知信号VCCOKが論理レベル「H」の場合に基準電圧VREFを下げることで、検知信号VCCOKの論理レベルが「L」になることを防止して、メモリ装置5の動作を安定化する。

【0030】

図5bでは、電源電圧VCCの供給が時刻t0に開始されると、基準電圧VREFが所定の時間後に所定の電圧値になる。入力電圧VCCINは、検知信号VCCOKが論理レベル「L」であるために、第5候補電圧V5である。入力電圧VCCINが電源電圧VCCの上昇に伴って上昇し、時刻t1で基準電圧VREF以上になると、検知信号VCCOKが論理レベル「H」になる。図4を例にすると、電源電圧VCCが2.40V以上になることで、入力電圧VCCINが基準電圧VREF以上になる。

【0031】

検知信号VCCOKが論理レベル「H」になると、切替回路32が切り替わり、第1〜第4候補電圧V1〜V4のいずれかが入力電圧VCCINになる。この実施形態では、初期設定として第2候補電圧V2が入力電圧VCCINになる。検知信号VCCOKの遷移に伴って、メモリ装置5が動作状態になり、電源電圧VCCが従来と同様に電圧降下する。しかし、入力電圧VCCINが第5候補電圧V5からそれより高電圧の第2候補電圧V2に切り替わっているために、入力電圧VCCOKが基準電圧VREF以下になることはない。図4を例にすると、電圧降下があっても電源電圧VCCが2.25V以上であれば、入力電圧VCCOKが基準電圧VREF以下になることはない。

そのために、電源電圧VCCの電圧降下による検知信号VCCOKの論理レベルの遷移はない。よって、メモリ装置5の動作は安定したものとなる。

【0032】

メモリ装置5が動作状態になるために、メモリ装置5から第1〜第4制御信号に関するデータが読み出される。読み出しが完了すると、第1〜第4制御信号が選択回路36に入力される。選択回路36は、これに応じて、第1候補電圧V1〜第5候補電圧V5のいずれかを選択電圧VDIDとして出力する。切替回路32は、検知信号VCCOKに応じて、選択電圧VDIDを入力電圧VCCINとして出力する。

【0033】

図5cでは、電源電圧VCCの供給が終了する。終了による電源電圧VCCの低下に伴い、時刻t3で入力電圧VCCINが基準電圧VREF以下になると、検知信号VCCOKが論理レベル「L」に遷移する。これにより、切替回路32が切り替わり、第5候補電圧V5が入力電圧VCCINとなる。電源電圧VCCは、検知信号VCCOKによりメモリ装置5が非動作状態になることで上昇する。しかし、入力電圧VCCINが第5候補電圧V5に切り替わっているために、入力電圧VCCINが基準電圧VREFよりも高電圧になることはない。そのために、検知信号VCCOKの遷移はない。よって、メモリ装置5の動作は安定して終了する。

図5cは、入力電圧VCCINが第2候補電圧V2の場合の例示図である。入力電圧VCCINが第1候補電圧V1の場合には、時刻t3が遅くなり、第4候補電圧V4の場合には、時刻t3が早まる。

【0034】

このように、本実施形態の電圧比較装置1を用いることで、従来のように、電源電圧VCCの供給開始及び終了時にメモリ装置5の動作が不安定になることはない。また、第1〜第5候補電圧V1〜V5から、最適な電圧値が選択可能であるので、電子システム全体のノイズなどによる電源電圧VCCの変動にも、電圧比較装置1の再設計などを行わなくても対処可能である。

【0035】

上記の実施形態では、検知信号VCCOKが論理レベル「L」の場合に第5候補電圧V5が入力電圧VCCINになり、論理レベル「H」の場合に第1〜第4候補V1〜V4のいずれかが入力電圧VCCINになるとしているが、これに限らなくともよい。例えば、検知信号VCCOKの論理レベルが「L」になると、それまで入力電圧VCCINとなっていた候補電圧よりも低い候補電圧に入力電圧VCCINを切り替えることで、上記と同様の効果を得ることができる。また、検知信号VCCOKの論理レベルが「H」になると、それまで入力電圧VCCINとなっていた候補電圧よりも高い候補電圧に入力電圧VCCINを切り替えることで、上記と同様の効果を得ることができる。

【図面の簡単な説明】

【0036】

【図1】本発明の電子システムの構成図である。

【図2】入力電圧生成部の詳細な構成図である。

【図3】選択部の詳細な構成図である。

【図4】第1〜第5候補電圧、電源電圧、及び基準電圧の、それぞれの電圧値の例示図である。

【図5a】従来の電圧比較装置による電源電圧の遷移に応じた検知信号の動きを説明するためのタイムチャート図である。

【図5b】図5bは、本実施形態の電圧検知部による電源電圧の遷移に応じて変化する基準電圧、入力電圧、及び検知信号の動作を説明するためのタイムチャート図である。

【図5c】図5cは、本実施形態の電圧検知部による電源電圧の遷移に応じて変化する基準電圧、入力電圧、及び検知信号の動作を説明するためのタイムチャート図である。

【符号の説明】

【0037】

1…電圧比較装置、2…比較器、3…入力電圧生成回路、30…分圧回路、31…負荷回路、32…切替回路、33,34…第1,第2トランスファゲート、35…第1インバータ、36…選択回路、360〜363…第2〜第5インバータ、364〜367…第3〜第6トランスファゲート、4…基準電圧発生回路、5…メモリ装置、6…メモリセル、R1〜R6…第1〜第6抵抗、VCC…電源電圧、VREF…基準電圧、VCCIN…入力電圧、VCCOK…検知信号、VDID…選択電圧

【技術分野】

【0001】

本発明は、メモリなどの大量の素子を備えた半導体装置に印加される電源電圧を基準電圧と比較して、電源電圧が基準電圧よりも高電圧か否かを検知する電圧比較装置、及びこのような電圧比較装置を備えた電子システムに関する。

【背景技術】

【0002】

従来の電圧比較装置として、例えば半導体装置に入力される電源電圧と所定の基準電圧とを比較して、電源電圧が半導体装置の正常動作に充分な電圧であるかを検知するものがある。検知結果を表す検知信号は、例えば半導体装置のロックアウト(lockout)信号として用いることができる。ロックアウト信号により、電源電圧が正常動作に充分であれば半導体装置が動作状態になり、電源電圧が正常動作に不充分であれば半導体装置が非動作状態になる。

【0003】

電源電圧は、フラッシュメモリなどのように大量の素子を有する半導体装置に印加される場合に、不安定な動きになることがある。例えば、ロックアウト信号により半導体装置が動作状態になると、負荷が急激に増加するために、電源電圧が降下する。電源電圧が基準電圧以上になると半導体装置が動作状態になるので、このような電圧降下は、電源電圧が基準電圧以上になった直後に発生する。電圧降下により、電源電圧が再び基準電圧以下になる。電圧比較装置がこれを検知すると、ロックアウト信号がすぐに切り替わる。これにより、半導体装置は動作状態になった直後に非動作状態になり、動作が不安定になって半導体装置の誤動作の原因になる。同様のことは、電源電圧を下げて半導体装置を非動作状態にする場合にも発生する。

【0004】

このような電源電圧による半導体装置の不安定動作を防止するために、特許文献1、2の発明が提案されている。特許文献1、2には、基準電圧を2種類用意しておき、これを切り換えて用いる技術が記載されている。特許文献1、2では、電源電圧が基準電圧以上になると基準電圧を下げる。これにより、電源電圧の電圧降下があっても、電源電圧が基準電圧以下になることを防止して検知信号が切り替わらないようになっている。

【特許文献1】特開2005−141811号公報

【特許文献2】特開2007−306648号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

特許文献1、2の発明では、基準電圧は予め決められた2種類しか取ることができない。そのために、電源電圧の電圧降下が予想以上であれば、上記の問題を解決することができず、半導体装置の動作を安定させることができない。

【0006】

本発明は、このような問題に鑑みて、電源電圧のような入力電圧の電圧降下及び電圧上昇に対応した電圧比較装置を提供することを主たる課題とする。

【課題を解決するための手段】

【0007】

以上の課題を解決する本発明の電圧比較装置は、所定の基準電圧と入力電圧とを比較して、前記入力電圧が前記基準電圧よりも低い場合に第1状態になり、前記入力電圧が前記基準電圧よりも高い場合に第2状態になる検知信号を出力する比較器と、前記入力電圧の候補となる複数の候補電圧を出力可能とし、前記検知信号が前記第1状態の場合は前記複数の候補電圧のうち前記入力電圧よりも低い候補電圧を新たな入力電圧として前記比較器へ出力し、前記検知信号が前記第2状態の場合は前記複数の候補電圧のうち前記入力電圧よりも高い候補電圧を新たな入力電圧として前記比較器へ出力する入力電圧生成回路と、を備える。

【0008】

従来のこの種の電圧比較装置は、上述の通り、基準電圧よりも電源電圧が高くなった場合に基準電圧を下げて、電源電圧の電圧降下があっても、電源電圧が基準電圧より低くなることを防止している。

本発明の電圧比較装置は、従来とは逆に、入力電圧が基準電圧よりも高い場合に入力電圧をさらに高くする。これにより入力電圧が電源電圧と同様に電圧降下があっても、基準電圧以下になることを防止できる。また、入力電圧が基準電圧よりも低い場合に入力電圧をさらに低くする。これにより入力電圧に電圧上昇があっても、基準電圧以上になることを防止できる。

【0009】

本発明では、前記入力電圧生成回路が、例えば、電源電圧を分圧して前記複数の候補電圧を出力する分圧回路と、前記検知信号が前記第1状態の場合に、最も低電圧の候補電圧を出力し、前記検知信号が前記第2状態の場合に、残りの候補電圧で前記入力電圧よりも高い候補電圧の一つを出力する切替回路と、を備える。電源電圧を分圧することで候補電圧を生成するために、容易に電源電圧の変化に応じて電圧値が変化する候補電圧を得ることができる。

前記切替回路は、例えば、前記残りの候補電圧で前記入力電圧よりも高い候補電圧の一つが入力される第1トランスファゲートと、前記最も低電圧の候補電圧が入力される第2トランスファゲートとを有している。前記検知信号が前記第1状態の場合に前記第2トランスファゲートが導通状態になり、前記検知信号が前記第2状態の場合に前記第1トランスファゲートが導通状態になる。

【0010】

また、入力電圧生成回路は、前記残りの候補電圧で前記入力電圧より高い候補電圧を一つ選択して前記切替回路に入力する選択回路をさらに備えてもよい。

このような選択回路は、例えば、前記残りの候補電圧がそれぞれ一つずつ入力される前記残りの候補電圧と同数のトランスファゲートを備え、いずれか一つのトランスファゲートが常に導通状態になるように構成される。

【0011】

本発明の電子システムは、以上のような本発明の電圧比較装置と、前記検知信号が第2状態の場合に動作状態になる半導体装置と、を備えている。上記のような電圧比較装置を用いるために、検知信号が電源電圧の不安定さに影響を受けることなく安定しており、半導体装置の誤動作も防止できる。半導体装置は、メモリ装置、CPU(Central Processing Unit)など、どのような装置であってもよい。

【発明の効果】

【0012】

以上のような本発明により、基準電圧よりも入力電圧が高くなった場合にはさらに高い入力電圧に切り替え、基準電圧よりも入力電圧が低くなった場合にはさらに低い入力電圧に切り替えるので、電源電圧の電圧降下或いは電圧上昇の影響を抑えることができる。そのために、電源電圧で動作する半導体装置の動作を安定化させることができる。

【発明を実施するための最良の形態】

【0013】

以下、図面を参照して本発明の実施形態を説明する。

【0014】

図1は、本発明の一実施形態である電子システムの構成図である。

この電子システムは、比較器2及び入力電圧VCCINを生成する入力電圧生成回路3を備える電圧比較装置1と、電子システム内で用いられる基準電圧VREFを発生する基準電圧発生回路4と、多数のメモリセル6によるメモリセルアレイを有する半導体装置の一例であるメモリ装置5とを有するものである。

本例では、電圧比較装置1、基準電圧発生回路4及びメモリ装置5が、一つの半導体基板上に形成されるものとして説明する。

【0015】

電圧比較装置1は、基準電圧発生回路4で生成された基準電圧VREFと入力電圧生成回路3で生成された入力電圧VCCINとを、比較器2で比較する。入力電圧VCCINは、電源電圧VCCの変化に応じて電圧値が変化する。比較器2からは、比較結果として検知信号VCCOKが出力される。検知信号VCCOKは、メモリ装置5のロックアウト信号として用いることができる。

【0016】

基準電圧発生回路4は、電源電圧VCCから基準電圧VREFを発生させる。基準電圧VREFは、電圧比較装置1及びメモリ装置5の他に、電子システム内の図示しない他の装置にも供給される。

【0017】

メモリ装置5には、メモリセル6の他に各メモリセル6にデータを書き込む、或いはメモリセル6からデータを読み出すための図示しない周辺回路が含まれている。メモリセル6及びこれらの周辺回路は、検知信号VCCOKによって動作状態及び非動作状態が切り替わるようになっている。メモリ装置5の一部には、後述する第1〜第4制御信号のような設定情報が記憶されている。このような設定情報は動作状態時に読み出される。

検知信号VCCOKが基準電圧VREFよりも入力電圧VCCINが低いことを表している場合(第1状態)、メモリ装置5は非動作状態になる。非動作状態時には、メモリ装置5に電源電圧VCCが印加されない。検知信号VCCOKが基準電圧VREFよりも入力電圧VCCINが高いことを表している場合(第2状態)、メモリ装置5は動作状態になる。動作状態時には、すべてのメモリセル6と周辺回路に電源電圧VCCが印加される。

【0018】

図2は、電圧比較装置1に含まれる入力電圧生成回路3の詳細な構成図である。

入力電圧生成回路3は、負荷回路31及び第1〜第6抵抗R1〜R6が直列に接続された分圧回路30と、第1、第2トランスファゲート33、34及び第1インバータ35を有する切替部32と、選択回路36とを備えている。

【0019】

分圧回路30は、電源電圧VCCを分圧して、入力電圧VCCINの候補となる候補電圧を出力する。この実施形態では、第1〜第5候補電圧V1〜V5を出力する。分圧回路30は、負荷回路31により電圧降下された電源電圧VCCを第1〜第6抵抗R1〜R6により分圧する。各抵抗間のノードN1〜N5には、第1〜第5候補電圧V1〜V5が生成される。第1〜第4候補電圧V1〜V4は、選択回路36に入力される。最も電圧値の低い第5候補電圧V5は、切替回路32に入力される。第1〜第5候補電圧V1〜V5は、例えば後述する図4の関係を満たすようになっている。第1〜第6抵抗R1〜R6は、このような第1〜第5候補電圧V1〜V5の関係を満たすような抵抗値である。

【0020】

切替回路32は、第5候補電圧V5と、選択回路36により第1〜第4候補電圧V1〜V4から選択された選択電圧VDIDと、のいずれか一方を、検知信号VCCOKに応じて、入力電圧VCCINとして出力する。第1、第2トランスファゲート33、34は、いずれもn型MOS(Metal Oxide Semiconductor)トランジスタとp型MOSトランジスタとが並列に接続されて構成される。第1トランスファゲート33を構成する各MOSトランジスタのソースが選択回路36に接続される。第1トランスファゲート33には、選択電圧VDIDが入力される。第2トランスファゲート34を構成するMOSトランジスタのソースが、分圧回路30のノードN5に接続される。第2トランスファゲート34には、第5候補電圧V5が入力される。

【0021】

検知信号VCCOKは、第1トランスファゲート33のn型MOSトランジスタのゲート及び第2トランスファゲート34のp型MOSトランジスタのゲートに入力される。また、検知信号VCCOKは、第1インバータ35により論理が反転して、第1トランスファゲート33のp型MOSトランジスタのゲート及び第2トランスファゲート34のn型MOSトランジスタのゲートに入力される。

【0022】

このような構成のために、切替回路32は、検知信号VCCOKが論理レベル「H」の場合に、第1トランスファゲート33を導通状態にして、選択電圧VDIDを入力電圧VCCINとして出力する。切替回路32は、検知信号VCCOKが論理レベル「L」の場合に、第2トランスファゲート34を導通状態にして、第5候補電圧V5を入力電圧VCCINとして出力する。

【0023】

選択回路36の構成を、図3の構成図を用いて説明する。

選択回路36は、第2〜第5インバータ360〜363及び第3〜第6トランスファゲート364〜367を備える。第3〜第6トランスファゲート364〜367は、第1、第2トランスファゲート33、34と同様に、n型MOSトランジスタとp型MOSトランジスタとが並列に接続されて構成される。

第3トランスファゲート364を構成する各MOSトランジスタのソースは、ノードN1に接続される。第4トランスファゲート365を構成する各MOSトランジスタのソースは、ノードN2に接続される。第5トランスファゲート366を構成する各MOSトランジスタのソースは、ノードN3に接続される。第6トランスファゲート367を構成する各MOSトランジスタのソースは、ノードN4に接続される。

【0024】

第2〜第5インバータ360〜363には、第1〜第4制御信号のいずれかが一つずつ入力される。第1〜第4制御信号は、通常、メモリ装置5に記憶されており、メモリ装置5が動作状態になる図示しない制御装置に読み出される。制御装置から第2〜第5インバータ360〜363に第1〜第4制御信号が入力される。第1〜第4制御信号は、使用者により設定可能である。第1〜第4制御信号は、いずれか一つが論理レベル「L」であり残りが論理レベル「H」である。

なお、メモリ装置5が非動作状態の場合には、制御装置により、初期設定として第1〜第4制御信号のいずれか一つが論理レベル「L」に設定される。そのために、メモリ装置5が非動作状態の場合でも、第1〜第4制御信号は、一つを除いて論理レベル「H」である。

【0025】

第2〜第5インバータ360〜363と第3〜第6トランスファゲート364〜367とは、それぞれ一つずつ「組」として構成される。第3〜第6トランスファゲート364〜367は、それぞれ組になる第2〜第5インバータ360〜363から第1〜第4制御信号の反転信号がn型MOSトランジスタのゲートに入力されるとともに、第1〜第4制御信号がp型MOSトランジスタゲートに入力される。

【0026】

第1〜第4制御信号のうち、論理レベル「L」が入力されるトランスファゲートが導通状態になる。そのために、常に第3〜第6トランスファゲート364〜367のいずれか一つが導通状態になる。

【0027】

図4は、ノードN1〜N5の電圧である第1〜第5候補電圧V1〜V5、電源電圧VCC、及び基準電圧VREFのそれぞれの例示図である。

基準電圧VREFは、電源電圧VCCに追従して変位するが、所定の電圧値(この実施形態では1.2V)以上にはならない。基準電圧VREFは、理想的には、所定の電圧値以下では、電源電圧VCCと同値になる。しかし、実際には、電源電圧VCCより0.2〜0.3V低い電圧値となる。所定の電圧値が1.2Vの場合、電源電圧が1.4〜1.5V以上であれば、基準電圧VREFが所定の電圧値で一定になる。

これに対して、第1〜第5候補電圧V1〜V5は、電源電圧VCCを分圧して得られるので、電源電圧VCCに常に追従して変位する。図2からもわかるように、第1候補電圧V1が最も高電圧であり、以下、第2候補電圧V2、第3候補電圧V3、第4候補電圧V4、第5候補電圧V5の順に、電圧値が低くなる。

図4の例では、第1候補電圧V1が基準電圧VREFと等しい場合に、電源電圧VCCが2.20Vである。第2候補電圧V2が基準電圧VREFと等しい場合に、電源電圧VCCが2.25Vである。第3候補電圧V3が基準電圧VREFと等しい場合に、電源電圧VCCが2.30Vである。第4候補電圧V4が基準電圧VREFと等しい場合に、電源電圧VCCが2.35Vである。第5候補電圧V5が基準電圧VREFと等しい場合に、電源電圧VCCが2.40Vである。

【0028】

図5aは、従来のこの種の電圧比較装置による電源電圧VCCの遷移に応じた検知信号VCCOKの動きを説明するためのタイムチャート図である。図5b、cは、本実施形態の電圧比較装置1による電源電圧VCCの遷移に応じて変化する基準電圧VREF、入力電圧VCCIN、及び検知信号VCCOKの動作を説明するためのタイムチャート図である。

【0029】

図5aでは、電源電圧VCCが基準電圧VREFよりも高電圧になると検知信号VCCOKが論理レベル「H」になる。

時刻t0で電源電圧VCCの供給が開始される。時刻t1になると、電源電圧VCCが基準電圧VREFよりも高電圧になる。これにより検知信号VCCOKが論理レベル「H」になり、メモリ装置5が動作状態になる。メモリ装置5が動作状態になるので、電源電圧VCCが電圧降下して、時刻t2で電源電圧VCCが基準電圧VREFよりも低電圧になる。これにより検知信号VCCOKが論理レベル「L」になり、メモリ装置5が非動作状態になる。その後、電源電圧VCCは上昇するために、再び基準電圧VREFより高電圧になり、メモリ装置5が動作状態になる。このようにメモリ装置5の動作が不安定である。同様のことは電源電圧VCCの供給を終了する場合にも起こる(時刻t3、t4)。

なお、特許文献1、2では、検知信号VCCOKが論理レベル「H」の場合に基準電圧VREFを下げることで、検知信号VCCOKの論理レベルが「L」になることを防止して、メモリ装置5の動作を安定化する。

【0030】

図5bでは、電源電圧VCCの供給が時刻t0に開始されると、基準電圧VREFが所定の時間後に所定の電圧値になる。入力電圧VCCINは、検知信号VCCOKが論理レベル「L」であるために、第5候補電圧V5である。入力電圧VCCINが電源電圧VCCの上昇に伴って上昇し、時刻t1で基準電圧VREF以上になると、検知信号VCCOKが論理レベル「H」になる。図4を例にすると、電源電圧VCCが2.40V以上になることで、入力電圧VCCINが基準電圧VREF以上になる。

【0031】

検知信号VCCOKが論理レベル「H」になると、切替回路32が切り替わり、第1〜第4候補電圧V1〜V4のいずれかが入力電圧VCCINになる。この実施形態では、初期設定として第2候補電圧V2が入力電圧VCCINになる。検知信号VCCOKの遷移に伴って、メモリ装置5が動作状態になり、電源電圧VCCが従来と同様に電圧降下する。しかし、入力電圧VCCINが第5候補電圧V5からそれより高電圧の第2候補電圧V2に切り替わっているために、入力電圧VCCOKが基準電圧VREF以下になることはない。図4を例にすると、電圧降下があっても電源電圧VCCが2.25V以上であれば、入力電圧VCCOKが基準電圧VREF以下になることはない。

そのために、電源電圧VCCの電圧降下による検知信号VCCOKの論理レベルの遷移はない。よって、メモリ装置5の動作は安定したものとなる。

【0032】

メモリ装置5が動作状態になるために、メモリ装置5から第1〜第4制御信号に関するデータが読み出される。読み出しが完了すると、第1〜第4制御信号が選択回路36に入力される。選択回路36は、これに応じて、第1候補電圧V1〜第5候補電圧V5のいずれかを選択電圧VDIDとして出力する。切替回路32は、検知信号VCCOKに応じて、選択電圧VDIDを入力電圧VCCINとして出力する。

【0033】

図5cでは、電源電圧VCCの供給が終了する。終了による電源電圧VCCの低下に伴い、時刻t3で入力電圧VCCINが基準電圧VREF以下になると、検知信号VCCOKが論理レベル「L」に遷移する。これにより、切替回路32が切り替わり、第5候補電圧V5が入力電圧VCCINとなる。電源電圧VCCは、検知信号VCCOKによりメモリ装置5が非動作状態になることで上昇する。しかし、入力電圧VCCINが第5候補電圧V5に切り替わっているために、入力電圧VCCINが基準電圧VREFよりも高電圧になることはない。そのために、検知信号VCCOKの遷移はない。よって、メモリ装置5の動作は安定して終了する。

図5cは、入力電圧VCCINが第2候補電圧V2の場合の例示図である。入力電圧VCCINが第1候補電圧V1の場合には、時刻t3が遅くなり、第4候補電圧V4の場合には、時刻t3が早まる。

【0034】

このように、本実施形態の電圧比較装置1を用いることで、従来のように、電源電圧VCCの供給開始及び終了時にメモリ装置5の動作が不安定になることはない。また、第1〜第5候補電圧V1〜V5から、最適な電圧値が選択可能であるので、電子システム全体のノイズなどによる電源電圧VCCの変動にも、電圧比較装置1の再設計などを行わなくても対処可能である。

【0035】

上記の実施形態では、検知信号VCCOKが論理レベル「L」の場合に第5候補電圧V5が入力電圧VCCINになり、論理レベル「H」の場合に第1〜第4候補V1〜V4のいずれかが入力電圧VCCINになるとしているが、これに限らなくともよい。例えば、検知信号VCCOKの論理レベルが「L」になると、それまで入力電圧VCCINとなっていた候補電圧よりも低い候補電圧に入力電圧VCCINを切り替えることで、上記と同様の効果を得ることができる。また、検知信号VCCOKの論理レベルが「H」になると、それまで入力電圧VCCINとなっていた候補電圧よりも高い候補電圧に入力電圧VCCINを切り替えることで、上記と同様の効果を得ることができる。

【図面の簡単な説明】

【0036】

【図1】本発明の電子システムの構成図である。

【図2】入力電圧生成部の詳細な構成図である。

【図3】選択部の詳細な構成図である。

【図4】第1〜第5候補電圧、電源電圧、及び基準電圧の、それぞれの電圧値の例示図である。

【図5a】従来の電圧比較装置による電源電圧の遷移に応じた検知信号の動きを説明するためのタイムチャート図である。

【図5b】図5bは、本実施形態の電圧検知部による電源電圧の遷移に応じて変化する基準電圧、入力電圧、及び検知信号の動作を説明するためのタイムチャート図である。

【図5c】図5cは、本実施形態の電圧検知部による電源電圧の遷移に応じて変化する基準電圧、入力電圧、及び検知信号の動作を説明するためのタイムチャート図である。

【符号の説明】

【0037】

1…電圧比較装置、2…比較器、3…入力電圧生成回路、30…分圧回路、31…負荷回路、32…切替回路、33,34…第1,第2トランスファゲート、35…第1インバータ、36…選択回路、360〜363…第2〜第5インバータ、364〜367…第3〜第6トランスファゲート、4…基準電圧発生回路、5…メモリ装置、6…メモリセル、R1〜R6…第1〜第6抵抗、VCC…電源電圧、VREF…基準電圧、VCCIN…入力電圧、VCCOK…検知信号、VDID…選択電圧

【特許請求の範囲】

【請求項1】

所定の基準電圧と入力電圧とを比較して、前記入力電圧が前記基準電圧よりも低い場合に第1状態になり、前記入力電圧が前記基準電圧よりも高い場合に第2状態になる検知信号を出力する比較器と、

前記入力電圧の候補となる複数の候補電圧を出力可能とし、前記検知信号が前記第1状態の場合は前記複数の候補電圧のうち前記入力電圧よりも低い候補電圧を新たな入力電圧として前記比較器へ出力し、前記検知信号が前記第2状態の場合は前記複数の候補電圧のうち前記入力電圧よりも高い候補電圧を新たな入力電圧として前記比較器へ出力する入力電圧生成回路と、を備える、

電圧比較装置。

【請求項2】

前記入力電圧生成回路は、

電源電圧を分圧して前記複数の候補電圧を出力する分圧回路と、

前記検知信号が前記第1状態の場合に、最も低電圧の候補電圧を出力し、前記検知信号が前記第2状態の場合に、残りの候補電圧で前記入力電圧よりも高い候補電圧の一つを出力する切替回路と、を備えており、

切替回路から出力される候補電圧が、前記入力電圧として前記比較器へ出力される、

請求項1記載の電圧比較装置。

【請求項3】

前記切替回路は、前記残りの候補電圧で前記入力電圧よりも高い候補電圧の一つが入力される第1トランスファゲートと、前記最も低電圧の候補電圧が入力される第2トランスファゲートとを有しており、前記検知信号が前記第1状態の場合に前記第2トランスファゲートが導通状態になり、前記検知信号が前記第2状態の場合に前記第1トランスファゲートが導通状態になる、

請求項2記載の電圧比較装置。

【請求項4】

前記入力電圧生成回路は、

前記残りの候補電圧で前記入力電圧より高い候補電圧を一つ選択して前記切替回路に入力する選択回路をさらに備える、

請求項2又は3記載の電圧比較装置。

【請求項5】

前記選択回路は、前記残りの候補電圧がそれぞれ一つずつ入力される前記残りの候補電圧と同数のトランスファゲートを備えており、

いずれか一つのトランスファゲートが常に導通状態になるように構成されている、

請求項4記載の電圧比較装置。

【請求項6】

請求項1〜5のいずれか1項に記載の電圧比較装置と、前記検知信号が前記第2状態の場合に動作状態になる半導体装置と、を備える、

電子システム。

【請求項1】

所定の基準電圧と入力電圧とを比較して、前記入力電圧が前記基準電圧よりも低い場合に第1状態になり、前記入力電圧が前記基準電圧よりも高い場合に第2状態になる検知信号を出力する比較器と、

前記入力電圧の候補となる複数の候補電圧を出力可能とし、前記検知信号が前記第1状態の場合は前記複数の候補電圧のうち前記入力電圧よりも低い候補電圧を新たな入力電圧として前記比較器へ出力し、前記検知信号が前記第2状態の場合は前記複数の候補電圧のうち前記入力電圧よりも高い候補電圧を新たな入力電圧として前記比較器へ出力する入力電圧生成回路と、を備える、

電圧比較装置。

【請求項2】

前記入力電圧生成回路は、

電源電圧を分圧して前記複数の候補電圧を出力する分圧回路と、

前記検知信号が前記第1状態の場合に、最も低電圧の候補電圧を出力し、前記検知信号が前記第2状態の場合に、残りの候補電圧で前記入力電圧よりも高い候補電圧の一つを出力する切替回路と、を備えており、

切替回路から出力される候補電圧が、前記入力電圧として前記比較器へ出力される、

請求項1記載の電圧比較装置。

【請求項3】

前記切替回路は、前記残りの候補電圧で前記入力電圧よりも高い候補電圧の一つが入力される第1トランスファゲートと、前記最も低電圧の候補電圧が入力される第2トランスファゲートとを有しており、前記検知信号が前記第1状態の場合に前記第2トランスファゲートが導通状態になり、前記検知信号が前記第2状態の場合に前記第1トランスファゲートが導通状態になる、

請求項2記載の電圧比較装置。

【請求項4】

前記入力電圧生成回路は、

前記残りの候補電圧で前記入力電圧より高い候補電圧を一つ選択して前記切替回路に入力する選択回路をさらに備える、

請求項2又は3記載の電圧比較装置。

【請求項5】

前記選択回路は、前記残りの候補電圧がそれぞれ一つずつ入力される前記残りの候補電圧と同数のトランスファゲートを備えており、

いずれか一つのトランスファゲートが常に導通状態になるように構成されている、

請求項4記載の電圧比較装置。

【請求項6】

請求項1〜5のいずれか1項に記載の電圧比較装置と、前記検知信号が前記第2状態の場合に動作状態になる半導体装置と、を備える、

電子システム。

【図1】

【図2】

【図3】

【図4】

【図5a】

【図5b】

【図5c】

【図2】

【図3】

【図4】

【図5a】

【図5b】

【図5c】

【公開番号】特開2009−201183(P2009−201183A)

【公開日】平成21年9月3日(2009.9.3)

【国際特許分類】

【出願番号】特願2008−37276(P2008−37276)

【出願日】平成20年2月19日(2008.2.19)

【出願人】(504378124)スパンション エルエルシー (229)

【Fターム(参考)】

【公開日】平成21年9月3日(2009.9.3)

【国際特許分類】

【出願日】平成20年2月19日(2008.2.19)

【出願人】(504378124)スパンション エルエルシー (229)

【Fターム(参考)】

[ Back to top ]