Fターム[2F067CC17]の内容

波動性又は粒子性放射線を用いた測長装置 (9,092) | 対象物(具体例) (587) | 半導体関連 (368) | ウエハー (223)

Fターム[2F067CC17]に分類される特許

81 - 100 / 223

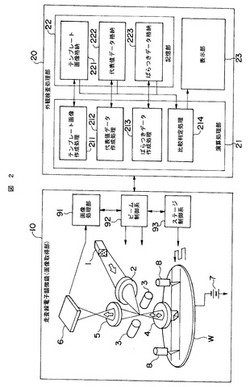

外観検査方法および外観検査装置、半導体検査装置ならびに半導体ウェハの断面検査装置

【課題】半導体デバイスの複雑な構造のばらつきを直感的かつ定量的に評価することができる外観検査装置を提供する。

【解決手段】被検査物の像を検出する画像検出部6、検出した画像を処理する画像処理部91、被検査物をスキャンするビーム制御系92およびステージ制御系93を有するスキャン制御部を備えた画像検出部10と、検出した画像から外観を検査する外観検査処理部20とを備えた外観検査装置において、外観検査処理部10が、取得した複数の像を重ね合わせ、像の各点(x,y)における代表的な値(代表値データμ(x,y))を求める代表値データ作成処理機能212と、複数の像の各点(x、y)における許容範囲の値(ばらつきデータσ(x,y))とを求めるばらつきデータ作成処理機能213と、代表的値データとばらつきデータとを元に、検査対象物の良否を判定する判定処理機能214を有する。

(もっと読む)

データ解析装置

【課題】

CD-SEM画像からパターンのエッジを抽出する際にパターン上における高さ(基板からの距離を表す値)を指定してエッジ点を抽出する。あるいは、それを行って得られるLER値やLERのフーリエスペクトルを得る。

【解決手段】

あらかじめ同じサンプルをAFMとCD-SEMとで観察しておき(601)、AFM観察結果から、高さを指定して得られるLERの大きさやLERの自己相関距離あるいはスペクトルという指標を求め、さらにCD-SEM観察結果からは、エッジ点を検出する画像処理条件を指定して得られるこれらの指標を求め(602)、値が一致するときにその値を与える高さと画像処理条件とが対応していると判断し(603)、以降、AFM観察の代わりにCD-SEM画像からこの画像処理条件を用いてエッジ点を抽出する。

(もっと読む)

欠陥レビュー方法およびその装置

【課題】

試料上の欠陥を,画像取得手段を用いて短時間に多数の欠陥観察を行う方法において,第1の倍率で撮像した画像から誤検出なく欠陥位置を特定し,第2の倍率での撮像を可能とする。

【解決手段】

試料上の欠陥を観察する方法において,画像取得手段を用いて第1の倍率で前記欠陥を含む欠陥画像を撮像し,欠陥画像から欠陥を含まない参照画像を合成し,取得した欠陥画像と合成した参照画像とを比較して欠陥候補を検出し,該欠陥候補を欠陥と正常部に識別する処理を行い,欠陥と識別された部位のみを第2の倍率で撮像するように装置を構成した。

(もっと読む)

半導体パターンの検査方法及び検査装置

【課題】半導体パターンの検査において、レシピの良不良診断および最適化の作業を自動的に行なう機能を備えた方法を提供する。

【解決手段】半導体パターン上に設定された測定点を含む領域について低倍率のSEM画像を取得する。次に、予めレシピとして登録されたアドレッシング用パターン、オートフォーカス用パターン、および、オートスティグマ用パターンが所定の推奨条件を満たすか否かを判定する。所定の推奨条件を満たさないと判定されたとき、SEM画像上より、最適なアドレッシング用パターン、オートフォーカス用パターン、および、オートスティグマ用パターンを選択する。

(もっと読む)

走査型電子顕微鏡を用いた回路パターンの寸法計測装置およびその方法

【課題】

走査型電子顕微鏡(SEM)を用いた回路パターンの寸法計測において、試料上の任意の評価ポイント(EP)を自動で撮像し,評価ポイントに形成された回路パターンを自動で計測することを可能にする。

【解決手段】

本発明では、走査型電子顕微鏡(SEM)を用いた回路パターンの寸法計測において、EPの座標データと前記EPを含む回路パターンの設計データを入力とし,前記EP座標データと設計データから,前記EP内に存在するパターンを計測するための測長カーソルの生成および測長方法の選択あるいは設定を自動で行うようにしてレシピを自動生成し,このレシピを用いて自動撮像・計測を行うようにした。

(もっと読む)

荷電粒子顕微鏡装置及びそれを用いた画像処理方法

【課題】

パターンの形状や試料特性に応じて,高速・高性能な画質改善処理を行う。

【解決手段】設計データや,設計データ上の各領域に対応する試料特性情報を用いて画質改善処理を行うことにより,画像上の個々の領域に対応する試料特性に応じて適切な画質改善処理を施し,画像上の領域分割を高速に行うといった処理を可能とする。さらに,設計データと対応する画像情報を保存したデータベースを利用することにより,類似した設計データにおいて過去に撮像した画像との差が大きい箇所を自動で強調する等の画質改善処理を可能とする。

(もっと読む)

ステージ及び電子顕微鏡装置

【課題】

本発明は、停止時のドリフトが小さいステージ機構およびそれを備えた電子顕微鏡装置を提供することを目的とする。

【解決手段】

上記課題を解決するために、本発明では、2以上の伸縮或いは揺動が可能な駆動素子を有し、当該2つの駆動素子の協働によりステージを移動させる試料ステージを提供する。2つの駆動素子の協働により、当該2つの駆動素子の動作を組合わせることによる種々の制御が可能となり、結果として、ステージの移動のみならず、停止時のドリフトの抑制が可能なステージ機構の提供が可能となる。

(もっと読む)

パターン測定方法及びパターン測定装置

【課題】

本発明の目的はパターンエッジの傾斜を評価するのに好適な試料測定方法、及び試料測定装置の提供にある。

【解決手段】

上記目的を達成するために、以下にパターンエッジについて、複数の輪郭線を形成し、その輪郭線間の寸法を評価する方法、及び装置を提案する。このように複数の輪郭線を形成することによって、パターンのエッジ部分の傾斜の程度を評価することが可能となる。また、エッジ部分の傾斜の程度の評価値を、面内分布表示することによって、テーパーが形成される要因を特定することが容易になる。

(もっと読む)

テンプレート作成方法及び画像処理装置

【課題】

本発明の目的は、同種画像間の画像認識に用いられるテンプレートと同等の情報を、設計データに基づいて形成されるテンプレートに付加することで、実画像を取得することなく、設計データに基づいてテンプレートを作成することのできる容易性の維持と、テンプレートと実画像の一致度を高めることによる画像認識技術性能向上の両立にある。

【解決手段】

上記目的を達成するために、以下に設計データに基づいて、画像認識用のテンプレートを作成する際に、当該テンプレートによって特定される領域の材料情報に基づいて、当該テンプレート内の各位置の輝度情報を設定する方法,装置、及びプログラムを提案する。また、その一例として、材料の情報に加えて、上記領域上に配置されたパターンの大きさ,画像取得装置の装置条件,試料の層情報,パターンの線分情報の少なくとも1つの情報に基づいて、輝度レベルを設定する。

(もっと読む)

走査型電子顕微鏡及びこれを用いたパターン寸法計測方法

【課題】CD-SEMによる半導体パターンの寸法計測において,パターンの断面形状に依存して寸法計測値と実際のパターンの寸法との誤差が変動することにより、計測精度が悪くなる問題があった。

【解決手段】

予め形状の異なる複数パターンのAFM計測結果と,同一形状のパターンをCD-SEMで計測したときの前記AFM計測結果との寸法計測誤差とを対応付けてデータベースに保存しておき,実際の寸法計測時には,計測対象パターンの少数箇所から得たAFM計測結果を前記データベースに照合し,最も形状が類似した側壁形状に対応したCD-SEM計測の寸法計測誤差を呼び出し,次に計測対象パターンのCD-SEM計測結果を前記呼び出した寸法計測誤差に基づき補正することにより,パターンの断面形状に依存した寸法誤差を低減した補正寸法値を算出する。

(もっと読む)

電子顕微鏡システム及びそれを用いたレジストパターンの膜厚減少量評価方法

【課題】

本発明の目的は、インラインのプロセス管理の一環として適用が可能な,高スループットなレジストパターンの膜減り検知ないし,膜減り計測を実現するシステムを提供することにある。

【解決手段】

レジストパターンの膜減りがレジスト上面の面荒れ(ラフネス)を伴うことに着目し,従来の線幅計測に用いているレジストパターンの電子顕微鏡像上で,レジスト上面に相当する部位のラフネスの程度を定量化することによって膜減り指標値を算出する。また,予め作成しておいた膜減り指標値とレジストパターンの膜減り量を関連づけるデータベースに当てはめることによって,レジストパターンの膜減り量を推定する。

(もっと読む)

電子顕微鏡システム及びそれを用いたパターン寸法計測方法

【課題】

本発明の目的は,試料の実際のパターンエッジ端に即した輪郭線情報を出力する電子顕微鏡システムを提供することにある。

【解決手段】

電子顕微鏡像のパターンエッジの各点において,パターンエッジに対して接線方向に該電子顕微鏡像を投影して局所投影波形を生成し,各点で生成した局所投影波形を,予め作成しておいた,試料の断面形状と電子線信号波形とを関連づけるライブラリに当てはめることによって,試料上に転写されたパターンの断面形状を推定し,断面形状に則したエッジ端の位置座標を求め,この位置座標の連なりとしてパターンの輪郭線を出力する。

(もっと読む)

パターン寸法計測方法

【課題】

電子線シミュレーションを利用した,SEM画像によるパターン計測においては,シミュレーションの精度が非常に重要となる。シミュレーション画像と実画像のマッチングを行うためには,計測対象形状や材料を適切にモデル化し,シミュレーション画像に反映する必要がある。

【解決手段】

本発明では,SEM画像やAFMなど他の計測装置により得られた情報に基づいて,シミュレーションと実画像のマッチング計測の精度に与える影響が大きな形状や寸法を適切に設定したシミュレーション画像を用いることにより,高精度なパターン計測を実現するようにした。

(もっと読む)

集積回路パターンの欠陥検査方法、及びその装置

【課題】

半導体集積回路パターンの欠陥検査において、欠陥検査回数を制限しつつ、致命欠陥の管理を容易にする。

【解決手段】

半導体集積回路の設計者が設計したパターン設計情報5に加え、パターンの重要度をその設計意図に応じて順位付けした設計意図情報6を記憶する。また、露光装置を介して、設計された回路パターンをウエハ上に露光転写する際に、露光装置の特性等によってシステマティックに発生する欠陥を、あらかじめシミュレーションによって予測し、ホットスポット情報7として記憶する。これら設計意図情報6とホットスポット情報7を組み合わせることによって、半導体集積回路の特性に対して、システマティックな欠陥が発生可能性の高い検査場所を限定し、欠陥検査時間を大幅に短縮することができる。

(もっと読む)

計測方法

【課題】凹部の形状を正確に把握することができる計測方法を提供する。

【解決手段】絶縁膜に形成された凹部の底面に対する側壁の角度を測定する工程(処理S1)と、凹部の底面に対する側壁の角度、幅寸法、深さ寸法を含んだパラメータ群を複数設定し、複数のパラメータ群にそれぞれ関連づけられた複数の反射光の波形を有するライブラリを作成する工程(処理S2)と、凹部に対し光を照射する工程と(処理S4)、反射光を検出する工程(処理S5)と、反射光の波形と、ライブラリから選択した波形とを照合する工程(処理S6)と、反射光の波形とライブラリから選択した波形とのずれが所定値未満である場合に、選択した波形に関連づけられた凹部の幅寸法等のパラメータを最適値とし、凹部の形状を把握する工程を含む。ライブラリの複数のパラメータ群の凹部の底面に対する側壁の角度は処理S1での測定値である。

(もっと読む)

画像生成方法及びその画像生成装置

【課題】

設計データを制約条件として用い単調なパターンでも精度の良い連結画像を生成することを目的とする。設計データと画像データとのマッチングで大まかに基準位置を求めて、設計データとのズレ量を検索範囲として、隣接画像間でのマッチングを行い高速で精度の良い連結画像を生成する。

【解決手段】

本発明の画像生成方法は、走査型電子顕微鏡を用いて電子デバイスパターンを検査する画像生成方法であって、電子デバイスパターンのレイアウト情報が記述された設計データを入力して記憶した設計データファイルと、撮像位置を変えて前記電子デバイスパターンを撮像して得た複数枚の分割画像データと、前記複数枚の分割画像データと前記設計データファイルの設計データとを用いて前記複数枚の分割画像データを1枚の画像に連結する画像連結手段とで構成される。

(もっと読む)

パターン寸法測定方法、及びパターン寸法測定装置

【課題】エッジ部分のコントラストが希薄であってもラインプロファイルに基づくエッジを適切に判定し、パターンの測長を実行することのできるパターン寸法測定方法及び装置を提供する。

【解決手段】本発明は荷電粒子線の走査によって試料上に形成されたパターンの寸法を測定するパターン寸法測定方法及び装置に関する。当該方法及び装置では、荷電粒子線の走査によって、試料上の画像を形成し、形成された画像の一部の領域を選択し、選択された画像の一部の領域を他の像に置換し、画像の一部が他の像に置換された画像を用いて、パターンの寸法測定を行うようにしている。

(もっと読む)

試料の検査,測定方法、及び荷電粒子線装置

【課題】

外乱等の影響に依らず、焦点等の調整が行われた高画質画像に基づく測定が可能な試料

の検査,測定方法を提供すること。

【解決手段】

焦点調整が行われた電子ビームを走査して、前記パターンを測定するための画像、或いは測定のための位置合わせを行うための画像を形成し、当該画像の評価値と、予め取得された参照画像の画像評価値を比較し、当該参照画像との比較によって、前記形成された画像が所定の条件を満たさないと判断される場合に、前記電子ビームの焦点調整を再度実行する方法を提供する。

(もっと読む)

検査装置及び検査方法

【課題】探索画像中にテンプレートと類似したパターンが存在する場合でも正確なマッチング位置を出力する検査装置及び方法を提供する。

【解決手段】画像探索部にテンプレート選択画像におけるテンプレートの相対位置と探索画像における現在探索中の場所の相対位置を比較してその位置ずれ量を出力する相対位置比較部を有し、マッチング位置決定部において探索画像類似度分布情報のみならず、前記位置ずれ量をも考慮しマッチング位置を決定する。

(もっと読む)

半導体装置の製造方法

【課題】寸法検査工程において、回路パターンまたはQCパターンの活性化領域上のゲート電極寸法を高精度に計測し、半導体装置を安定して製造する。

【解決手段】測定対象の画像データから、配線幅プロファイルを取得し、設計データベースから活性化領域の幅やピッチなどの下層レイヤの寸法を取得し、活性上解析領域を幅、およびピッチで設定し、画像の端からの位置をxとする。活性上解析領域の配線幅の平均値をAEI_A(x)として計算する。位置xを0からTまで移動すると、配線幅の平均値AEI_A(x)は下層レイヤのピッチ構造に応じて変動する。下層レイヤの活性化領域と活性上解析領域が一致した場合、配線幅の平均値AEI_A(x)は最大値をとる。この極値を活性領域上のゲート電極寸法の計測結果とし、半導体装置の製造工程を管理する。

(もっと読む)

81 - 100 / 223

[ Back to top ]