Fターム[2G132AE18]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 記録 (518)

Fターム[2G132AE18]の下位に属するFターム

フェイルメモリ (120)

Fターム[2G132AE18]に分類される特許

21 - 40 / 398

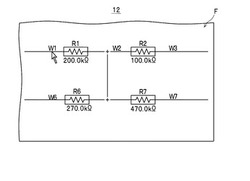

データ作成装置、基板検査装置およびデータ作成方法

【課題】部品実装基板に対して行う電気的検査において用いる検査用データを作成する際の入力作業を効率よくかつ正確に行う。

【解決手段】回路基板に電気部品(抵抗器R1,R2,R6,R7)が実装された部品実装基板に対して行う電気的検査において電気信号の入出力を行うための部品実装基板における検査ポイントを示すポイント情報を含む検査用データを作成する処理部と、ポイント情報を入力する操作が可能な操作部と、ポイント情報の入力時に参照させる図であって回路基板の配線(W1〜W3,W6,W7)および電気部品の配置を示す配置図Fを表示部12に表示させる表示制御部とを備え、操作部は、配置図F内に図示されている配線を選択する選択操作が可能に構成され、処理部は、選択操作によって選択された配線を示す情報をポイント情報として検査用データを作成する。

(もっと読む)

試験情報表示装置、方法、プログラム、および該ソフトウェアを格納したコンピュータ可読媒体

【課題】STILで記述された電子回路素子用試験プログラムから所望の試験情報を取得し、その取得した情報をユーザが見やすい形式で表示する装置を提供する。

【解決手段】STILで記述された電子回路素子用試験プログラムから所定の試験情報を取得し、その取得した情報を表示する試験情報表示装置(1000)は、前記試験プログラムを参照するプログラム参照手段(10)と、前記所定の試験情報に関連したコマンドを基に、前記参照した試験プログラムから該試験情報を含むデータブロックを取得するデータブロック取得手段(20)と、前記取得したデータブロックから前記所定の試験情報を取得する試験情報取得手段(20)と、前記取得した試験情報を配列する試験情報配列手段(40)と、前記配列された試験情報を表示する試験情報表示手段(50)と、を備える。

(もっと読む)

データ作成装置、基板検査装置およびデータ作成方法

【課題】検査ポイントや判定用の基準値を正確かつ効率的に設定する。

【解決手段】回路基板に電気部品が実装された部品実装基板に対して行う電気的検査において電気信号の入出力を行うための部品実装基板における検査ポイントを示すポイント情報を含む検査用データを作成可能に構成され、検査用データの作成時に参照させる図であって回路基板の配線および電気部品の配置を示す配置図F2を表示部12に表示させる表示制御部を備え、表示制御部は、配置図F2を表示させる際に、予め設定された条件を満たす電気部品の図示を省略して表示させる第1表示処理を実行可能に構成されている。

(もっと読む)

データ作成装置、基板検査装置およびデータ作成方法

【課題】部品実装基板に対して行う電気的検査において用いる検査用データを作成する際の入力作業の効率を向上させる。

【解決手段】回路基板に電気部品(抵抗器R1〜R8)が実装された部品実装基板における基板の配線(W1〜W7)上に規定されている規定ポイント(P1a〜P7b)の中から選択されて部品実装基板に対して行う電気的検査において電気信号の入出力を行うための検査ポイントを示すポイント情報を含む検査用データを作成する処理部と、配線および電気部品の配置を示す第1配置図を表示部12に表示させる表示制御部とを備え、表示制御部は、第1配置図内に図示されている配線を選択する第1選択操作が行われたときに規定ポイントの配置を示す第2配置図Fbを表示部12に表示させ、その際に、第1選択操作によって選択された配線上に規定されている規定ポイントを他の規定ポイントと識別可能に図示させる。

(もっと読む)

測定装置

【課題】被測定物の送信器と受信器を接続する試験を測定装置により行う。

【解決手段】送信部202と受信部204を有する被測定物200に接続される測定装置100は、送信部202に接続される入力ポート102と、受信部204に接続される出力ポート104と、出力信号を出力する信号出力部132、134と、入力信号の電力を測定する電力測定部145、155と、入力ポートが接続される部分を、出力ポート104および電力測定部145、155の一方または双方とすることができ、しかも、出力ポート104が接続される部分を、入力ポート102および信号出力部132、134の一方または双方とすることができる接続部(カプラ110、スイッチ120〜128)と、入力ポート102と出力ポート104とが接続される際に、出力ポート104から出力される出力ポート信号の電力を調整する電力調整部183、185とを備える。

(もっと読む)

半導体試験装置

【課題】複数の半導体デバイスを並列に接続した状態で、試験条件の異なる複数のシーケンスを実施するにあたって、配線長の違いなどを相殺するためのタイミングキャリブレーションを行う。そのために必要な補正データを試験装置にロードする時間は、半導体デバイスの総数およびシーケンスの総数に応じて増加する。したがって、総試験時間が増大する。

【解決手段】シーケンスごとに、補正データのロードを伴う並列試験と、補正データのロードが不要なシングル試験とを比較し、試験時間の短い方を選択して実行する。こうすることで、総試験時間を最小限に抑えることが出来る。

(もっと読む)

モニタリング装置及びモニタリングシステム

【課題】LSI等の不具合発生時の原因追求を容易化する。

【解決手段】LSI内又はLSIの近傍にモニタリング装置100を配置し、モニタリング装置100内で、周波数カウンタ20が、一定時間でのリングオシレータ10の発振周波数を計測し、計測した発振周波数を示す発振周波数情報を生成し、時刻カウンタ30が、周波数カウンタ20により発振周波数が計測された時刻を示す時刻情報を生成し、出力制御部80が、発振周波数情報と時刻情報とを対応付けて記憶装置90に出力し、記憶装置90が、発振周波数情報と時刻情報をログとして記憶する。これにより、LSIが起動してから不具合発生までの間の発振周波数の推移を観測することで遅延の相対的な変化を確認することができ、LSIの個体差を気にする必要がなく、不具合発生時の原因追求を容易化できる。

(もっと読む)

半導体装置の不良解析方法

【課題】差画像解析を用いた半導体装置の不良解析を短時間で、効率よく高精度に行う。

【解決手段】良品、および不良品サンプルの半導体装置にテストパターンの掃引を開始して顕微鏡により発光画像を取得する。取得した発光画像を囲う反応ボックスを設定してレイアウト座標系の位置データに変換し、良品サンプルの反応ボックスと不良品サンプルの反応ボックスとが重なっている面積を計算する。重なっている面積がしきい値より少ない反応ボックスを差分ボックスと判定し、その差分ボックスを発光解析コントローラに表示する。

(もっと読む)

半導体試験装置

【課題】 正極出力と負極出力との差分値に基づく良否判定にかかる時間を短縮して、被試験デバイスの階調テストに要する時間を短縮する半導体試験装置を提供する。

【解決手段】 本発明の代表的な構成は、FPDドライバ102の階調テストを行う半導体試験装置100において、FPDドライバ102のピンから出力される正極出力または負極出力をA/D変換するA/D変換器112a〜112nと、A/D変換された正極出力または負極出力の一方を記憶しておくメモリ118と、メモリ118に記憶された正極出力または負極出力の一方を出力したものと同じピンについて、A/D変換された負極出力または正極出力の他方の入力を受けて、正極出力と負極出力との差分値を逐次演算する差分演算回路114と、を有することを特徴とする。

(もっと読む)

デバイステスタ

【課題】過去に取得したデータを含めて、再度のシュムーデータの取得なしに複数のDUTのシュムーデータの全体的傾向を把握することが容易なデバイステスタを提供。

【解決手段】本発明の構成は、被試験デバイス(DUT140)の電気的試験を行うデバイステスタ100であって、被試験デバイスのシュムーデータを取得するシュムー取得部220と、取得したシュムーデータをファイルに保存するデータ保存部222と、ファイルからシュムーデータを読み出すデータ読出部228と、取得したシュムーデータおよびファイルから読み出したシュムーデータから1または2以上のシュムーデータをユーザに選択させるデータ選択部226と、選択された1または2以上のシュムーデータ同士をプロット単位で論理計算し、計算された重畳シュムーデータを表示部212に表示する重畳表示部230と、を備えることを特徴とする。

(もっと読む)

測定結果管理システム、管理サーバ、及び半導体集積回路装置

【課題】実際に稼動している半導体集積回路装置の実動作に影響を与える要因を解析し、更にその要因を低減することが可能な半導体集積回路装置を提供する。

【解決手段】測定対象である半導体集積回路131と、この半導体集積回路のジッタ又はノイズジッタ、ノイズ等の実動作に影響を与える物理量を測定する測定回路(半導体集積回路装置)130とを同一チップ上に構成する。測定回路の測定結果を解析し、測定対象の半導体集積回路を調整する回路にフィードバックさせる。

(もっと読む)

検査制御システム、検査方法、および検査制御プログラム

【課題】不良品の見逃しリスクを減少しつつ、所定のテスト量を減らして製造コストを削減する。

【解決手段】検査制御システム100は、所定の同一条件下で製造された複数の半導体装置について、一部の半導体装置ずつ順にテストを行い、各半導体装置への検査を制御する。検査制御システム100は、所定の同一条件下で製造された一部の半導体装置に対して所定のテスト量のテストを行った結果の良否判定の入力を受け付けるテスト結果入力受付部102、テスト結果入力受付部102が受け付けた結果に基づき、結果が良判定の場合は所定のテスト量を減少する一方、結果が不良判定の場合は所定のテスト量を増加して所定のテスト量を設定し直す設定更新部104、および次の一部の半導体装置に対してテストを行う際に、設定更新部104が設定し直した所定のテスト量のテストを行うよう制御するテスト実行制御部106を含む。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、前記回路ブロックがそれぞれ正常に動作し得る最小限度の電圧を供給する複数の電圧供給回路を備え、各前記回路ブロックへの最小限度の電圧を供給する制御内容を記憶する電源電圧制御メモリを有し、前記電源電圧制御メモリの記憶する制御内容に従って前記電圧供給回路が各前記回路ブロックに供給する電圧を切り替える電源切り替え手段を備えた半導体装置を用いる。

(もっと読む)

半導体装置

【課題】半導体装置の消費電力を低減しつつ、高速に動作させる。

【解決手段】半導体装置の回路が複数の回路ブロックに分割され、各前記回路ブロック毎に電源電圧を供給し、前記電源電圧を電圧調整回路により切り替える電圧供給回路を有し、前記電圧調整回路を切り替える電圧制御信号を記憶する電源電圧制御メモリを有する電圧設定回路を有し、前記半導体装置の回路の複数箇所に回路の電圧を検出する電圧検出スイッチを有し、前記電圧検出スイッチを指定することで電圧を検出する回路の位置を切り替え、且つ、前記電源電圧制御メモリにアドレスを指定して値を書き込む制御を行う回路スイッチ制御回路を有する半導体装置を用いる。

(もっと読む)

プロービング装置、検査装置および接続切替え方法

【課題】製造コストの低減を図りつつ、電気的パラメータを正確に測定させる。

【解決手段】電気的パラメータを測定する測定点(測定点Pa1〜Pa10のいずれか)にプロービングさせたプローブ(プローブPb1〜Pb10のいずれか)に対して付与されている第1の識別番号を測定手順データD1に基づいて特定し、かつ特定した第1の識別番号のプローブが接続されているプローブ接続部(接続部C1〜C10のいずれか)の第2の識別番号を、各プローブ接続部に対する各プローブの接続関係に応じて第1の識別番号および第2の識別番号を相互に対応付けた識別番号データD2に基づいて特定し、スキャナ4を制御して、特定した第2の識別番号のプローブ接続部に接続されているプローブを測定部5に接続させる。

(もっと読む)

故障診断装置、故障診断方法、及び故障診断プログラム

【課題】実測とシミュレーション結果に不一致が生じた場合に、不一致を生じている経路数だけでなく、不一致の時間的な大小を評価する。

【解決手段】本発明では、回路の後方追跡により抽出した故障候補から、候補の出力側に存在するスキャン回路(SFF)までの故障伝搬経路を、デジタル信号が伝搬する際に費やす遅延時間を求め、実測のテスト結果が不合格である経路の遅延が、合格である経路よりも大きい故障候補を、真の故障であると判定し、その大小関係に逆転(不一致)が生じた場合は、その時間的な逆転が統計的に小さい故障候補を、真の故障であると判定する。遅延が大きい経路は、それが小さい経路に比べて回路動作における時間的なマージンが小さく、遅延故障が発生した場合にテスト結果が不合格になりやすい。そのため、実測のテスト結果の合格/不合格と遅延時間の大小が上記に従う故障候補は、真の故障である可能性が高い。

(もっと読む)

オンチップジッタデータ取得回路、ジッタ測定装置、及びその方法

【課題】本発明は、高周波プローブを要さずにジッタ測定が可能なオンチップジッタデータ取得回路を提供することを目的とする。

【解決手段】本発明に係るオンチップジッタデータ取得回路1は、クロック信号を、遅延量選択信号で選択可能な複数の遅延量のいずれか1つの遅延量で遅延する可変遅延部10と、クロック信号の位相と、可変遅延部で遅延されたクロック信号の位相とを比較して、位相比較信号を生成する位相比較信号生成部20と、位相比較信号を所定の期間に亘り取得する位相比較信号取得部30と、を有することを特徴とする。

(もっと読む)

抜取検査の設計方法

【課題】スキップロットサンプリングに関する仮定が成立しない場合であっても、抜取検査を容易且つ高精度に設計する。

【解決手段】検査工程をスキップする頻度を示すスキップ頻度と、スキップ頻度に基づいて決まる非検査ロットの直前に連続するi(iは2以上の整数)個のロットのうち、少なくともq(qは2以上且つi以下の整数)個のロットが不合格であった場合に次の非検査ロットを検査ロットに変更するというスキップ条件と、を受け付け、スキップ条件を用いて検査工程を実行したと仮定したときの第1合格率を計算し、スキップ頻度及びスキップ条件を用いて検査工程を実行したと仮定したときのロットの総数に対する検査ロットの数の割合である検査率を計算し、製造ラインが停滞しない場合には、スキップ頻度をサンプリングプランとして決定し、製造ラインが停滞する場合には、スキップ頻度を変更し、サンプリングプランとして決定する。

(もっと読む)

信号測定装置、信号測定システムおよび半導体試験装置

【課題】変換特性の異なる複数のA/D変換器が同一時期にアナログ信号をサンプリングして変換したデータを、メモリに同一タイミングで記憶するためのタイミング調整を行う信号測定装置、信号測定システムおよび半導体試験装置を提供する。

【解決手段】被測定対象から出力されるアナログ信号をデジタル信号に変換し測定する信号測定装置において、アナログ信号を前記デジタル信号に変換する変換特性が互いに異なる複数の変換部20a、20bと、変換部によって変換された変換データを間引く間引き部37bと、変換部によって変換されたデータと間引き部によって間引かれたデータとを記憶する記憶部33a、33bと、変換部のサンプリングクロック周期と間引き部の間引き間隔とに基づいて、変換部でサンプリングされ変換されたデータと、このデータと同時期にサンプリングされ変換された後に間引き部によって間引かれたデータとを記憶部に記憶させるタイミングを合わせる調整部38bと、を備えたことを特徴とする

(もっと読む)

シミュレーションネットリスト作成装置、シミュレーションネットリスト作成方法、及びコンピュータプログラム

【課題】 回路における電源制御に関するシミュレーションの時間を削減する。

【解決手段】 回路を構成する部品の「部品情報110、端子情報120、及び端子間の接続情報100」に基づき、探索開始部品を特定する。そして、探索開始部品の電源端子及びリセット端子と、電源回路の制御ネット名とを探索始点とする。また、電源回路の入出力ネット名と、電源ネット名と、グランドネット名と、部品情報110に基づいて特定される探索終了部品とを探索終点とする。そして、探索始点から探索終点までの探索経路にある部品を探索し、当該部品の接続情報を特定し、探索経路にある部品のシミュレーションネットリストを作成する。

(もっと読む)

21 - 40 / 398

[ Back to top ]