Fターム[2G132AF11]の内容

Fターム[2G132AF11]の下位に属するFターム

粒子線(イオンビーム等)を使用するもの (23)

電子線(EB)を使用するもの (90)

レーザ、光を使用するもの (100)

磁気、静電誘導によるもの (77)

Fターム[2G132AF11]に分類される特許

1 - 20 / 42

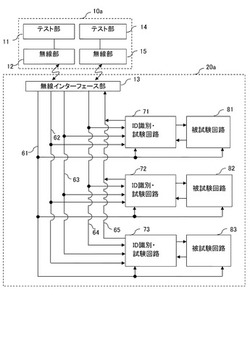

半導体集積回路、そのテスト方法及びテストシステム

【課題】テスト時間が短い半導体集積回路のテストシステム及びテスト方法を提供する。

【解決手段】本発明にかかる半導体集積回路20は、複数の被試験回路81乃至83を有し、外部のテストシステム10と無線で通信することにより、被試験回路81乃至83をそれぞれテストする複数のテストパターンに、被試験回路81乃至83を識別するIDが付加されたテスト入力信号を受信する無線インターフェース部13と、IDを識別し、IDに対応する被試験回路81乃至83に、IDが付加されたテスト入力信号に含まれるテストパターンを入力し、被試験回路81乃至83からテストパターンに応じたテスト結果が出力される度に、テスト結果に、IDを付加したテスト出力信号を、無線インターフェース部を介して、外部のテストシステム10に出力する試験回路と、を有するものである。

(もっと読む)

試料検査装置及び吸収電流像の作成方法

【課題】複数本の探針を用いて検出された吸収電流から、入力間の増幅率の差を含むことなく鮮明な吸収電流像を取得し、測定効率を向上させることができる試料検査装置及び吸収電流像の作成方法を提供する。

【解決手段】複数の探針4を試料2に接触させ、試料2に電子線1を照射しつつ、探針4に流れる電流を測定し、少なくとも2本の探針4からの信号を差動増幅器6に入力する。そして、差動増幅器6からの出力を増幅し、これと電子線1の走査情報に基づいて吸収電流像7を作成する。これにより、入力間の増幅率の差を含むことなく鮮明な吸収電流像7を取得でき、半導体試料2の不良解析の測定効率を向上できる。

(もっと読む)

半導体素子の故障解析方法及び故障解析装置

【課題】本発明は、半導体素子の故障解析方法及び故障解析装置に係り、故障箇所を位置精度よく特定して解析することにある。

【解決手段】コントローラに、半導体素子への電力供給により該半導体素子の裏面から発せられる光を撮像手段にて検出させることにより該半導体素子の故障箇所を特定させる。次に、半導体素子の表面電極側に配置された圧痕用プローブを該半導体素子の表面電極に接触させ、かかる状況において、半導体素子の表面電極側から該表面電極へレーザを走査照射した場合に得られる走査位置と電流量との関係を示した電流像に基づいて、半導体素子の表面電極上で圧痕用プローブが接触する接触箇所を特定させる。そして、半導体素子上で特定した故障箇所と接触箇所との位置ズレ量に基づいて、圧痕用プローブを前記半導体素子の表面電極に接触させる位置を変更させる。

(もっと読む)

検査データと組み合わせて設計データを使用するための方法及びシステム

【課題】検査データと組み合わせて設計データを使用するためのさまざまな方法及びシステムが実現される。

【解決手段】設計データ空間における検査データの位置を決定するための一コンピュータ実施方法は、ウェハ上のアライメント部位に対する検査システムにより取り込まれたデータを所定のアライメント部位に対するデータにアラインさせることを含む。この方法は、さらに、設計データ空間における所定のアライメント部位の位置に基づいて設計データ空間におけるウェハ上のアライメント部位の位置を決定することを含む。それに加えて、この方法は、設計データ空間におけるウェハ上のアライメント部位の位置に基づいて設計データ空間における検査システムによりそのウェハについて取り込まれた検査データの位置を決定することを含む。一実施形態では、検査データの位置は、サブピクセル精度で決定される。

(もっと読む)

電磁ノイズ分布検出装置

【課題】機器内で発生する電磁ノイズと同じ周波数の試験信号を注入した場合の近似的な分布を得ることのできる電磁ノイズ分布検出装置を得る。

【解決手段】信号発生器1は、供試機器100内で発生する電磁ノイズの周波数から僅かにずらした周波数の信号を出力し、注入プローブ3によって供試機器100に注入する。検出プローブ4は可動部7により供試機器100上を走査し、供試機器100の電磁界分布を検出し、電磁界強度計6によって電磁界強度の分布を測定する。ノイズ分布検出手段11は、電磁界強度計6で測定された電磁界強度の分布を、供試機器100内で発生する電磁ノイズの近似的な分布として検出する。

(もっと読む)

RFIDタグの検査ラインシステム

【課題】僅かな不良であっても確実に品質不良を発見することができるRFIDタグの検査ラインシステムを提供する。

【解決手段】検査ラインシステム1は、アンテナ回路が形成された基板21が巻き取られ、基板21を下流側に供給する基板供給ロール装置11と、基板供給ロール装置11から供給された基板21を巻き取る基板巻取りロール装置17からなるロール・ツー・ロール方式であって、基板供給ロール装置11と基板巻取りロール装置17との間に配置され、アンテナ回路の電気的導通検査を行う回路抵抗測定検査手段13と、アンテナ回路の外観検査を行う外観画像処理検査手段14と、アンテナ回路の共振周波数の測定検査を行う共振周波数測定検査手段15と、各検査の結果に応じてアンテナ回路の正常或いは異常の判定を行う合否判定手段と、を備える。

(もっと読む)

半導体装置の不良解析方法

【課題】差画像解析を用いた半導体装置の不良解析を短時間で、効率よく高精度に行う。

【解決手段】良品、および不良品サンプルの半導体装置にテストパターンの掃引を開始して顕微鏡により発光画像を取得する。取得した発光画像を囲う反応ボックスを設定してレイアウト座標系の位置データに変換し、良品サンプルの反応ボックスと不良品サンプルの反応ボックスとが重なっている面積を計算する。重なっている面積がしきい値より少ない反応ボックスを差分ボックスと判定し、その差分ボックスを発光解析コントローラに表示する。

(もっと読む)

半導体装置

【課題】配線にプローバを立てないで済む、より簡便な検査方法の確立、及び該検査方法

を用いる検査装置の提供。

【解決手段】電磁誘導によって素子基板の配線に起電力を生じさせることにより、該配線

に電流を流して検査を行う。非接触にて前記回路または回路素子に電圧を印加することで

、前記回路または回路素子を動作させ、前記回路または回路素子から出力された電圧を非

接触で読み取り、前記回路または回路素子の良否を判定することを特徴とする検査方法。

(もっと読む)

プローブカード及びそれを備えた半導体装置の検査装置並びに半導体装置の検査方法

【課題】接触方式及び非接触方式の両方式を用いて供給することが可能な半導体装置の検査において、異なる種類の半導体装置を検査する際の検査に要するコストが増大し、さらに、微細ピッチで配置された半導体装置を検査できない。

【解決手段】本発明のプローブカードは、基板と、基板上に、第1の方向に第1の間隔で配置された複数の接触端子部と、基板上に、第1の方向に第2の間隔で配置された複数の非接触インタフェースと、を備え、非接触インタフェースが第1の方向に第2の間隔で配置された領域に含まれる有効プローブカード領域であって、有効プローブカード領域の両端に配置された非接触インタフェース間の距離である有効プローブカード長さが、第1の間隔と第2の間隔の最小公倍数の整数倍である。

(もっと読む)

半導体装置、半導体ウエハおよびその電源制御方法

【課題】電源供給構造を備えた半導体装置において、外部測定装置のコストの増大を招くことなく、電源回路を正確に制御することが困難である。

【解決手段】本発明の半導体装置は、主回路部と、電源配線部と、無線信号を受信し制御信号を出力する無線回路部と、電源配線部と主回路部に接続され、無線回路部からの制御信号に基づき、主回路部への電源供給状態を制御する第一の電源回路部と、電源配線部と無線回路部に接続され、無線回路部への電源供給状態を制御する第二の電源回路部とを有する。

(もっと読む)

被検査装置用インタフェース回路及び、検査方法

【課題】簡単な構成で入出力状態が制御できる被検査装置用インタフェース回路2を提供する。

【解決手段】被検査装置本体7と該被検査装置本体7を検査する検査装置6とを非接触で通信させる第1のアンテナ部3と、第1のアンテナ部3を入力状態又は出力状態に切替える第1の制御部4と、を備える。

(もっと読む)

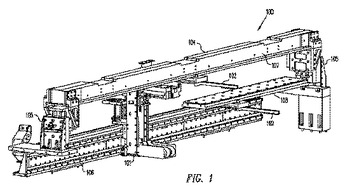

自動プローブ構成ステーション及びその方法

被試験デバイスの検査を容易にするプローブ・システム。システムは、ストレージ・ラック、プローブ・バー・ガントリー・アセンブリ、被試験デバイスに電気的に合わさるように構成されるプローブ・アセンブリ、及びプローブ・アセンブリをストレージ・ラックから取出し、プローブ・アセンブリをプローブ・バー・ガントリーに引渡すロボット・システムを組込む。ロボット・システムは、プローブ・バー・ガントリーからプローブ・アセンブリを取出し、プローブ・アセンブリをストレージ・ラックに引渡すことも可能である。プローブ・アセンブリは、プローブ・アセンブリをプローブ・バー・ガントリー又はストレージ・ラックに取付けるクランプ・アセンブリを含む。プローブ・アセンブリは、プローブ・アセンブリがプローブ・バー・ガントリー・アセンブリ上に設置されると、被試験デバイス上の導電性パッドに合わさるように構成されたコンタクト・ピンのアレイを含む。  (もっと読む)

(もっと読む)

回路基板検査装置および回路基板検査方法

【課題】小型の集積回路や底面に端子が形成された集積回路が実装された検査対象基板、および内層実装型の検査対象基板を短時間で確実に検査する。

【解決手段】集積回路X1,X2・・が実装された検査対象基板Pの良否を電気的に検査する回路基板検査装置であって、検査対象の集積回路Xに電磁波を選択的に照射した状態において、集積回路Xにおける電源端子Tvが接続されているべき電源パターンPvと信号端子Tsが接続されているべき信号パターンPsとの間の電気的パラメータ、および信号パターンPsと集積回路Xにおけるグランド端子Tgが接続されているべきグランドパターンPgとの間の電気的パラメータを測定し、測定した電気的パラメータに基づいて各導体パターンPv,Ps,Pgに対する各端子Tv,Ts,Tgの接続状態の良否を検査する。

(もっと読む)

集積回路の並行検査の方法、装置及びシステム

【課題】 検査コストを低減し、製品化までの時間を短縮し、欠陥デバイスが合格デバイスとして通過してしまう誤りの率を低下できる集積回路の検査の方法、装置及びシステムを提供する。

【解決手段】 本発明の装置では、共通の基板に、複数の被検査デバイス(DUT)と、複数の比較装置が設けられる。この複数のDUTは、すべて同一の入力刺激で動作し、各々が実行結果を発生する。この実行結果は比較装置で比較されて、比較特徴が生成され、その特徴により、欠陥のある被検査デバイスを検出する。

(もっと読む)

半導体装置の製造方法及びTEG素子

【課題】TEGの被検査配線に非接触で電位を印加し、非接触で被検査配線の欠陥の有無及び位置を迅速に特定する。

【解決手段】半導体基板1の上面に光起電力素子2を形成し、光起電力素子2上に形成された絶縁層3上面に、一端が光起電力素子2の正電極2−1に接続されかつ他端が光起電力素子2の負電極2−2に接続された被検査配線4tを形成し、半導体基板1下面から光11を入射して光起電力素子2を励起して被検査配線4tの両端に電位差を発生させ、非接触走査型表面電位顕微鏡を用いて被検査配線4tの表面電位分布を測定する工程とを有する。

(もっと読む)

半導体装置の診断装置及び診断方法

【課題】半導体装置の診断の所要時間を短縮し、且つ、診断の精度を向上させるための半導体装置の診断装置及び診断方法を提供する。

【解決手段】発光解析によって取得された半導体装置の各セルのトランジスタの発光像情報、並びにレイアウトを含む設計情報に基づいて、発光像情報の発光位置情報に対応する故障セルリストを作成し、設計情報から接続関係を示すトランジスタ回路網リスト及び診断パターンを作成する故障セルリスト作成部14aと、設計情報、診断パターン、及び故障辞書に基づいて、セル内のトランジスタの基板電流に関するシミュレーションを実行して、セル内のトランジスタの基板電流を含む発光箇所辞書を作成する発光箇所辞書作成部14cと、発光像情報、設計情報、及び発光箇所辞書に基づいて、第1故障回路網候補の中から第2故障回路網候補を抽出する故障回路網抽出部14dと、第2故障回路網候補を出力する出力部18と、を備えている。

(もっと読む)

非接触導通試験方法および装置

【課題】絶縁試験用のプローブと試験対象部品の電極との導通を、プローブを試験対象部品に装着した状態で確認することのできる非接触導通試験装置および方法を提供する。

【解決手段】試験対象部品(10)が具備する電極(11、12、13・・・)間の絶縁試験に先立って実行する絶縁試験用のプローブ20と電極間の導通を確認する非接触導通試験方法であって、導電性の本体(21)と本体から突出する突出部(22)と本体および突出部を覆う絶縁層(23)とから成るプローブと、プローブを装着した試験対象部品を装着可能な装着部(41)と部品装着部にプローブを装着した試験対象部品を装着したときにプローブの突出部を受容する受容部(42)とから成る絶縁層(44)で覆われた導電性の試験用基板(40)と、を使用する。

(もっと読む)

光子放出に基づいた欠陥検知のためのシステム及び方法

【課題】光子放出を利用して集積回路中の欠陥デバイスを検出する方法を提供する。

【解決手段】集積回路160の領域から放出画像(IREM)を取得するステップと、集積回路の前記領域に存在する各デバイスからの放出の決定強度を提供するために、強度の値を決定するステップと、各デバイスに対応する参照強度を取得するステップと、強度が参照強度に対して描画され、曲線適合計算が実行されて計算強度と参照強度との直線関係が取得され、最大偏差が、標準偏差計算のような計算によるか、ユーザによる手動入力によって、各決定強度を対応する参照強度と比較するステップとを備える。

(もっと読む)

試料検査装置及び吸収電流像の作成方法

【課題】本発明の目的は、複数本の探針を用いて検出された吸収電流から、入力間の増幅率の差を含むことなく鮮明な吸収電流像を取得し、測定効率を向上させることに関する。

【解決手段】本発明では、複数の探針を試料に接触させ、試料に電子線を照射しつつ、探針に流れる電流を測定し、少なくとも2本の探針からの信号を差動増幅器に入力する。そして、差動増幅器からの出力を増幅し、これと電子線の走査情報に基づいて吸収電流像を作成することに関する。本発明により、入力間の増幅率の差を含むことなく鮮明な吸収電流像を取得でき、半導体試料の不良解析の測定効率を向上できる。

(もっと読む)

半導体集積回路の故障解析方法及び故障解析装置

【課題】半導体集積回路の故障解析について、解析装置から得られる検出信号に対する物理的な故障原因を容易に特定できる半導体集積回路の故障解析方法、解析装置、解析プログラムを提供する。

【解決手段】半導体集積回路チップの製造時に半導体ウエハー内の物理的な欠陥について外観検査等により検査し(S1)、半導体集積回路チップの論理動作試験を行い動作不良チップを抽出し(S2)、解析装置により動作不良チップから観測される検出信号について解析を行い検出信号が検出された座標と層とを取得し(S3)、設計データと検出信号の座標と層とを用いて検出信号が検出されたセルまたはネットと接続する回路の層と座標とを求め(S4)、その回路の層及び座標と、物理欠陥の検出された検査工程及びその物理欠陥のチップ内座標と、を照合し回路と関連する物理欠陥を特定する(S5)。

(もっと読む)

1 - 20 / 42

[ Back to top ]