Fターム[2H092GA29]の内容

液晶−電極、アクティブマトリックス (131,435) | 電極の構造 (19,386) | 表示領域内電極の構造(アクティブを除く) (7,836) | 画素電極と配線電極との接続 (1,333) | スルーホール (1,194)

Fターム[2H092GA29]に分類される特許

101 - 120 / 1,194

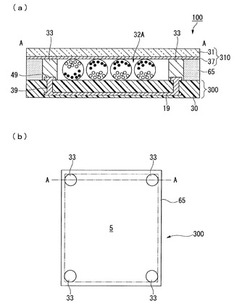

電気装置

【課題】薄くて軽くかつフレキシブル性を有した電気装置を提供する。

【解決手段】本発明の電気装置は、機能素子を挟んで対向配置された第1基板および第2基板と、機能素子よりも第1基板側に設けられた第1電極(裏面電極)と、第2基板に設けられ第1電極と電気的に接続された第2電極と、第1基板と第2基板とが重なる領域であって第1電極と第2電極との間に挟まれた領域に、機能素子と、当該機能素子を駆動する電子部品とが設けられている。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタの作製に用いるフォトリソグラフィ工程を従来よりも少なくし、且つ、信頼性の高い半導体装置を提供する。

【解決手段】第1の基板上に酸化物半導体層を有するトランジスタを含む回路と、当該第1の基板とシール材で固定された第2の基板とを有し、当該シール材、当該第1の基板、及び当該第2の基板で囲まれる閉空間は、減圧状態、或いは乾燥空気を充填する半導体装置に関する。当該シール材は、少なくとも前記トランジスタを囲み、閉じられたパターン形状を有する。また当該回路は、酸化物半導体層を有するトランジスタを含む駆動回路である。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

タッチスクリーンパネル一体型液晶表示装置及びその駆動方法

【課題】工程時間及び工程コストを減少させ、厚さが薄いタッチスクリーンパネル一体型液晶表示装置を提供する。

【解決手段】複数のデータ配線D1〜Dm及び複数の群に区分される複数のゲート配線G1〜Gnにそれぞれ連結される複数の画素P、複数の感知電極、複数の群に区分される複数の共通電極、共通電極の複数の群について、同一の群に含まれる共通電極には同時に駆動信号を供給する一方で、異なる群については各群を基準に駆動信号を順次に供給する共通電極駆動部5、並びにゲート配線G1〜Gnの複数の群について、各群別に各群に属するゲート配線にゲート信号を順次に供給するゲート駆動部3を含むタッチスクリーンパネル一体型液晶表示装置。

(もっと読む)

液晶表示装置

【課題】コントラスト比と広視野角を同時に確保することができ、液晶分子の応答速度を速くすることができるだけでなく、優れた表示特性を示す液晶表示装置を提供する。

【解決手段】本発明の実施形態にかかる液晶表示装置は、互いに対向する第1基板および第2基板と、第1および第2基板の間に介在しており、液晶分子を含む液晶層と、第1基板の上に配置されており、互いに分離されている第1画素電極および第2画素電極とを含み、第1画素電極および第2画素電極の1つは、データ線を介して第1電圧が印加され、第1画素電極および第2画素電極の残りの1つは、電圧伝達線を介して第2電圧が印加され、第1画素電極および第2画素電極は、幹部と、幹部から延びた複数の枝電極とを含み、第1画素電極の枝電極と第2画素電極の枝電極は交互に配置されており、第1画素電極および第2画素電極の幹部は、電圧伝達線と少なくとも一部重畳する。

(もっと読む)

半導体装置の作製方法

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

電気光学装置及び電子機器

【課題】電気光学装置において、積層構造の単純化を図り、しかも高品質な表示を可能とする。

【解決手段】電気光学装置は、基板上に、データ線(6)に接続された第1ソースドレイン領域、及び画素電極(9)に接続された第2ソースドレイン領域を含んでなる半導体層(30a)と、半導体層と画素電極との間に配置され、一の走査線(11)に接続されたゲート電極(30b)とを有するトランジスター(30)と、一の走査線に隣り合う走査線に接続された第2トランジスターのゲート電極が延在してなる第1容量電極と、第1容量電極と画素電極との間に設けられるとともに第2ソースドレイン領域に接続された第2容量電極とを有する蓄積容量(70)とを備える。蓄積容量は、半導体層とゲート電極との間の絶縁膜及び半導体層と基板との間の絶縁膜を貫通するとともに基板に設けられた溝内の少なくとも一部に設けられている。

(もっと読む)

薄膜トランジスター表示板およびその製造方法

【課題】薄膜トランジスター表示板およびその製造方法の提供。

【解決手段】本発明の実施形態による薄膜トランジスター表示板は、絶縁基板と、前記絶縁基板の上に位置するゲート線と、前記ゲート線と交差するデータ線と、前記ゲート線およびデータ線と連結されている薄膜トランジスターと、前記薄膜トランジスターのゲート電極と前記薄膜トランジスターの半導体との間に位置するゲート絶縁膜と、前記薄膜トランジスターと連結されている画素電極と、前記画素電極と前記薄膜トランジスターとの間に位置する保護膜と、を備え、前記ゲート絶縁膜および前記保護膜のうちの少なくとも一方は、窒化シリコン膜を含み、前記窒化シリコン膜は、2×1022cm3以下または4atomic%以下にて水素を含む。

(もっと読む)

液晶表示素子、表示装置、観察装置およびカメラ

【課題】配線の簡略化を図ることができる液晶表示素子を提供する。

【解決手段】基板に形成された電極930に電圧を印加して液晶の配向を制御することにより標識を表示する液晶表示素子において、電極930は、環状の閉じた形状を成す標識用電極931、標識用電極931の周囲に配置された周辺電極933、および標識用電極931によって囲まれた孤立電極932を有し、電極930と基板との間に配設され、標識用電極931、周辺電極933および孤立電極932に対応するスルーホールH1~H4がそれぞれ形成された電気的絶縁層920と、電気的絶縁層920と基板との間に配設され、スルーホールH2,H4を介して周辺電極933と孤立電極932とを電気的に接続する配線913が形成された配線層910とを備える。

(もっと読む)

液晶表示装置及び電子機器

【課題】液晶素子に印加される電圧を異ならせて視野角特性を改善する。

【解決手段】 本発明の一は、一画素に三以上の液晶素子を有し、該液晶素子の各々に印

加される電圧値が異なる液晶表示装置である。各液晶素子に印加される電圧を異ならせる

には、加えた電圧を分圧する素子を配置することにより行う。印加される電圧を異ならせ

るためには、容量素子、抵抗素子、又はトランジスタ等を用いる。

(もっと読む)

薄膜トランジスタ液晶ディスプレーのアレイ基板およびその製造方法

【課題】薄膜トランジスタ液晶ディスプレーのアレイ基板及びその製造方法を提供する。

【解決手段】アレイ基板は画素領域を画成するゲートラインとデータラインとを備え、前記画素領域内に薄膜トランジスタ、共通電極および電極ストリップ構造の画素電極とが形成され、前記共通電極は前記データラインを覆う第2絶縁層上に形成され、前記画素電極は前記共通電極を覆う第3絶縁層上に形成される。これによって、表示領域の面積が拡大され、開口率が効果的に向上される。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

液晶パネル

【課題】液晶を挟む2つの基板のうち一方の基板に、複数の薄膜トランジスタと複数の信号線と複数の走査線とに加えて、カラーフィルタ層が形成された液晶パネルにおいて、各画素の開口率を向上する。

【解決手段】第1の基板10には、カラーフィルタ層を形成する複数の色材膜18が形成されている。隣接する2つの色材膜18の間には、それらを区画する仕切り部32が形成されている。共通電極21は、一方の色材膜18の上側から仕切り部32の上側を越えて他方の色材膜18の上側まで続いている。

(もっと読む)

画素構造、表示装置、及び、電子機器

【課題】2つの副画素電極を電気的に接続するに当り、高精細化の妨げとならない画素構造、当該画素構造を用いた表示装置、及び、当該表示装置を有する電子機器を提供する。

【解決手段】回路部が形成された基板上に設けられる平坦化膜を、第1,第2の平坦化膜51,52からなる2層構造とし、この2層構造の2つの平坦化膜51,52間に金属配線53を形成する。そして、この金属配線53により、第2の平坦化膜52に形成されたコンタクト部56,57を介して、第2の平坦化膜52上に配された2つの副画素電極46A,46Bを電気的に接続する。

(もっと読む)

表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い表示装置を提供する。消費電力が少なく、信頼性の高い表示装置を提供する。

【解決手段】トランジスタの、ゲート電極となる導電層、ゲート絶縁層となる絶縁層、半導体層、およびチャネル保護層となる絶縁層を連続して形成する。ゲート電極(同一層で形成される他の電極または配線を含む)と島状半導体層の形成を、一回のフォトリソグラフィ工程で行う。該フォトリソグラフィ工程と、コンタクトホールを形成するフォトリソグラフィ工程と、ソース電極及びドレイン電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程と、画素電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程の、4つのフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

多層薄膜パターン及び表示装置の製造方法

【課題】間便に所望の形状のパターンを得ることのできる多層薄膜パターン及び表示装置の製造方法を提供すること。

【解決手段】基板上に層間絶縁膜1を形成する工程と、層間絶縁膜1上に導電性を有する第1の薄膜2を形成する工程と、第1の薄膜2上に第2の薄膜3を形成する工程と、第2の薄膜3上に、複数階調露光によって膜厚差を有するレジストパターン5を形成する工程と、膜厚差を有するレジストパターン5を介して、第2の薄膜3及び第1の薄膜2をエッチングして、レジストパターンの存在しない領域の層間絶縁膜1を露出させる工程と、膜厚差を有するレジストパターン5をアッシングして、レジストパターンの薄膜部5bを除去する工程と、薄膜部5bが除去されたレジストパターン5cを介して、第2の薄膜3をエッチングする工程と、を順次実施する。

(もっと読む)

液晶表示装置

【課題】表示品位の良好な液晶表示装置を提供する。

【解決手段】所定の間隔をおいて対向配置された第1基板及び第2基板と、前記第1基板の前記第2基板と対向する側に配置され、前記第2基板を支持し前記第2基板との間にセルギャップを形成するスペーサと、前記第1基板と前記第2基板との間の前記セルギャップに保持されるとともに、前記第1基板と前記第2基板とに間に形成される縦電界が印加される液晶層と、前記第1基板の前記第2基板と対向する側において各画素の周辺に配置され、前記第2基板から離間し前記第2基板との間に空隙を形成する壁部と、前記スペーサ及び前記壁部を覆う配向膜と、を備えたことを特徴とする液晶表示装置。

(もっと読む)

表示装置用基板及びそれを用いた液晶表示装置

【課題】本発明は、静電気流入による層間短絡などの障害が生じたとしても容易に修復することのできる表示装置用基板を提供することを目的とする。

【解決手段】基板1上の表示領域内に配設され、表示領域の内方より表示領域の外方に向けて引き出し形成される第1の配線部10を有する。さらに、基板1上の表示領域の外の第1の配線部10と絶縁膜を介して交差して形成される第2の配線部70を有する。さらに、第2の配線部70に形成され、少なくとも交差する第1の配線部10と重なり合う領域に開口した開口部72を有する。さらに、開口部72の両端に形成され、絶縁膜を介して第1及び第2の配線部10、70が重なり合う重畳部74を有する。

(もっと読む)

液晶表示装置

【課題】 製造コストの増大を抑制しつつ低温気泡の発生を抑制し且つ耐荷重性を確保する。

【解決手段】 スイッチング素子の上に配置された着色層と、前記着色層の上に配置された樹脂層と、前記樹脂層の上に配置され前記着色層及び前記樹脂層に形成されたコンタクトホールを介して前記スイッチング素子と電気的に接続された画素電極と、を備えた第1基板と、前記第1基板に対向して配置された第2基板と、前記第1基板の前記第2基板と対向する側に配置され、前記第2基板を支持し前記第2基板との間にセルギャップを形成するスペーサと、前記第1基板と前記第2基板との間の前記セルギャップに保持された液晶層と、を備え、前記スペーサは、前記コンタクトホールの内側において前記着色層及び前記樹脂層の少なくとも一方が欠落した領域と、前記コンタクトホールの外側において前記着色層の上に前記樹脂層が積層された領域と、に跨って配置されたことを特徴とする液晶表示装置。

(もっと読む)

表示装置

【課題】本発明は、アクティブマトリクス型表示装置の製造コストを低減するこ

とを課題とし、安価な表示装置を提供することを課題とする。また、本発明の表

示装置を表示部に用いた安価な電子装置を提供することを目的とする。

【解決手段】 アクティブマトリクス型表示装置の製造コストを低減するために

画素部に用いるTFTを全て一導電型TFT(ここではpチャネル型TFTもし

くはnチャネル型TFTのいずれか一方を指す)とし、さらに駆動回路もすべて

画素部と同じ導電型のTFTで形成することを特徴とする。これにより製造工程

を大幅に削減し製造コストを低減することが可能となる。

(もっと読む)

101 - 120 / 1,194

[ Back to top ]