Fターム[2H092JA46]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子 (19,865) | 三端子素子 (19,408) | 構造 (10,751) | 素子と画素電極との接続 (3,242) | スルーホール (2,664)

Fターム[2H092JA46]に分類される特許

141 - 160 / 2,664

半導体装置

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層421と、ゲート電極層上に設けられるゲート絶縁層402と、ゲート絶縁層上に設けられる第1の酸化物半導体層442と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層443と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層の幅を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制する。

【解決手段】ボトムゲート電極12aと第1のブラックマトリックス層17aで第1の半導体層14を挟むシングルゲート型の薄膜トランジスタを有する半導体装置であって、前記第1の半導体層と前記第1のブラックマトリックス層は重畳している半導体装置である。

(もっと読む)

電気光学装置、及び電子機器

【課題】不良の発生が抑制され高いコストパフォーマンスを有する電気光学装置、及び電子機器を提供する。

【解決手段】素子基板上に設けられた、TFT30と、TFT30に対応して設けられた画素電極15と、TFT30と画素電極15との間に設けられたデータ線6aと、データ線6aと画素電極15との間に設けられた第1容量電極16aと、第1容量電極16aと画素電極15との間に設けられ、第1容量電極16aの一部に誘電体層を介して対向配置されると共に、電気的にTFT30と画素電極15とに接続された第2容量電極16bと、を備え、第2容量電極16bは、アモルファスタングステンシリサイド膜からなる。

(もっと読む)

液晶表示装置およびマザー基板

【課題】TFT基板に有機パッシベーション膜が形成されておらず、かつ、TFT基板と対向基板との間隔を柱状スペーサによって規定する液晶表示装置において、TFT基板と対向基板との間隔を一定とする。

【解決手段】液晶表示パネルの表示領域では、TFT基板100と対向基板200との間隔は柱状スペーサ150によって規定している。液晶表示パネル内において、画素も走査線も映像信号線も形成されていない部分においても、柱状スペーサ150によって間隔を規定する。この場合、柱状スペーサ150の台座140が必要となるが、台座140の層構造は、表示領域において間隔を規定する柱状スペーサ150が接触するTFT基板側の層構造と同一にする。これによって、製造コストの上昇をともなうことなく、液晶表示パネルの液晶層300の間隔を一定にでき、輝度むら、あるいは色むらを防止することが出来る。

(もっと読む)

電気光学装置および投射型表示装置

【課題】反射性画素電極の上層側に絶縁膜が形成されているか否かにかかわらず端子電極を設けることができるとともに、深いコンタクトホールを形成しなくても端子電極の導通を図ることができる電気光学装置、および投射型表示装置を提供すること。

【解決手段】電気光学装置100において、端子電極102は、反射性の画素電極9aと同一の層に設けられているとともに、画素電極9aを構成する導電膜と同一種類の導電材料からなる。このため、画素電極9aの上層側に平坦化膜17等の絶縁膜が形成されているか否かにかかわらず、端子電極102を構成することができる。また、端子電極102を導通させるためのコンタクトホール45sが浅い。画素電極9aおよび端子電極102の上層側には平坦化膜17が設けられており、平坦化膜17の端子電極102と重なる領域には開口部17sが設けられている。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法

【課題】薄膜トランジスタ、薄膜トランジスタパネル、及びこれらを製造する方法に関する。

【解決手段】薄膜トランジスタは、ゲート電極、ゲート絶縁膜、上記ゲート絶縁膜上に形成された酸化物半導体層、及び上記酸化物半導体層上に相互に離隔して形成されたドレーン電極及びソース電極を含む。上記ドレーン電極は、上記酸化物半導体層上に形成された第1のドレーン副電極及び上記第1のドレーン副電極上に形成された第2のドレーン副電極を含む。上記ソース電極は、上記酸化物半導体層上に形成された第1のソース副電極及び上記第1のソース副電極上に形成された第2のソース副電極を含む。上記第1のドレーン副電極及び上記第1のソース副電極は、ガリウム亜鉛酸化物(GaZnO)を含み、上記第2のドレーン副電極及び上記第2のソース副電極は、金属原子を含む。

(もっと読む)

液晶表示装置

【課題】 製造歩留まりの低下を抑制する液晶表示装置を提供する。

【解決手段】 マトリクス状に配置された複数の表示画素PXを含む表示領域25と、複数の表示画素PXを駆動する駆動配線11、12と、駆動配線11、12の上層に配置されパターン端部に膜厚の薄い薄膜部23が設けられている平坦化膜20と、平坦化膜20上において平坦化膜20のパターン端部を横切って配置された第1電極30と、を備えたアレイ基板110と、アレイ基板110と対向して配置された対向基板120と、アレイ基板110と対向基板120との間に挟持された液晶層70と、を備えた液晶表示装置。

(もっと読む)

液晶表示装置及びその製造方法

【課題】歩留まりの低下を抑制することが可能な液晶表示装置及びその製造方法を提供する。

【解決手段】スイッチング素子と、前記スイッチング素子の上に配置され前記スイッチング素子まで貫通した第1コンタクトホールを有する有機絶縁膜と、前記有機絶縁膜の上に形成され前記第1コンタクトホールを介して前記スイッチング素子に電気的に接続された島状の中継電極と、前記有機絶縁膜の上に形成され前記中継電極から離間した共通電極と、前記中継電極及び前記共通電極の上に配置され前記第1コンタクトホールの直上の位置とは異なる位置で前記中継電極まで貫通した第2コンタクトホールを有する層間絶縁膜と、前記層間絶縁膜の上に形成され前記第2コンタクトホールを介して前記中継電極に電気的に接続され前記共通電極と向かい合うスリットを有する画素電極と、を備えた第1基板を備えた液晶表示装置。

(もっと読む)

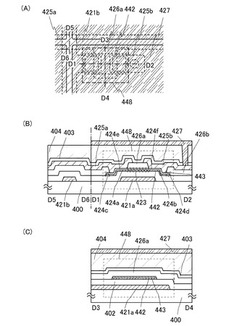

半導体装置

【課題】動作特性および信頼性の向上した、新規なマルチゲート構造のトランジスタを提

供することを課題とする。

【解決手段】2つ以上のゲート電極と、直列に接続した2つ以上のチャネル形成領域、ソ

ース領域、ドレイン領域、及び高濃度不純物領域を有する半導体層と、を有するマルチゲ

ート構造のトランジスタにおいて、ソース領域側に近接するチャネル形成領域のチャネル

長が、ドレイン領域側に近接するチャネル形成領域のチャネル長よりも大きくする。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】酸化物半導体膜を含むトランジスタにおいて、酸化物半導体膜に接し、且つ

ソース電極及びドレイン電極を覆う帯電防止機能を有する金属酸化膜を形成し、加熱処理

を行う。この加熱工程によって、水素、水分、水酸基又は水素化物などの不純物を酸化物

半導体膜より意図的に排除し、酸化物半導体膜を高純度化する。また、金属酸化膜を設け

ることで、トランジスタにおいて酸化物半導体膜のバックチャネル側に寄生チャネルが発

生するのを防止する。

(もっと読む)

表示装置および電子機器

【課題】封止性能を低減させることなく狭額縁化を実現することが可能な表示装置を提供する。

【解決手段】液晶表示装置1Aは、駆動側基板10および対向基板18間に設けられると共に、複数の画素を有する画素部10Aと、駆動側基板10上において、画素部10Aの周辺の額縁領域10Bに配設されたトランジスタTFT11と、額縁領域10Bにおいて、トランジスタTFT11を被覆して設けられた平坦化膜13(絶縁膜)と、画素部10Aを封止すると共に平坦化膜13の端縁部13eを覆って設けられたシール層19とを備えたものである。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

る。信頼性の高い半導体装置を歩留まり良く作製する。

【解決手段】酸化物半導体膜を有するトップゲート構造のスタガ型トランジスタにおいて

、酸化物半導体膜と接する第1のゲート絶縁膜を、プラズマCVD法によりフッ化珪素及

び酸素を含む成膜ガスを用いた酸化シリコン膜で形成し、該第1のゲート絶縁膜上に積層

する第2のゲート絶縁膜を、プラズマCVD法により水素化珪素及び酸素を含む成膜ガス

を用いた酸化シリコン膜で形成する。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

スイッチング素子基板

【課題】本発明は、低比誘電率かつ高OD値を達成することが可能な樹脂製遮光部を有し、画素部の面積が大きく、かつ、液晶表示装置に用いた場合に、コンタクトホール内における画素電極の断線を好適に防止することが可能なスイッチング素子基板およびこれを用いた液晶表示装置を提供することを主目的とする。

【解決手段】基材と、上記基材上に形成されたスイッチング素子と、上記基材上に設けられた画素部と、上記スイッチング素子上に形成され、上記スイッチング素子に用いられる電極上にコンタクトホールを有する樹脂製遮光部と、上記コンタクトホールの側面および端部を覆うように形成され、絶縁性を有する断線防止層とを有し、上記コンタクトホールの縦断面形状が、垂直形状または逆テーパー形状であり、上記断線防止層が、上記断線防止層の形成部分の縦断面形状が順テーパー形状となるように形成されていることを特徴とするスイッチング素子基板を提供することにより、上記目的を達成する。

(もっと読む)

表示装置

【課題】画素電極とソース配線、さらには画素電極とTFTとの電気的な干渉を抑制する

構造を提供する。

【解決手段】薄膜トランジスタと、前記薄膜トランジスタの活性層、ゲイト絶縁膜、及び

ゲイト電極上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜上に形成され、前

記活性層に接続されたソース配線及びドレイン電極と、前記ソース配線及び前記ドレイン

電極上に形成された第2の層間絶縁膜と、前記第2の層間絶縁膜上に形成された電磁シー

ルド用の導電膜と、前記導電膜上に形成された第3の層間絶縁膜と、前記第3の層間絶縁

膜上に形成され、前記ドレイン電極に接続された画素電極とを有し、前記導電膜は前記ソ

ース配線と前記画素電極との間に設けられている。

(もっと読む)

液晶表示装置

【課題】段差部にて、絶縁膜の両側に形成される電極同士が短絡する恐れのない液晶表示装置を提供する。

【解決手段】第1の基板は、アクティブ素子と、前記アクティブ素子よりも上層に形成された第1の絶縁膜と、前記第1の絶縁膜よりも上層に設けられた第1の電極と、前記第1の電極よりも上層に設けられた第2の絶縁膜と、前記第2の絶縁膜よりも上層に設けられた第2の電極とを有し、前記第1の絶縁膜は、第1のコンタクトホールを有し、前記第2の絶縁膜は、前記第1の電極と前記第2の電極との間と、前記第1のコンタクトホール内とに一体的に形成されており、前記第1のコンタクトホール内の前記第2の絶縁膜には、第2のコンタクトホールが形成されており、前記第2の絶縁膜は、第1の膜厚で形成した後、前記第2の電極を形成する前に前記第1の膜厚よりも薄い第2の膜厚まで薄膜化されて形成される。

(もっと読む)

表示装置

【課題】表示素子に印加される電圧が変化することによる表示品位の低下、表示の切替時

における紙媒体との違和感を低減することのできる液晶表示装置を提供することを課題の

一とする。

【解決手段】第1の画像信号の書き込み期間及び第1の画像信号の保持期間を有する第1

の静止画表示期間と、第2の画像信号の書き込み期間及び第2の画像信号の保持期間を有

する第2の静止画表示期間と、を切り替えて表示させ、第1の静止画表示期間の書き込み

期間と、第2の静止画表示期間の書き込み期間と、の長さを異ならせるディスプレイコン

トローラを有する構成とする。

(もっと読む)

電気光学装置および電子機器

【課題】画素の開口率を低下させることなく、画素電極のコンタクトホールが配置された電気光学装置およびこれを備えた電子機器を提供すること。

【解決手段】本適用例の液晶装置は、画素電極15と、画素電極15に対応して設けられた薄膜トランジスター(TFT)30と、TFT30と画素電極15との間に、TFT30の半導体層30aを覆うように設けられた遮光性の第1容量配線としての第2容量電極16bと、第2容量配線71と画素電極15との間に、画素電極15とコンタクトホールCNT8を介して電気的に接続された中継電極9と、を備え、第1容量配線としての第2容量電極16bは、画素電極15に対する画素の開口隅部に張り出した張り出し部16baを有し、コンタクトホールCNT8は、上記張り出し部16baと重なるように形成されている。

(もっと読む)

半導体装置

【課題】酸化物半導体層を用いる薄膜トランジスタにおいて、酸化物半導体層と電気的に

接続するソース電極層またはドレイン電極層との接触抵抗の低減を図ることを課題の一と

する。

【解決手段】ソース電極層またはドレイン電極層を2層以上の積層構造とし、その積層の

うち、酸化物半導体層と接する一層を酸化物半導体層の仕事関数より小さい仕事関数を有

する金属又はそのような金属の合金とする。二層目以降のソース電極層またはドレイン電

極層の材料は、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、または上述

した元素を成分とする合金か、上述した元素を組み合わせた合金等を用いる。

(もっと読む)

液晶パネル及びそれを用いた電子機器並びに投写型表示装置

【課題】半導体装置でパシベーション膜として一般的に使用されている減圧CVD法による窒化シリコン膜は、膜厚の10%程度のばらつきが生じるので、これを反射型液晶パネルに用いると、パシベーション膜の膜厚のばらつきによって反射率が大きく変化したり、液晶の屈折率が変動したりするという不具合がある。

【解決手段】基板(1)上に反射電極(14)がマトリックス状に形成されるとともに各反射電極に対応して各々トランジスタが形成され、前記トランジスタを介して前記反射電極に電圧が印加されるように構成された液晶パネル用基板において、パシベーション膜(17)として、膜厚が500〜2000オングストロームの酸化シリコン膜を使用し、入射光の波長に応じて膜厚を適当な値に設定するようにした。

(もっと読む)

141 - 160 / 2,664

[ Back to top ]