Fターム[2H092MA07]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 成膜方法 (5,204) | CVD (1,864)

Fターム[2H092MA07]の下位に属するFターム

Fターム[2H092MA07]に分類される特許

201 - 220 / 739

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に、酸化物半導体層より導電率の高いバッファ層を形成し、該バッファ層の上にソース電極層及びドレイン電極層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

薄膜トランジスタ搭載基板、その製造方法及び画像表示装置

【課題】活性層として用いた酸化物薄膜の安定化と高品質化を実現した薄膜トランジスタをプラスチック基板上に搭載した薄膜トランジスタ搭載基板の製造方法を提供する。

【解決手段】プラスチック基板10の上又はその上方に活性層となるアモルファス酸化物薄膜13を形成する工程と、少なくとも活性層となる部分のアモルファス酸化物薄膜13に向けてパルスレーザー20を照射する工程とを少なくとも有する。パルスレーザー20の照射工程は、プラスチック基板10に該プラスチック基板のガラス転移温度以上の温度を一定時間加えず、且つアモルファス酸化物薄膜13をアモルファス相のままで所定の比抵抗に制御する工程である。

(もっと読む)

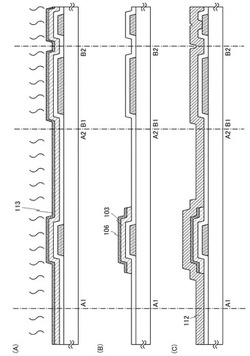

多層配線基板及びそれを備えた半導体装置

【課題】遮光領域を抑制することにより、開口率の低下を防止するとともに、製造工程を簡素化することができる多層配線基板及びそれを備えた半導体装置を提供することを目的とする。

【解決手段】TFT基板1は、第1コンタクトホール11が形成された第1絶縁膜8と、第1絶縁膜8の表面及び第1コンタクトホール11の表面に形成された第1配線層14と、第2コンタクトホール15が形成された第2絶縁膜9と、第2絶縁膜9上に積層されるとともに、第2絶縁膜9の表面及び第2コンタクトホール15の表面に形成され、第1配線層14と導通された第2配線層16とを備えている。そして、第1及び第2コンタクトホール11,15が、TFT基板1の上下方向Xにおいて重なった状態で直線的に配置され、第1コンタクトホール11において、第1配線層14上に絶縁性樹脂25が充填されている。

(もっと読む)

アクティブマトリックス基板の製造方法、電気光学装置、及び電子機器

【課題】低コストで高精細なアクティブマトリックス基板の製造方法、電気光学装置、および電子機器を提供する。

【解決手段】基板15と、複数の画素電極80と、前記複数の画素電極80と基板15との間に設けられた薄膜トランジスターと、前記薄膜トランジスターに電気的に接続されるデータ線40及びゲート線20と、を備えるアクティブマトリックス基板の製造方法であって、前記画素電極80をマスクとして、前記薄膜トランジスターの半導体層50のパターニングを行う。

(もっと読む)

半導体装置の製造方法および電子機器の製造方法

【課題】転写工程や薄膜加工工程においても効果的に検査が行える半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、素子(T)と前記素子と接続された外部接続端子(P)とを有する素子層(17)が形成された第1基板(S1)を、接着層(21)を介して第2基板(S2)と貼り合わせる工程を有し、前記工程において前記第1基板と前記第2基板との間に、前記外部接続端子と電気的に接続するようフレキシブルプリント回路(50)の少なくとも一部を挟み込むことを特徴とする。かかる方法によれば、上記フレキシブルプリント回路を利用して、素子の検査を容易に行うことができる。

(もっと読む)

液晶表示装置

【課題】液晶表示装置において、ディスクリネーションを低減する。

【解決手段】第1及び第2の走査線と第1及び第2の信号線とによって囲まれた領域に設けられた第1の画素電極と、第2及び第3の走査線と第1及び第2の信号線とによって囲まれた領域に設けられた第2の画素電極と、第1及び第2の画素電極の上方に設けられた対向電極を有し、第1の画素電極は、中央で最大の面積を占める平坦面と、第1乃至第4の端部を有し、第1の端部は第1の走査線に沿って設けられ、第2の端部は第1の信号線に沿って設けられ、第3の端部は第2の走査線に沿って設けられ、第4の端部は第2の信号線に沿って設けられ、第2及び第4の端部は前記平坦面と同じ高さに設けられ、第1及び第3の端部は平坦面より0.5μm以上高く設けられた液晶表示装置を提供する。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタアレイ基板及び表示装置

【課題】閾値電圧シフトが小さく、かつオン特性に優れた薄膜トランジスタ、及びその製造方法を提供する。

【解決手段】本発明に係る薄膜トランジスタの製造方法は、ゲート電極2、ゲート絶縁膜3、第1の半導体層10、オーミックコンタクト層として機能する第2の半導体層、ソース電極5及びドレイン電極6をこの順に形成する工程を備え、第1の半導体層10を形成する工程は、実質的にイントリンシックな微結晶シリコン層からなる微結晶層11を形成し、少なくともソース電極5、ドレイン電極6と対向配置される領域に、微結晶層11aの表面の結晶欠陥を低減するように、低濃度のP(リン)が添加された非晶質シリコン層からなる欠陥修復層12aを形成し、その後、実質的にイントリンシックな非晶質シリコン層からなる非晶質層13aを形成する。

(もっと読む)

薄膜トランジスタ及びその製造方法、電気光学装置、並びにセンサー

【課題】オン電流が高く、特性シフトが低減された薄膜トランジスタを提供する。

【解決手段】基板上に、活性層としてのIn、Ga、及びZnを含む酸化物半導体膜と、ゲート電極と、ゲート絶縁膜と、ソース電極と、ドレイン電極と、を有し、

前記酸化物半導体膜のモル比〔In:Ga:Zn〕を2.0−x:x:y(但し、0.0<x<2.0、0.0<y)で表したとき、前記酸化物半導体膜の膜厚方向についての前記yの分布において、前記基板に近い側の膜面、及び、前記基板から離れた側の膜面よりも、前記yが大きい領域が存在する。

(もっと読む)

半導体装置及びその製造方法、並びに液晶表示装置

【課題】光センサーと遮光膜を有する半導体装置において、段切れや膜剥がれに起因にする歩留まりの低下を防止することができるとともに、暗電流の増大を防止して光センサーの性能の低下を防止することができる半導体装置及びその製造方法、並びに液晶表示装置を提供することを目的とする。

【解決手段】フォトダイオード15を構成するポリシリコン膜を形成する部分Bの非晶質シリコン膜30の厚みW1が、遮光膜28の周縁に対応した部分Aの非晶質シリコン膜30の厚みW2より薄くなるように、非晶質シリコン膜30を薄膜化する。そして、非晶質シリコン膜30にレーザー光を走査して、非晶質シリコン膜30を多結晶化させてポリシリコン膜を形成する。

(もっと読む)

電子デバイス及びその製造方法、並びに電子機器

【課題】製造プロセスを増加させずに、信頼性が高く、かつ反射特性に優れる電子デバイスを提供する。

【解決手段】本発明に係る電子デバイス200は、基板1と、基板1上に形成され、少なくともMo系膜41と、その上層に形成されたAl系膜42とからなる導電性反射膜40とを備える。そして、導電性反射膜40のMo系膜41の表面荒さRaが5nm以下であり、Al系膜42の波長350nm〜550nmにおける反射率が85%以上である。

(もっと読む)

表示装置及びその製造方法

【課題】 移動度特性及び特性安定性を向上した薄膜トランジスタを提供する。さらに、それを用いた高性能の表示装置を提供する。

【解決手段】 基板上に、ゲート電極と、ゲート絶縁膜と、半導体膜と、ソース電極及びドレイン電極として機能する一対の電極とを具備し、少なくとも前記ソース電極及びドレイン電極の一部が前記半導体膜を挟んで前記ゲート絶縁膜の反対側に位置する薄膜トランジスタを有する表示装置であって、前記半導体膜は、1−8nmの厚さの微結晶Si膜と、前記微結晶Si膜の前記ゲート絶縁膜側とは反対側に位置する非晶質Si膜とを含む積層からなる。

(もっと読む)

電気光学装置

【課題】基板のクラックによる断線を回避して電気光学装置の信頼性や歩留りを向上させる。

【解決手段】本発明に係る電気光学装置は、基板(S1)と、基板上(S1)に配置され、画素領域(A1)と、画素領域(A1)の外周に位置する周辺領域(A2)とを有する絶縁層(12)と、上記画素領域に配置された電気光学素子と、周辺領域(A2)に配置され、上記電気光学素子を駆動する駆動回路(DC1,DC2)と、上記周辺領域に配置された外部端子(P)と、上記周辺領域に配置され、上記外部端子と上記駆動回路を電気的に接続する配線である引出配線(L1,L2)と、を有し、引出配線の少なくとも一部(L1)が基板(S1)と絶縁層(12)との間に配置される。

(もっと読む)

電界効果型トランジスタ及びその製造方法並びに画像表示装置

【課題】プラスチックフィルム基板と電界効果型トランジスタとの密着性を下地層を形成することで化学的に高め、フォトリソグラフィ工程で用いる強酸や強アルカリへの浸漬によっても電界効果型トランジスタがプラスチックフィルム基板から剥離することなく再現性良く製造する電界効果型トランジスタ及びその製造方法並びに画像表示装置を提供する。

【解決手段】基板、ゲート電極、ゲート絶縁層、ソース電極、ドレイン電極及び半導体を有して形成された電界効果型トランジスタであって、基板上に高分子化合物と金属化合物との混合物を含有する下地層を備えることを特徴とする電界効果型トランジスタ。

(もっと読む)

多階調フォトマスク、多階調フォトマスクの製造方法、及びパターン転写方法

【課題】 被転写体上に形成するレジストパターンの段差形状をより精緻に制御する。

【解決手段】 透明基板上に、遮光部、透光部、第1半透光部及び第2半透光部を含む転写パターンが形成された多階調フォトマスクであって、露光光に対する第1半透光部の透過率が、露光光に対する第2半透光部の透過率よりも小さく、第1半透光部を透過する露光光と、第2半透光部を透過する露光光との干渉によって形成される光強度が、第1半透光部を透過する露光光の強度以上となるように、第1半透光部を透過する露光光と、第2半透光部を透過する露光光との位相差が制御されている。

(もっと読む)

電界効果型トランジスタの製造方法、電界効果型トランジスタ、及び表示装置の製造方法

【課題】電界効果型トランジスタの製造工程の簡略化が図れる電界効果型トランジスタの製造方法、電界効果型トランジスタ、及び表示装置の製造方法を提供する。

【解決手段】本実施の形態のトップコンタクト型の電界効果型トランジスタ10の製造方法によれば、半導体層形成工程で形成した活性層18上に、防護層22を形成した後に、該防護層22上にフォトレジスト膜を形成して露光工程においてパターン状に露光する。そして、次の現像工程において、アルカリ性現像液を用いて、上記露光工程を経たフォトレジスト膜30を現像してレジストパターン30B’を形成すると共に、防護層22における該レジストパターン30B’から露出している領域22Aを除去して防護層22のエッチングを行なう。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層にダメージを与えず、また、オフ電流の小さい薄膜トランジスタを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の手前側にソース電極又はドレイン電極が形成されてなるボトムゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、裏面照射によって紫外線の照射された半導体層部分を高導電率化するものであるため、半導体層へのダメージが生じないため信頼性が向上する。また、ソース電極又はドレイン電極によって紫外線が遮光された半導体層の領域は照射前の導電率と同じとなるため、オフ電流の値を小さくすることができる。

(もっと読む)

液晶表示装置

【課題】光透過型及び光反射型兼用の液晶表示装置において、光反射型液晶表示装置として使用する場合の輝度を低下させることなく、光透過型液晶表示装置として使用する場合のコントラスト及び輝度を向上させる。

【解決手段】本発明の液晶表示装置は、第1の透明基板21と、第1の透明基板21の上方において第1の透明基板21と対向する第2の基板41と、第1の透明基板21と第2の基板41との間に挟持される液晶層50と、からなる。第1の透明基板21は光反射領域Bと光透過領域Aとからなり、光反射領域Bは、絶縁膜24上に、モリブデン、クロム、チタン及びタンタルの何れか1つからなる下地膜と該下地膜の上に形成されたアルミニウム膜又は銀膜とからなる反射電極25とを有し、光透過領域Aは、絶縁膜24上に透過電極26を有し、透過電極26の端面の上部に反射電極25が重なって接続されている。

(もっと読む)

半透過性膜、表示デバイス、及びパターン基板の製造方法

【課題】生産性が向上し、かつ特性が良好な半透過性膜、表示デバイス、及びパターン基板の製造方法を提供することを目的とする。

【解決手段】本発明にかかる半透過性膜は、光学特性として光の透過特性と反射特性とを有する半透過性膜である。半透過性膜は、アルミニウム又はアルミニウムを主成分とする合金のいずれかに少なくとも40mol%以上50mol%未満の窒素を含む窒素含有膜である。また、半透過性膜は、上記の窒素含有膜と金属膜との積層膜とすることも可能である。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層の高導電率化工程やソース電極及びドレイン電極のエッチング工程において、半導体層にダメージを与えないような薄膜トランジスタ及びこれを用いた液晶表示装置を提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の向こう側にソース電極又はドレイン電極が形成されてなるトップゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、紫外線の表面照射によって照射された半導体層部分を高導電率化するため、半導体層へのダメージが生じない。従って、高導電率化工程及びエッチング工程のいずれにおいても半導体層はダメージを受けることがないため信頼性が向上する。

(もっと読む)

半導体装置の作製方法

【課題】大面積な半導体装置を低コストに提供することを目的の一とする。または、nチャネル型トランジスタ及びpチャネル型トランジスタに最適な結晶面をチャネル形成領域とすることにより、性能向上を図ることを目的の一とする。

【解決手段】絶縁表面上に(211)面から±10°以内の面を上面とする島状の単結晶半導体層を形成し、単結晶半導体層の上面及び側面に接して形成し、且つ絶縁表面上に非単結晶半導体層を形成し、非単結晶半導体層にレーザー光を照射して非単結晶半導体層を溶融し、且つ、単結晶半導体層を種結晶として絶縁表面上に形成された非単結晶半導体層を結晶化して結晶性半導体層を形成し、結晶性半導体層を用いて、nチャネル型トランジスタ及びpチャネル型トランジスタを形成する。

(もっと読む)

201 - 220 / 739

[ Back to top ]