Fターム[2H092MA19]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | パターン形成 (6,228) | エッチング (2,565) | 物理的エッチング (431)

Fターム[2H092MA19]に分類される特許

41 - 60 / 431

電界効果型トランジスタ、表示素子、画像表示装置、及びシステム

【課題】低コストで、後工程にて形成される上層の塗布性に優れ、かつ高信頼性を示す電界効果型トランジスタなどの提供。

【解決手段】絶縁性基板と、前記絶縁性基板上に形成されたゲート電極と、前記ゲート電極上に形成されたゲート絶縁層と、前記ゲート絶縁層上に形成されたソース電極及びドレイン電極と、前記ゲート絶縁層上に形成され、かつ、少なくとも前記ソース電極及び前記ドレイン電極との間に形成された酸化物半導体層と、前記酸化物半導体層を被覆するように形成された保護層とを有し、前記保護層が、フッ素樹脂を含有し、前記保護層形成後の前記保護層の水に対する接触角が、75°以上90°以下である電界効果型トランジスタである。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

表示装置及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を

同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電

極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気

的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成

された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを

介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成

された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的

に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜を生産性高く作製する方法を提供する。また、該微結晶半導体膜を用いて、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】反応室内に第1の電極及び第2の電極が備えられたプラズマCVD装置を用いて、堆積性気体及び水素を第1の電極及び第2の電極の間に配置された基板を含む反応室内に供給した後、第1の電極に高周波電力を供給することにより反応室内にプラズマを発生させて、基板に微結晶半導体膜を形成する。なお、プラズマが発生している領域において、基板端部と重畳する領域のプラズマ密度を、基板端部と重畳する領域より内側の領域のプラズマ密度より高くし、基板端部より内側の領域に微結晶半導体膜を形成する。また、上記微結晶半導体膜の作製方法を用いて、半導体装置を作製する。

(もっと読む)

微結晶半導体膜及びその作製方法、並びに半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜及びその作製方法を提供する。また、電気特性が良好な半導体装置を、生産性高く作製する方法を提供する。

【解決手段】厚さが70nm以上100nm以下の微結晶半導体膜であり、微結晶半導体膜の表面から一部が突出する結晶粒を有し、当該結晶粒は配向面を有し、且つ13nm以上の大きさの結晶子を有する微結晶半導体膜である。また、微結晶半導体膜の膜密度が2.25g/cm3以上2.35g/cm3以下、好ましくは2.30g/cm3以上2.33g/cm3以下である。

(もっと読む)

液晶表示装置、パーソナルコンピュータ、ディスプレイ、電子書籍

【課題】液晶滴下により、広視野角表示のマルチドメイン垂直配向型の液晶表示装置を実

現する。

【解決手段】第1の基板及び第2の基板間に滴下された液晶を保持するためのシール材と

、シール材に囲まれ、第1の基板上に設けられた画素部と、シール材の外側において、第

2の基板とは重ならない領域の第1の基板上に配置されるICチップと、シール材の外側

において、第2の基板とは重ならない領域の第1の基板上に配置される、画素部とICチ

ップとを電気的に接続する異方性導電膜と、シール材と交差するように画素部から異方性

導電膜が配置される領域まで延び、第1の基板上に設けられた画素部とICチップとを電

気的に接続する配線とを有する液晶表示装置である。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流が小さく、好ましくはオン電流及び移動度も高く、工程が簡略化された半導体装置の作製方法を提供する。

【解決手段】チャネルエッチ型の薄膜トランジスタの作製に際して、ゲート絶縁層上に少なくとも半導体層を形成し、半導体層上に導電膜を形成し、導電膜上にエッチングマスクを形成し、基板を反応室内に搬入し、導電膜を加工してソース電極及びドレイン電極層を形成し、反応室内に半導体エッチング用のガスを導入し、反応室内で半導体エッチング用のガスでエッチングを行い、基板を反応室から搬出し、その後エッチングマスクを除去する。すなわち、導電膜の加工から半導体エッチング用のガスで行うエッチングまでを同一チャンバー内で連続して行い、半導体エッチング用のガスで行うエッチングはエッチングマスクを除去する前に行う。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

半導体装置の作製方法

【課題】接触不良を低減し、コンタクト抵抗の増大を抑制し、開口率が高い液晶表示装置

を得ることを課題とする。

【解決手段】基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、島状半導

体膜と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けら

れ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領

域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極

に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護

膜を有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有

し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記補助容量は保護膜

に覆われていない液晶表示装置に関する。

(もっと読む)

タッチセンシング基板及びそれの製造方法

【課題】タッチセンシング基板及びその製造方法を提供する。

【解決手段】第1光センシング素子は、ベース基板上に配置され、第1の光によって動作し、第1ゲート電極、第1ゲート電極と重なる第1アクティブパターン、第1アクティブパターンと部分的に重なる第1ソース電極、及び第1ドレーン電極を含む。第2光センシング素子は、ベース基板上に配置され、第2の光により動作し、第2ゲート電極、第2ゲート電極と重なる第1アクティブパターンと異なった物質を含む第2アクティブパターン、第2アクティブパターンと部分的に重なる第2ソース電極、及び第2ドレーン電極を含む。第1バイアス配線は、第1及び第2ゲート電極から延長されて第1及び第2ゲート電極と接続される。ソース及びドレーン電極がソース及びドレーン接続電極によりコンタクトホールを通じて接続されることによって、ソース及びドレーン電極のショート不良を防止することができる。

(もっと読む)

電気光学装置の製造方法および電気光学装置

【課題】トランジスターの静電破壊を抑制する。

【解決手段】電気光学装置の製造方法は、基板上に第1トランジスターを形成する工程と

、第1トランジスターが形成された基板上に第1絶縁膜を形成する工程と、第1絶縁膜を

エッチングして、第1トランジスターに通じる第1貫通孔を形成する工程と、第1貫通孔

を介して第1トランジスターに接続された第1部分および第1部分とは接続されていない

第2部分を有する第1導体膜を第1絶縁膜上に形成する工程と、第1導体膜上に第2絶縁

膜を形成する工程と、第2絶縁膜をエッチングして第1導体膜の第1部分および第2部分

のそれぞれに通じる第2貫通孔および第3貫通孔を形成する工程と、第2貫通孔および第

3貫通孔を介して、第1導体膜の第1部分および第2部分を電気的に接続する第2導体膜

を第2絶縁膜上に形成する工程とを有する。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い表示装置を提供する。消費電力が少なく、信頼性の高い表示装置を提供する。

【解決手段】トランジスタの、ゲート電極となる導電層、ゲート絶縁層となる絶縁層、半導体層、およびチャネル保護層となる絶縁層を連続して形成する。ゲート電極(同一層で形成される他の電極または配線を含む)と島状半導体層の形成を、一回のフォトリソグラフィ工程で行う。該フォトリソグラフィ工程と、コンタクトホールを形成するフォトリソグラフィ工程と、ソース電極及びドレイン電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程と、画素電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程の、4つのフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

半導体装置

【課題】アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的としている。

【解決手段】基板上に逆スタガ型のTFT上に無機材料から成る第1の層間絶縁層と、第1の層間絶縁膜上に形成された有機材料から成る第2の層間絶縁層と、前記第2の層間絶縁層に接して形成された画素電極とを設け、前記基板の端部に他の基板の配線と電気的に接続する入力端子部とを有し、該入力端子部は、ゲート電極と同じ材料から成る第1の層と、画素電極と同じ材料から成る第2の層とから形成されていることを特徴としている。このような構成とすることで、フォトリソグラフィー技術で使用するフォトマスクの数を5枚とすることができる。

(もっと読む)

液晶表示装置

【課題】表示領域に平坦化膜が形成された配向が均一で良好な構造で、蓄積容量を小面積で大きく確保し、高開口率化できるアクティブマトリクス型液晶表示装置の提供。

【解決手段】ソース電極106上の一部に、平坦化膜108が存在しない凹部領域114がある。凹部領域114において、透明導電膜からなる共通電極110が、ソース電極106を覆って第2蓄積容量142を形成している。

(もっと読む)

横電界方式のアクティブマトリクス型液晶表示装置

【課題】縦クロストークの発生を防止することができ、かつ、開口率を向上させることができる横電界方式の液晶表示装置を提供する。

【解決手段】 共通電極と画素電極とを同層上に形成し、共通電極及び画素電極の双方を透明材料から形成する。共通電極はデータ線を完全に覆うように形成する。データ線と共通電極との間にある絶縁膜は、複数の層からなり、一方の層は、共通電極の下方においてのみ、形成されている。

(もっと読む)

可変容量素子、及び液晶表示装置

【課題】制御性が良く、安定して動作する可変容量素子を提供する。消費電力が少なく、表示品位の良い液晶表示装置を提供する。

【解決手段】印加される電界により、n型またはi型となる半導体、もしくは、p型またはi型となる半導体を用いて可変容量素子を構成する。容量素子を構成する第1の電極と第2の電極の間に、誘電体層として絶縁層と上記半導体層の積層を設ける。第1の電極を誘電体層側に設け、第2の電極を半導体層側に設けた時に、第1の電極と半導体層が重畳する面積C1よりも、第1の電極と半導体層と第2の電極が重畳する面積C2の方を小さくなるようにする。動画像表示と静止画像表示で駆動方法を切り替える液晶表示装置に可変容量素子を適用することで、消費電力が少なく、表示品位の良い液晶表示装置を実現できる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

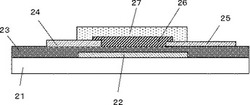

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

アレイ基板及び液晶ディスプレイ

【課題】本発明はアレイ基板及び液晶ディスプレイに関する。

【解決手段】本発明は、アレイ基板と液晶ディスプレイを開示している。このアレイ基板は、サブストレートと、前記サブストレートに形成された、横縦方向に交差して複数の画素ユニットを囲んで形成したデータライン及びゲートラインと、を備え、各画素ユニットは画素電極と薄膜トランジスタースイッチ素子とを備え、前記薄膜トランジスタースイッチ素子は、ゲート電極、ソース電極、ドレイン電極、活性層を備え、前記ゲート電極と活性層との間にゲート絶縁層が設けられ、前記ゲート絶縁層は不透明絶縁層を含む。

(もっと読む)

41 - 60 / 431

[ Back to top ]