Fターム[2H092MA27]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 処理方法 (2,214) | ドーピング (666)

Fターム[2H092MA27]に分類される特許

41 - 60 / 666

酸化物半導体膜、半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を活性層に用いるトランジスタにおいて、チャネル領域と隣接するソース領域およびドレイン領域に微小な空洞を設ける。酸化物半導体膜に形成されるソース領域およびドレイン領域に微小な空洞を設けることによって、微小な空洞に酸化物半導体膜のチャネル領域に含まれる水素を捕獲させることができる。

(もっと読む)

電気光学装置及び電子機器

【課題】ダミー画素部に黒色のベタ状の画像を表示させた場合、ダミー画素電極には最大(又は最小)の電圧が印加され続けられる。一方、画素電極には、平均すれば中間調の電圧が印加される。この電位差によって発生する横方向電界により液晶層中に含まれるイオン性不純物が移動して偏在し、シミ状の表示むらが発生するという課題があった。

【解決手段】基板上に設けられ、画素電極が配列した表示画素部と、前記表示画素部を平面視で囲うように配列したダミー画素電極と、を備え、前記ダミー画素電極は、電気的にフローティング状態を取り、前記ダミー画素電極と前記画素電極との間隙は、前記画素電極間の間隔よりも小さい。そのため、ダミー画素電極の電位は、隣り合う画素電極の電位に近づく。そのため、横方向電界を緩和でき、シミ状の表示むらの発生を防ぐことができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

液晶表示装置、及び液晶表示装置の製造方法

【課題】 光リーク電流を低減し、画質を向上させる。

【解決手段】 本開示に係る液晶表示装置は、複数の層間絶縁膜310が積層されており、複数の層間絶縁膜310のうち、信号線22及びトランジスタが設けられた非開口領域25と、信号線22及びトランジスタが設けられていない開口領域23とを有する駆動素子基板12と、液晶16を介して駆動素子基板12と対向するように設けられた対向基板11と、を備え、駆動素子基板12は、非開口領域25と開口領域との間であって層間絶縁膜310に設けられ、層間絶縁膜310と屈折率が異なる絶縁部311と、絶縁部311と、対向基板11との間に設けられた遮光膜305と、を有する。

(もっと読む)

電気光学装置の製造方法、電気光学装置、投射型表示装置および電子機器

【課題】絶縁膜の穴内に設けたプラグ電極によって導電層同士の導通を行うにあたって、研磨時間やプラグ電極形成用導電膜の成膜時間を短縮することのできる電気光学装置の製造方法、電気光学装置、投射型表示装置、および電子機器を提供すること。

【解決手段】液晶装置の素子基板において、第2電極層7aと画素電極9aとを層間絶縁膜48の穴48a内に設けたプラグ電極8aを介して電気的に接続するにあたって、第1絶縁膜46に設けたコンタクトホール46aを埋めるようにプラグ電極8aを形成した後、第2絶縁膜47を成膜する。そして、第2絶縁膜47を表面側から研磨してプラグ電極8aを露出させた後、第2絶縁膜47の表面側に画素電極9aを形成する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、信頼性の高い半導体装置を提供する。

【解決手段】酸化物半導体膜を含むトランジスタの作製工程において、酸化物半導体膜に酸素ドープ処理を行い、その後、酸化物半導体膜及び酸化物半導体膜上に設けられた酸化アルミニウム膜に対して熱処理を行うことで、化学量論的組成比を超える酸素を含む領域を有する酸化物半導体膜を形成する。該酸化物半導体膜を用いたトランジスタは、バイアス−熱ストレス試験(BT試験)前後においてもトランジスタのしきい値電圧の変化量が低減されており、信頼性の高いトランジスタとすることができる。

(もっと読む)

電気光学装置の製造方法

【課題】テトラエトキシシラン等のシラン系有機材料を用いたプラズマCVD法によりシリケートガラスを形成した場合でも、シリケートガラスから半導体層へのフッ素の侵入を防止することのできる電気光学装置の製造方法を提供すること。

【解決手段】液晶装置の製造方法において、ゲート電極3cの形成工程、低濃度不純物導入工程、および高濃度不純物導入工程を行った後、シランガス等のシラン系無機原料を用いたCVD法により第1絶縁膜411を形成する。次に、第1アニール工程において第1絶縁膜411をアニールした後、テトラエトキシシラン等のシラン系有機原料を用いたプラズマCVD法によりシリケートガラスからなる第2絶縁膜412を形成する。

(もっと読む)

半導体装置の製造方法、及び電気光学装置の製造方法

【課題】情報処理と光制御とを一括して光制御基板1枚で処理する場合、例えば低リークを必要とするTFTと、高速動作するTFT等、特性の異なるTFTを同一基板上に形成することが必要となってくる。しかしながら、フォトマスク数を増やすことで特性の異なるTFTを形成すると、TATが延び、価格も高騰するという課題があった。

【解決手段】第1LDDと、第2LDDの2水準の濃度を持つLDDを一つのハーフトーンマスクでレジストを形成した。レジスト膜厚は、第1LDDには低加速エネルギーでは不純物が透過せず、高加速エネルギーでは不純物が通る設定とし、第2LDDではレジストを開口させた。低加速エネルギーでイオン注入することで、第2LDDにはこのイオン注入で1回めのイオン注入が行われる。次に、高加速エネルギーでイオン注入することで第1LDDには高加速エネルギー分の不純物が入り、第2LDDには2回分の不純物が入る。

(もっと読む)

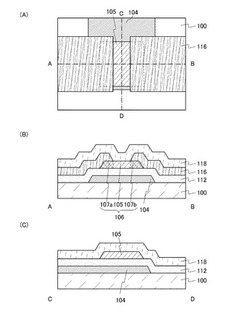

半導体装置の製造方法および電気光学装置の製造方法

【課題】特性の異なるTFTを同一基板上に形成する場合、フォトマスク数を増やすことで特性の異なるTFTを形成すると、TATが延び、価格も高騰するという課題があった。

【解決手段】1つのハーフトーンマスクを用いて、第2領域156とチャネル前駆体161aとソース・ドレイン前駆体165aとで膜厚の異なる段差レジストを形成する。NMOSTFTのチャネル前駆体161aには低加速エネルギーでは不純物が透過せず、高加速エネルギーでは不純物が通るレジスト膜厚の設定とし、ソース・ドレイン前駆体165aではレジストを開口させた。まず低加速エネルギーでソース・ドレイン前駆体165aにイオン注入し、次に、高加速エネルギーでチャネル前駆体161aにイオン注入する。第2領域156では2回の注入で、不純物が透過しないレジスト膜厚に設定する。

(もっと読む)

半導体装置

【課題】隣接する画素の間に設ける絶縁膜は、バンク、隔壁、障壁、土手などとも呼ばれ

、薄膜トランジスタのソース配線や、薄膜トランジスタのドレイン配線や、電源供給線の

上方に設けられる。特に、異なる層に設けられたこれらの配線の交差部は、他の箇所に比

べて大きな段差が形成される。隣接する画素の間に設ける絶縁膜を塗布法で形成した場合

においても、この段差の影響を受けて、部分的に薄くなる箇所が形成され、その箇所の耐

圧が低下されるという問題がある。

【解決手段】段差が大きい凸部近傍、特に配線交差部周辺にダミー部材を配置し、その上

に形成される絶縁膜の凹凸形状を緩和する。また、上方配線の端部と下方配線の端部とが

一致しないように、上方配線と下方配線の位置をずらして配置する。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

表示装置及びマスク

【課題】マスクの枚数を増やすことなく、ストレージキャパシタの電極間から半導体パターンを除去して高画質化を実現させる表示装置及びその製造方法を提供する。

【解決手段】本発明によるTFTパネルの製造では、半導体パターンとTFTのドレイン電極とを、同じマスクを利用したエッチングで同時にパターニングする。一方、画素電極の直下に形成される絶縁膜のパターニングには別のマスクを利用する。ドレイン電極を覆う絶縁膜の領域では、中央部の全体を感光させ、周辺部を半分の厚みまで感光させる。ストレージ電極の上方を覆う絶縁膜の領域は薄い一部を残して感光させる。ドレイン電極を覆う誘電膜をエッチングしてドレイン電極を露出させるとき、絶縁膜のその薄い一部がその下地の誘電膜を保護する。その後、絶縁膜のその薄い一部を画素電極の一部に置換し、保護された誘電膜を隔ててストレージ電極と対向させる。

(もっと読む)

液晶表示装置、電子機器

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

薄膜トランジスタの製造方法、薄膜トランジスタ、表示装置、センサ及びX線デジタル撮影装置

【課題】基板の選択性を広げつつ、電界効果移動度が高くノーマリーオフ駆動する薄膜トランジスタ等を得る。

【解決手段】活性層の成膜工程での成膜室中の雰囲気の全圧に対する酸素分圧をPo2depo(%)とし、熱処理工程中の雰囲気の全圧に対する酸素分圧をPo2anneal(%)としたときに、熱処理工程時の酸素分圧Po2anneal(%)が、−20/3Po2depo+40/3≦Po2anneal≦−800/43Po2depo+5900/43の関係を満たすように成膜工程と熱処理工程とを行う。

(もっと読む)

表示装置及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を

同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電

極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気

的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成

された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを

介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成

された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的

に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

半導体膜の作製方法及び半導体装置の作製方法

【課題】結晶性の高い微結晶半導体膜を生産性高く作製する方法を提供する。また、該微結晶半導体膜を用いて、電気特性が良好な半導体装置を生産性高く作製する方法を提供する。

【解決手段】反応室内に第1の電極及び第2の電極が備えられたプラズマCVD装置を用いて、堆積性気体及び水素を第1の電極及び第2の電極の間に配置された基板を含む反応室内に供給した後、第1の電極に高周波電力を供給することにより反応室内にプラズマを発生させて、基板に微結晶半導体膜を形成する。なお、プラズマが発生している領域において、基板端部と重畳する領域のプラズマ密度を、基板端部と重畳する領域より内側の領域のプラズマ密度より高くし、基板端部より内側の領域に微結晶半導体膜を形成する。また、上記微結晶半導体膜の作製方法を用いて、半導体装置を作製する。

(もっと読む)

液晶表示装置

【課題】ソースフォロワ出力の線形領域を従来より拡大する。

【解決手段】画素10内のソースフォロワ用PMOSトランジスタTr13及びTr14は、ゲートが保持容量Cs1、Cs2に接続されて常にオン状態で使用されるため、ソースフォロワ用PMOSトランジスタTr13及びTr14の閾値電圧Vthのみが+0.5Vに設定され、ノーマリーオン状態とされる。ソースフォロワ用PMOSトランジスタTr13及びTr14の電流値は定電流負荷トランジスタTr7で制御し、オンオフは定電流負荷トランジスタTr7とスイッチング用NMOSトランジスタTr5、Tr6で制御する。また、トランジスタTr5、Tr6が介在し出力可能の電圧範囲が存在するため、ソースフォロワ用PMOSトランジスタTr13及びTr14の閾値電圧Vthのシフトによって線形性を保つ領域が最大になるように最適化する。

(もっと読む)

半導体装置

【課題】同一の層間膜上に画素電極と、ゲート配線を形成した半導体装置において、マス

ク枚数を追加することなく、液晶の焼きつきや特性劣化を低減する。

【解決手段】ゲート配線上に絶縁膜を設けることで、ゲート配線が非選択の期間に液晶に

かかるゲート電圧の絶対値を減少させることができる。絶縁膜は遮光性樹脂膜、柱状スペ

ーサーで形成すると、マスク枚数の増加を抑えることができる。また、絶縁膜上に画素電

極を形成し、ゲート配線と画素電極が重なり合うようにすることで、画素電極の電界遮蔽

効果によって、液晶にかかるゲート電圧を減少させることができる。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

41 - 60 / 666

[ Back to top ]