Fターム[2H092MA27]の内容

液晶−電極、アクティブマトリックス (131,435) | 製造方法 (16,988) | 製法、工程 (14,676) | 処理方法 (2,214) | ドーピング (666)

Fターム[2H092MA27]に分類される特許

61 - 80 / 666

液晶表示装置及び電子機器

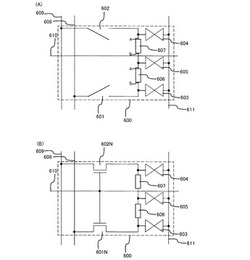

【課題】液晶素子に印加される電圧を異ならせて視野角特性を改善する。

【解決手段】 本発明の一は、一画素に三以上の液晶素子を有し、該液晶素子の各々に印

加される電圧値が異なる液晶表示装置である。各液晶素子に印加される電圧を異ならせる

には、加えた電圧を分圧する素子を配置することにより行う。印加される電圧を異ならせ

るためには、容量素子、抵抗素子、又はトランジスタ等を用いる。

(もっと読む)

EL表示装置

【課題】動作性能および信頼性の高いEL表示装置を提供する。

【解決手段】第1のチャネル形成領域と、第1のソース領域及び第1のドレイン領域と、ゲート絶縁膜と、第1のゲート電極とを備えた第1のTFTと、第2のチャネル形成領域と、第2のソース領域及び第2のドレイン領域と、ゲート絶縁膜と、第2のゲート電極とを備えた第2のTFTと、第1のTFT及び第2のTFT上に設けられた第1の絶縁膜と、第1のソース領域及び第1のドレイン領域の一方と接続されたソース配線と、第1のソース領域及び第1のドレイン領域の他方と接続し、且つ第2のゲート電極に接続された第1のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の一方に接続された第2のドレイン配線と、第1の絶縁膜上に設けられ、第2のソース領域及び第2のドレイン領域の他方に接続された電流供給線と、を有する。

(もっと読む)

液晶表示装置

【課題】IPSにおける従来の技術は、工程数が多く、開口率が低いので、実用化できな

い。また、液晶層に最も近接している層に存在する配線及び電極が多く、画素表示部にお

ける個々の液晶にかかる電界が不均一であった。

【解決手段】本発明は、ゲイト線102、105とコモン線103、104を最初に同時

に形成し、層間膜形成後、画素電極108とコモン電極110、111とソ─ス線106

、107を同時に形成する。こうすることによって、電極パタ─ンを単純化でき、工程を

簡略化した。また、液晶層に最も近接している層に存在する配線及び電極を画素電極とコ

モン電極とソ─ス線とし、その形状を単純なものにした。

(もっと読む)

反射型液晶表示装置及び液晶プロジェクターシステム

【課題】 遮光だけでは抑制できない、入射してしまう光により生じる電子(ホール)による影響を抑制する。

【解決手段】 トランジスタのドレイン領域34よりも、多数キャリアに対して、ドレイン領域における電圧とQ(単位電荷量)との積の基準値よりも低いポテンシャルとされる領域36を設けるか、もしくはドレイン領域の周りにポテンシャル障壁を設ける。かかる構成により、フローティングとなる反射電極30と接続されたドレイン領域34の回りのポテンシャル制御を行い、半導体基板内に発生した光キャリアがドレイン領域34に導かれにくくする。

(もっと読む)

表示装置

【課題】配線抵抗の上昇を防ぎつつ、配線間の寄生容量を低減できる表示装置を提供する。また、表示品質を向上させた表示装置を提供する。また、消費電力を低減できる表示装置を提供する。

【解決手段】液晶表示装置の画素において、信号線と、該信号線と交差する走査線と、信号線から突出する第1の電極と、該第1の電極と対向する第2の電極と、該第2の電極と接続する画素電極とを有する。また、走査線の一部はループ形状であり、第1の電極の一部は、走査線の開口部と重畳する領域に位置する。即ち、第1の電極の一部は、走査線と重畳しない。

(もっと読む)

電気光学装置の製造方法および電気光学装置

【課題】トランジスターの静電破壊を抑制する。

【解決手段】電気光学装置の製造方法は、基板上に第1トランジスターを形成する工程と

、第1トランジスターが形成された基板上に第1絶縁膜を形成する工程と、第1絶縁膜を

エッチングして、第1トランジスターに通じる第1貫通孔を形成する工程と、第1貫通孔

を介して第1トランジスターに接続された第1部分および第1部分とは接続されていない

第2部分を有する第1導体膜を第1絶縁膜上に形成する工程と、第1導体膜上に第2絶縁

膜を形成する工程と、第2絶縁膜をエッチングして第1導体膜の第1部分および第2部分

のそれぞれに通じる第2貫通孔および第3貫通孔を形成する工程と、第2貫通孔および第

3貫通孔を介して、第1導体膜の第1部分および第2部分を電気的に接続する第2導体膜

を第2絶縁膜上に形成する工程とを有する。

(もっと読む)

表示装置

【課題】本発明は、アクティブマトリクス型表示装置の製造コストを低減するこ

とを課題とし、安価な表示装置を提供することを課題とする。また、本発明の表

示装置を表示部に用いた安価な電子装置を提供することを目的とする。

【解決手段】 アクティブマトリクス型表示装置の製造コストを低減するために

画素部に用いるTFTを全て一導電型TFT(ここではpチャネル型TFTもし

くはnチャネル型TFTのいずれか一方を指す)とし、さらに駆動回路もすべて

画素部と同じ導電型のTFTで形成することを特徴とする。これにより製造工程

を大幅に削減し製造コストを低減することが可能となる。

(もっと読む)

表示素子の製造方法

【課題】安定した電流駆動能力を発揮させる。

【解決手段】アレイ基板20の製造方法は、基板上にゲート電極24aを形成するゲート電極形成工程と、ゲート電極24a上に不純物を含有するゲート絶縁膜24b、半導体膜SM、導電膜COの順で成膜する成膜工程と、導電膜CO上にレジストRSを塗布し、そのレジストRSに対してフォトマスクを介して露光を行った後に現像を行うことでレジストRSをパターニングするレジストパターニング工程と、パターニングされたレジストRSをマスクとして導電膜COをエッチングすることで開口領域OPを挟んで配されるソース電極24d及びドレイン電極24eを形成する導電膜パターニング工程と、開口領域OPから半導体膜SMを介してゲート絶縁膜24bに含有される不純物を脱離させる不純物脱離工程とを含む。

(もっと読む)

半導体装置の作製方法

【課題】樹脂基板等の可撓性を有する基板を用いて、柔軟性を有する半導体装置を作製す

るための技術を提供する。

【解決手段】分離層を有する固定基板上に樹脂基板を形成する工程と、前記樹脂基板上に

少なくともTFT素子を形成する工程と、前記分離層にレーザー光を照射することにより

、前記分離層の層内または界面において前記固定基板から前記樹脂基板を剥離する工程と

を行い、前記樹脂基板を用いた柔軟性を有する表示装置を作製する。

(もっと読む)

半導体装置およびその作製方法

【課題】短チャネル効果による電気特性の変動が生じにくい、チャネル領域に酸化物半導体を含むトランジスタを用いた半導体装置を作製する。

【解決手段】窒素を含む一対の酸窒化物半導体領域、および該一対の酸窒化物半導体領域に挟まれる酸化物半導体領域を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体領域上に設けられるゲート電極とを有する半導体装置。ここで、一対の酸窒化物半導体領域はトランジスタのソース領域およびドレイン領域となり、酸化物半導体領域はトランジスタのチャネル領域となる。

(もっと読む)

液晶表示装置

【課題】文字をくっきり表示でき、画像を滑らかに表示できる液晶表示装置を提供するこ

とを目的する。

【解決手段】面積階調方式を用いており、どの表示領域を用いて1画素を構成するかにつ

いて、モードによって切り替える。文字を表示したい場合には、ストライプ配置になるよ

うに選んで、1画素を構成する。これにより、くっきりとした表示が出来る。画像を表示

したい場合は、入りくんだ状態になるように選んで、1画素を構成する。これにより、滑

らかな表示をすることが出来る。

(もっと読む)

可変容量素子、及び液晶表示装置

【課題】制御性が良く、安定して動作する可変容量素子を提供する。消費電力が少なく、表示品位の良い液晶表示装置を提供する。

【解決手段】印加される電界により、n型またはi型となる半導体、もしくは、p型またはi型となる半導体を用いて可変容量素子を構成する。容量素子を構成する第1の電極と第2の電極の間に、誘電体層として絶縁層と上記半導体層の積層を設ける。第1の電極を誘電体層側に設け、第2の電極を半導体層側に設けた時に、第1の電極と半導体層が重畳する面積C1よりも、第1の電極と半導体層と第2の電極が重畳する面積C2の方を小さくなるようにする。動画像表示と静止画像表示で駆動方法を切り替える液晶表示装置に可変容量素子を適用することで、消費電力が少なく、表示品位の良い液晶表示装置を実現できる。

(もっと読む)

電気光学装置および投射型表示装置

【課題】熱応力に起因するヒロック等の欠陥が画素電極の表面に発生することを防止することができる電気光学装置、および該電気光学装置を用いた投射型表示装置提供する。

【解決手段】電気光学装置100の素子基板10において、ノンドープシリコン酸化膜からなる第3層間絶縁膜44と、アルミニウム膜等からなる画素電極9aとの間にはドープトシリコン酸化膜からなる応力緩和膜46が形成されている。応力緩和膜46は、ドープトシリコン酸化膜からなり、第3層間絶縁膜44と異なる熱膨張係数をもって第3層間絶縁膜44に接するとともに、画素電極9aと異なる熱膨張係数をもって画素電極9aに接している。また、各層の熱膨張係数は以下の関係第3層間絶縁膜44<応力緩和膜46<画素電極9aにある。このため、応力緩和膜46は、第3層間絶縁膜44と画素電極9aとの間において熱膨張係数の差を緩和する。

(もっと読む)

半導体装置及びその作製方法

【課題】従来では、LDD構造を備えたTFTやGOLD構造を備えたTFTを形成しようとすると、その製造工程が複雑なものとなり工程数が増加してしまう問題があった。

【解決手段】第2のドーピング工程によって低濃度不純物領域24、25を形成した後、第4のエッチング工程を行うことによって、第3の電極18cに重なる低濃度不純物領域の幅と、第3の電極に重ならない低濃度不純物領域の幅とを自由に調節できる。こうして、第3の電極18cと重なっている領域は、電界集中の緩和が達成されてホットキャリアによる防止ができるとともに、第3の電極18cと重なっていない領域は、オフ電流値を抑えることができる。

(もっと読む)

電気光学装置、投射型表示装置、電気光学装置の製造方法

【課題】画素電極表面でのヒロックの発生や、平坦化絶縁膜において凹部を埋める部分での空洞の発生を防止することのできる電気光学装置、該電気光学装置を用いた投射型表示装置、および当該電気光学装置の製造方法を提供すること。

【課題手段】電気光学装置100の素子基板10において、反射性の画素電極9aの上層側に設けられた平坦化絶縁膜17は、画素電極9a上に積層された層がドープトシリコン酸化膜170からなる。ドープトシリコン酸化膜170の熱膨張係数は、画素電極9aを構成するアルミニウム膜の熱膨張係数との差が小さい。このため、加熱した状態で平坦化絶縁膜17を成膜しても、画素電極9aおよび平坦化絶縁膜17に大きな熱応力が発生しないので、画素電極9aの表面にヒロック等の欠陥が発生しにくい。また、ドープトシリコン酸化膜170は、段差被覆性に優れている。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

発光装置

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にp型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

EL表示装置及びその作製方法

【課題】さらなる低温プロセス(350℃以下、好ましくは300℃以下)を実現し、安価な半導体装置を提供する。

【解決手段】本発明は、結晶構造を有する半導体層103を形成した後、イオンドーピング法を用いて結晶質を有する半導体層103の一部にn型不純物元素及び水素元素を同時に添加して不純物領域107(非晶質構造を有する領域)を形成した後、100〜300℃の加熱処理を行うことにより、低抵抗、且つ非晶質な不純物領域108を形成し、非晶質な領域のままでTFTのソース領域またはドレイン領域とする。

(もっと読む)

薄膜トランジスタ基板およびそれの製造方法

【課題】薄膜トランジスタ基板およびこれの製造方法を開示する。

【解決手段】本発明の薄膜トランジスタ基板は、基板上に形成されたゲート電極、前記ゲート電極上に前記ゲート電極と重なるように形成され、多結晶シリコンを含むアクティブ層、前記アクティブ層上に前記ゲート電極を中心に両側に分離して形成された第1オーミックコンタクト層、前記第1オーミックコンタクト層上に形成された第2オーミックコンタクト層および前記第2オーミックコンタクト層上に形成されたソース電極およびドレーン電極を含む。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置に於けるLDD構造とGOLD構造の形成は、従来、ゲート電極をマスクにセルフアラインで形成しているが、ゲート電極が2層構造となる場合が多く、成膜工程とエッチング工程が複雑になる。またドライエッチング等のプロセスのみでLDD構造及びGOLD構造の形成を行っている為、トランジスタ構造が全て同一構造となり、回路毎にLDD構造とGOLD構造及びシングルドレイン構造を別々に形成することが困難である。

【解決手段】 回折格子パターン或いは半透膜から成る光強度低減機能を有する補助パターンを設置したフォトマスク或いはレチクルをゲート電極形成用フォトリソグラフィ工程に適用することにより、ドライエッチング及びイオン注入工程を通し、回路毎にGOLD構造及びLDD構造及びシングルドレイン構造のトランジスタを簡単に形成することができることを特徴としている。

(もっと読む)

61 - 80 / 666

[ Back to top ]