Fターム[4K030DA02]の内容

Fターム[4K030DA02]の下位に属するFターム

Fターム[4K030DA02]に分類される特許

81 - 100 / 746

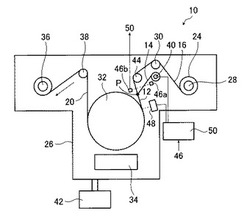

機能性フィルムの製造方法および製造装置

【課題】積層体の長手方向に、基材と保護フィルムとの密着力が変化した場合であっても、基材と保護フィルムとを適正に剥離させることができ、基材の搬送テンションが緩んで、ツレシワが発生したり、熱ダメージを受けて、基材が損傷することを防止する。

【解決手段】処理を行なう前の積層体の搬送中に、基材上の保護フィルムの有無を検出する第1検出工程と、第1検出工程と成膜処理との間に、基材上の保護フィルムの有無を検出する第2検出工程と、第1検出工程と第2検出工程の検出結果に応じて、第1検出工程と第2検出工程との間で、保護フィルムが基材から剥離するように、剥離力を制御する制御工程とを有することにより、前記課題を解決する。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備え、シード層3を形成する工程における下地の加熱温度を、アモルファスシリコン膜を形成する工程における前記下地の加熱温度よりも低くする。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

成膜方法及び半導体装置の製造方法

【課題】ポリイミド膜に対して高い密着性を有するコバルト膜を成膜する方法を提供する。

【解決手段】成膜装置100の処理容器1内で、処理容器1内にCOガスを導入しながら、ポリイミド膜81が形成されたウエハWを110℃以上400℃以下の温度で加熱し、ポリイミド膜81を熱処理する。熱処理によって、ポリイミド膜81中の分子が熱分解し、膜密度が減少するとともに、表面粗度が大きくなる。その後、処理容器1内に成膜原料であるCo2(CO)8を導入してCVD法によりポリイミド膜81上にコバルト膜83を堆積させる。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】面取り部の形状を再成形するとともに、裏面クラウンを完全に除去し、平坦性に優れた、パーティクルのほとんど無いエピタキシャルウェーハを製造することができる方法を提供することを目的とする。

【解決手段】表裏の主面と該主面の外周の面取り部とからなるシリコン単結晶基板上にエピタキシャル層を成長させることによりエピタキシャルウェーハを製造する方法において、前記シリコン単結晶基板の前記裏面側の主面全面と前記裏面側の面取り部に裏面酸化膜を形成する工程と、該裏面酸化膜を形成したシリコン単結晶基板の表面側の主面上に、40μm以上の膜厚のエピタキシャル層を成長させる工程と、該エピタキシャル層表面に保護酸化膜を形成する工程と、該保護酸化膜を形成したシリコン単結晶基板の面取り部を研削及び研磨する工程と、その後、前記保護酸化膜を除去して、仕上げの洗浄を行う工程とを含むエピタキシャルウェーハの製造方法。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてCo2(CO)8を用いてCo膜を成膜する場合に、Co膜の針状の異常成長を抑制することができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、基板Wの温度を160〜300℃とし、処理容器1内に気体状のCo2(CO)8を供給し、基板W上でCo2(CO)8を熱分解させて基板W上にCo膜を成膜する。

(もっと読む)

トレンチ埋め込みエピタキシャル成長条件の最適化方法

【課題】トレンチ埋め込みエピタキシャル成長の制御パラメータを変更した際にエピタキシャルの成長反応の変化傾向を簡便に知ることができ、結果として、最適な成長条件を簡便に見つけ出すことが可能な、トレンチ埋め込みエピタキシャル成長条件の最適化方法を提供する。

【解決手段】シリコンソースガスにエッチングガスを混合した混合ガスを原料ガスとし、この原料ガスをH2キャリアガスで流通させることにより、シリコン基板表面に形成したトレンチ内部にエピタキシャル層を成長させてトレンチ内部をエピタキシャル層で埋め込む工程を含む半導体基板の製造方法における、トレンチ内部をエピタキシャル層で埋め込む際のエピタキシャル成長の最適条件を求める方法であって、ある特定のアスペクト比のトレンチ内部を埋め込む際のエピタキシャル成長の最適条件をエピタキシャル成長速度のH2キャリアガスの流量依存性により求めることを特徴とする。

(もっと読む)

基板処理装置及び半導体装置の製造方法

【課題】生産性よく、半導体装置の不良の少ない高品質な膜を形成でき、歩留りの低下を防止できる基板処理装置及び半導体製造装置の製造方法を提供する。

【解決手段】基板を処理する複数の処理室と、前記各処理室内へ原料を供給する原料供給系と、前記各処理室内へ反応剤を供給する反応剤供給系と、前記原料供給系に設けられ前記複数の処理室で共用とされる原料供給部と、前記反応剤供給系に設けられ前記複数の処理室で共用とされる反応剤供給部と、基板を収容した前記各処理室内に前記原料と前記反応剤とを交互に供給して前記基板を処理すると共に、前記原料供給部と前記反応剤供給部とを前記各処理室で時間分割して用いるように、前記原料供給系、前記反応剤供給系、前記原料供給部および前記反応剤供給部を制御する制御部と、を有する。

(もっと読む)

エピタキシャルウェーハの製造方法

【課題】シリコンウェーハとエピタキシャル層との界面における不純物濃度の低下を防止する。

【解決手段】シリコンウェーハを反応炉内で水素ベークする第1の工程(ステップS3)と、反応炉にシリコン原料ガス及びドーパントガスを導入することにより、水素ベークされたシリコンウェーハの表面にエピタキシャル層を形成する第2の工程(ステップS4)とを備える。第1の工程においては、反応炉内にドーパントガスを導入し、外方拡散により低下するシリコンウェーハ表層の不純物濃度を補う。これにより、シリコンウェーハとエピタキシャル層との界面における不純物濃度の低下が抑制されたエピタキシャルウェーハを製造することが可能となる。

(もっと読む)

積層体の形成方法

【課題】炭素膜のもつ基材への高い密着性、硬度、および表面平坦性を利用し、ダイヤモンド砥粒やアルカリスラリーなどを用いることなく、ダイヤモンド、サファイヤ、硬質炭素膜などの硬度の高い材料表面を高速かつ簡便に、高い平坦性および精度で研磨、研削が可能な積層体を形成する方法を提供する。

【解決手段】基材を用意する工程と、ダイヤモンド微粒子を粉砕して前記基材上に該ダイヤモンド微粒子を設ける工程と、内部にSiO2材又はAl2O3材の供給源及び前記工程で得られた基材を設置したマイクロ波プラズマCVD反応炉内に、反応ガスを導入し、該反応炉内に表面波プラズマを発生させて、該基材上にSiO2材又はAl2O3材と炭素粒子とからなる膜を、該SiO2材又はAl2O3の量が前記基材側の下部層から上部層に向かって減少するように堆積させる工程とを備える。

(もっと読む)

メタモルフィック基板システム、メタモルフィック基板システムの形成方法、および、第3族窒化物の半導体素子

【課題】サファイア、GaAs、シリコンまたは炭化ケイ素といった異種基板上で第3族窒化物の半導体材料の層を1層以上成長させる上で遭遇する、少なくともいくつかの問題に対処する。

【解決手段】ラミネート基板システムは、AlxGa1-xN(5)と支持基板材料(4)(または当該材料と一般化学組成が同一である材料)とが交互に積層された多数の層からなる変成遷移領域(2)を含む。転位密度が低い第3族窒化物半導体素子(2)がラミネート基板システム上に形成される。変成遷移領域(2)の多数の層(4、5)は、格子定数が支持基板(1)(支持基板付近)の格子定数から素子(3)(素子付近)の格子定数へと成長方向に沿って変化する超格子構造を形成する。

(もっと読む)

半導体基板及びその製造方法

【課題】単純な単結晶シリコン基板を出発基板として窒化ガリウム膜を形成することができ、反りやクラックが抑制された半導体基板及びその製造方法を提供する。

【解決手段】半導体基板10は、単結晶シリコン基板11と、前記単結晶シリコン基板11の最表面を除く表層領域に形成された転位層12と、前記単結晶シリコン基板11の前記最表面に形成されたバッファ層13と、前記バッファ層13の表面に形成された窒化ガリウム層14とを備えている。転位層12は、窒化ガリウム層14が形成された単結晶シリコン基板14の表層領域に転位が発生し且つ単結晶シリコン基板11の最表面には転位が発生しない条件下でイオン注入することにより形成される。イオン注入では、ドーズ量が5E+14atoms/cm2以上5E+17atoms/cm2以下のアルゴンイオンを注入する。

(もっと読む)

半導体基板及びその製造方法

【課題】単純な単結晶シリコン基板を出発基板としてGaN膜を形成することができ、反りやクラックが抑制された半導体基板及びその製造方法を提供する。

【解決手段】半導体基板10は、単結晶シリコン基板11と、単結晶シリコン基板11の表面に形成された転位層を含む加工ダメージ層12と、加工ダメージ層12の表面に形成されたバッファ層13と、バッファ層13の表面に形成された窒化ガリウム膜14とを備えている。加工ダメージ層12は、単結晶シリコン基板11の表面から深さ0.5μmまでの範囲内に形成されている。加工ダメージ層12は、#2000〜#8000の砥石を用いて単結晶シリコン基板11の表面を研削した後、転位層の一部が残るように単結晶シリコン基板11の表面を研磨することにより形成される。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備え、アミノシラン系ガスのアミノシランは熱分解させないで、下地上に吸着させる。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】エピタキシャル膜成長を行う際に、基板表面へのエッチングダメージを軽減して、良質なエピタキシャル膜を得る技術を提供する。

【解決手段】表面に絶縁体面と半導体面とを有する基板を処理室内に搬送する工程と、前記処理室内に搬送された基板に対し、水素含有ガスと塩素含有ガスとを供給し、前記基板の前記半導体面をエッチングするエッチング工程と、前記エッチングされた基板に対し、水素含有ガスを供給して基板表面の残留塩素を除去する第1パージ工程と、前記残留塩素を除去された基板に対しシリコン含有ガスを供給し、前記基板の半導体面にシリコン含有膜を形成する成膜工程とを備え、前記エッチング工程と第1パージ工程とを含む工程を連続して2回以上実施するよう半導体装置の製造方法を構成する。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理に使用するガスを供給する処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、処理室101に、被処理体1を複数収容するとともに、コントローラ150が、下地を加熱し、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、下地を加熱し、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御する。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

エピタキシャルウェーハの製造方法、エピタキシャルウェーハ

【課題】エピタキシャル層の形成時のオートドープを確実に抑制することで、エピタキシャルウェーハの抵抗率均一性を向上させ、周縁部まで効率的にデバイスの形成が可能なエピタキシャルウェーハの製造方法およびエピタキシャルウェーハを提供する。

【解決手段】一面10a側に第一のエピタキシャル層11を形成したシリコン単結晶基板10は、次に、堆積物除去工程を行う。この堆積物除去工程では、シリコン単結晶基板10の面取り部10cを、例えば鏡面研磨することによって、第一の成長工程S1で生じた堆積物Pを除去する。

(もっと読む)

誘電体膜の形成方法、及びこれを用いる半導体素子のキャパシタの形成方法

【課題】誘電特性及び漏れ電流特性を向上させることのできる半導体素子の誘電体膜の形成方法及びキャパシタの形成方法を提供する。

【解決手段】誘電体膜は、原子層堆積法により、ウェーハ上に酸化ジルコニウム(ZrO2)及び酸化アルミニウム(Al2O3)で構成された誘電体膜を形成する方法であって、チャンバー内に、1つのZrと1つのAl原子とが1つの分子を構成しているソースガスを注入し、ウェーハ上に、ZrO2とAl2O3とからなる[ZrO2]x[Al2O3]y(ここで、x及びyは正数である)膜を形成するステップを繰り返すことにより、ZrO2とAl2O3とで構成された厚さ30Å〜500Åの誘電体膜を形成する。

(もっと読む)

窒化膜の形成方法

【課題】バッチ式の縦型炉を用いてプラズマアシストALD法により窒化膜を形成する際、炉底部付近でのローディング効果を抑制する。

【解決手段】反応容器102内に複数段にウエハを載置可能なボート101と、前記反応容器の側面に沿ってRF電極106で挟まれたプラズマ空間105と、該プラズマ空間から前記反応容器内の前記各段のウエハに略均等にガスを供給可能な供給口F1,F2と、を備えたバッチ式の縦型炉100を用いて、窒化すべきガスの導入、吸着、パージ、プラズマ励起された窒化ガスの導入による前記窒化すべき吸着ガスの窒化およびパージ、を1サイクルとして所定の膜厚までサイクルを繰り返すプラズマアシストALD法において、前記窒化すべきガス導入時のキャリアガス量よりも前記窒化ガス導入時のキャリアガス流量を少なくし、特に窒化ガスとしてのNH3とキャリアガスとしてのN2の流量比をNH3の50に対してN2を3以下とする。

(もっと読む)

81 - 100 / 746

[ Back to top ]