Fターム[4K030DA09]の内容

Fターム[4K030DA09]に分類される特許

101 - 120 / 328

微小機械システムに適用される高い摩擦性能を維持しながら微小機械部品をコーティングする方法

【課題】表面粗さの低減と摩擦性能の向上させながら微小機械システムの微小機械部品をコーティングする方法を提供する。

【解決手段】 本発明の微小機械システムの微小機械部品をコーティングする方法は、(A)コーティングすべき基板(4)を用意するステップと、(B)前記基板(4)を、ダイアモンドコーティング層(1)を施すステップとを有する。前記ダイアモンドコーティング層(1)は、反応容器内でCVDステップにより堆積され、前記CVDステップによるダイアモンドコーティング層の(1)の堆積プロセスの間の成長プロセスの終了段階に於いて、前記反応容器内の炭素量を変化させ、前記基板(4)の表面近傍のsp2/sp3炭素(2)結合の変化を生じさせる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】動作電圧が低い半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置の抵抗可変素子を作製する際に、タングステンからなる導電膜31上にチタンシリコン窒化物からなる非晶質膜32を堆積させ、その上にチタン窒化物からなる多結晶導電膜33を堆積させることにより、下部電極25を形成する。次に、ニッケル酸化物からなる抵抗可変膜26を堆積させ、その後加熱処理を行い、多結晶導電膜33の結晶を成長させると共に、多結晶導電膜33に含まれるチタンと抵抗可変膜26に含まれる酸素とを反応させる。これにより、多結晶導電膜33の結晶粒が不均一に成長して突起34が形成されると共に、酸化膜35が形成されることにより、抵抗可変膜26の下層部分26aに酸素欠損が生成される。

(もっと読む)

透明ガスバリア性フィルム

【課題】加工時や使用時に生じる熱による寸法変化が起こりにくく、且つ変質しにくく、したがって、長期にわたり高く安定したガスバリア性を保持することができる透明ガスバリア性フィルムを提供する。

【解決手段】プラスチックフィルムを加熱処理し、特定の熱収縮率となるように収縮させてプラスチック基材フィルムとし、該プラスチック基材フィルムの少なくとも一方の面に蒸着膜を設けて蒸着フィルムとし、該蒸着フィルムを加熱処理して、特定の熱収縮率となるように収縮させ、該収縮させた蒸着フィルムの蒸着膜が設けられた面に、さらに、ガスバリア性塗布膜、蒸着膜、ガスバリア性塗布膜、をこの順序で設けることを特徴とする透明ガスバリア性フィルム。

(もっと読む)

酸化ストロンチウムルテニウム界面

酸化ストロンチウムルテニウムは、ルテニウム伝導体と酸化ストロンチウムチタン誘電体との間に有効な界面を提供する。酸化ストロンチウムルテニウムの形成は、酸化ストロンチウムを形成するための原子層堆積の使用と、その後の酸化ストロンチウムルテニウムを形成するための酸化ストロンチウムの焼鈍とを含む。酸化ストロンチウムの第1の原子層堆積は水を酸素源として使用して行われ、続いて、その後の酸化ストロンチウムの原子層堆積がオゾンを酸素源として使用して行われる。 (もっと読む)

グラフェン製造法

【課題】新規のグラフェン製造方法を提供する。

【解決手段】本発明はグラフェンの製造方法に関し、以下の段階を含む。

・基板上にアモルファス炭素を含む薄層を堆積する段階、

・光及び/又は電子照射の下で前記薄層をアニーリングし、それによってグラフェンを含む層が得られる段階。

(もっと読む)

High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体

【課題】High−k金属ゲート・トランジスタに対するスレショルド電圧制御および駆動電流改良のための方法および構造体を提供する。

【解決手段】デバイスを形成する方法は、基板を用意するステップと、基板上に界面層を形成するステップと、界面層上にHigh−k誘電体層を堆積するステップと、High−k誘電体層上に酸素除去層を堆積するステップと、アニールを実施するステップとを含む。High−k金属ゲート・トランジスタは、基板と、基板上の界面層と、界面層上のHigh−k誘電体層と、High−k誘電体層上の酸素除去層とを含む。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】半導体装置の製造において、金属膜の酸化による高抵抗化を防止し、生産性を向上させる。

【解決手段】半導体装置の製造方法は、基板200を収容し、基板200の温度が第1処理温度となるように設定された処理室201内に、酸素を用いることなく熱分解にて金属含有膜を形成できる有機金属原料ガスを供給して、基板200上に金属含有膜を形成する工程と、金属含有膜が形成された基板200を収容し、基板200の温度が第2処理温度となるように設定された処理室201内で、水素含有ガス雰囲気下、もしくは、到達真空雰囲気下で金属含有膜を熱処理する工程と、を有する。

(もっと読む)

縦型ウエハ処理装置

【課題】縦型ウエハ処理装置において、反応管のフランジの厚みが薬液洗浄により減少した場合であっても、追加で緩衝材を挿入することなく、反応管とマニホールドの気密性を確保する。

【解決手段】反応管1のフランジ1aの上面を金属管7側に付勢するために金属管7に着脱可能に取り付けられた金属製のフランジ押え部29を備えている。フランジ押え部29は、金属管7の上方に配置される金属管側フランジ押え部材31と、突起部33aでフランジ1aの上面を付勢するするフランジ側フランジ押え部材33と、金属管側フランジ押え部材31及びフランジ側フランジ押え部材33の互いに対向する面に取り付けられた金属製バネ35とを備えている。フランジ押え部29の高さは可変になっている。フランジ押え部29は、フランジ側フランジ押え部材33が取付けネジの締め付けによって金属管7に固定されることによって金属管7に取り付けられる。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】より高い誘電率を有する高誘電率絶縁膜を形成する半導体装置の製造方法及び基板処理装置を提供する。

【解決手段】基板上に高誘電率絶縁膜を形成する工程S106と、前記高誘電率絶縁膜に対し真空下で熱処理を施す工程S110と、熱処理後の前記高誘電率絶縁膜が室温となるまでの間、前記高誘電率絶縁膜が存在する空間の酸素分圧を、前記熱処理時に前記高誘電率絶縁膜が存在する空間の酸素分圧と同等もしくはそれ以下に保持する。

(もっと読む)

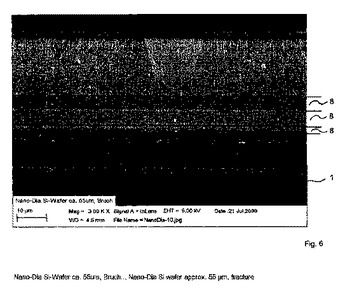

CVD自立ダイヤモンド膜及びその製造方法

本発明は、互いに重ねて積層された複数のダイヤモンド層(8)を含むCVD自立ダイヤモンド膜であって、各ダイヤモンド層(8)の下面は、第1の平均結晶粒径が2〜50nmであるダイヤモンドから形成され、ダイヤモンド層(8)内の平均結晶粒径はダイヤモンド層(8)の下面から上面へと増大し、上面の領域の第2の平均結晶粒径が50〜500nmであるCVD自立ダイヤモンド膜に関する。  (もっと読む)

(もっと読む)

圧電素子

【課題】本発明の目的は、セラミックスの結晶化温度を低減させることができ、セラミックスの表面モフォロジを改善することができる、セラミックスの製造方法を提供することにある。

【解決手段】セラミックスの製造方法は、酸素八面体構造を有する複合酸化物材料と、該複合酸化物材料に対して触媒作用を有する常誘電体材料とが混在した膜を形成し、その後該膜を熱処理することを含み、前記常誘電体材料は、構成元素中にSiを含む層状触媒物質、または構成元素中にSi及びGeを含む層状触媒物質からなる。前記熱処理は焼成及びポストアニールを含み、少なくとも該ポストアニールは、加圧された、酸素及びオゾンの少なくとも一方を含む雰囲気中で行われることが望ましい。セラミックスは、酸素八面体構造を有する複合酸化物であって、該酸素八面体構造中にSi及びGeを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板側から熱酸化膜、CVD酸化膜の2層を積層したゲート絶縁膜を有する半導体装置において、アニール処理時にCVD酸化膜の内部応力が圧縮応力に変化することによる半導体基板等の歪みを低減する。

【解決手段】熱酸化膜とCVD酸化膜との間に、リンガラス膜を形成する。リンガラスは、シリコン酸化膜中にリン(P)を導入して軟化温度(ガラス転移温度)を低くした酸化膜であり、850〜900℃でリフローと呼ばれる流動現象が生じる。900℃以上で行われるCVD酸化膜のアニール処理時には、リンガラス膜がリフロー流動状態となり、熱酸化膜とCVD酸化膜と間で緩衝材として機能する。これによってアニール処理時にCVD酸化膜の内部応力が圧縮応力に変化することが抑制され、ゲート絶縁膜や半導体基板の歪みが低減される。

(もっと読む)

スパッタリング装置

【課題】生産性の低下を抑えつつ組成の異なる合金薄膜を形成可能なスパッタリング装置を提供する。

【解決手段】スパッタリング装置10は、外部より低圧な雰囲気に維持可能なチャンバ12と、チャンバ12内で基材14を保持する保持部16と、保持部16で保持された基材14に周面が対向するように設けられた回転可能な回転陰極18であって、表面のターゲット材料をスパッタリングするための電力が供給される筒状の回転陰極18と、回転陰極18の表面に金属材料を供給可能な複数の補助陰極320,330と、を備える。複数の補助陰極320,330は、互いに異なる金属材料を回転陰極18の表面に供給する。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】界面層および高誘電率絶縁膜下層部への窒素原子の導入を抑制することができる半導体装置の製造方法及び基板処理装置の提供。

【解決手段】MOSFETのゲートスタック形成工程は、ウエハ上に界面層を形成するステップと、界面層に第一ハフニウムシリケート膜を形成するステップと、第一ハフニウムシリケート膜にアニールを施すことで第一ハフニウムシリケート膜を緻密化もしくは結晶化するステップと、緻密化もしくは結晶化した第一ハフニウムシリケート膜上に第二ハフニウムシリケート膜を形成するステップと、第一ハフニウムシリケート膜および第二ハフニウムシリケート膜に対しプラズマ窒化を施すステップと、プラズマ窒化のプラズマダメージを回復する回復アニールステップと、を有する。窒素導入による移動度の劣化を抑制し、良好なMOSFET特性を得ることができる。

(もっと読む)

エピタキシャルウェーハとその製造方法

【課題】歪み層形成に供されるウェーハで転位発生に対して耐性が高いエピタキシャルウェーハを提供する。

【解決手段】シリコン単結晶から切り出されたシリコン基板表面にシリコンエピタキシャル層が成膜堆積されたエピタキシャルウェーハであって、

前記シリコンエピタキシャル層表面の酸素濃度が1.0×1017〜12×1017atoms/cm3 とされてなる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ウィンドウ特性の向上とリテンション特性の向上とを同時に図ることのできる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】シリコン基板110上に、トンネル酸化膜111、チャージトラップ膜112、ブロッキング酸化膜113、ゲート電極114が、下側からこの順で形成された積層構造を有する半導体装置であって、ブロッキング酸化膜113が、チャージトラップ膜112側に設けられた結晶質膜113aと、当該結晶質膜113aの上層に設けられたアモルファス膜113bとを具備している。

(もっと読む)

ミクロポーラス炭素系材料、ミクロポーラス炭素系材料の製造方法、吸着材及びミクロポーラス炭素系材料を用いた水素吸蔵方法

【課題】ガス吸着量が多いミクロポーラス炭素系材料を提供する。

【解決手段】ミクロポーラス炭素系材料であって、炭素骨格中に窒素を有し、3次元の長周期規則構造と、内部にミクロ細孔とを有し、BET表面積が1500m2/g以上であり、窒素/炭素の元素比が0.07以上である。このミクロポーラス炭素系材料は、多孔質材料1の表面及び空孔(ミクロ孔)の内部に窒素含有有機化合物を導入し、この窒素含有有機化合物を加熱して炭化する第1の工程と、多孔質材料1の表面及び空孔の内部に有機化合物を導入して気相炭化する第2の工程と、多孔質材料1を除去する第3の工程と、を有する製造方法により得られる。

(もっと読む)

ミクロポーラス炭素系材料、ミクロポーラス炭素系材料の製造方法及びミクロポーラス系炭素材料を用いた水素吸蔵方法

【課題】元来有する細孔機能を維持しながら担持された金属が有する機能を発現可能なミクロポーラス炭素系材料を提供する。

【解決手段】ミクロポーラス炭素系材料5であって、0.7nm以上2nm以下の範囲内の3次元の長周期規則構造と、ミクロ細孔2aとを有するミクロポーラス炭素系材料であって、ミクロ細孔2a表面に遷移金属4が担持されている。この材料を、遷移金属を含む多孔質材料の表面及びミクロ細孔内に有機化合物を導入し、この有機化合物を化学気相成長法により炭化して遷移金属を含むミクロポーラス炭素系材料と多孔質材料の複合体を得る工程と、多孔質材料を除去する工程とを有する方法、又は多孔質材料の表面に有機化合物を導入して化学気相成長法によりミクロポーラス炭素系材料を得て、このミクロポーラス炭素系材料を遷移金属塩溶液中に浸漬・含浸し、ミクロポーラス炭素系材料の表面に遷移金属を担持する方法により得る。

(もっと読む)

多孔質の低誘電率組成物並びにそれを作製及び使用するための方法

【課題】多孔質の有機ケイ酸塩ガラス膜を提供する。

【解決手段】当該膜、SivOwCxHyFz(式中、v+w+x+y+z=100%、vは10〜35原子%、wは10〜65原子%、xは5〜30原子%、yは10〜50原子%、zは0〜15原子%である)は、Si−CH3を有するケイ酸塩の網目構造を有し、細孔及び2.7よりも低い誘電率を有する。予備的な膜が、オルガノシラン及び/又はオルガノシロキサン前駆体と細孔形成前駆体とからCVD法によって堆積される。ポロゲン前駆体が予備的な膜中に細孔を形成し、続いて除去されて多孔質膜を与える。組成物は、少なくとも1つのSi−H結合を含有するオルガノシラン及び/又はオルガノシロキサン化合物と、アルコール、エーテル、カルボニル、カルボン酸、エステル、ニトロ、第一、第二及び/又は第三アミン官能性又はそれらの組み合わせを含有する炭化水素のポロゲン前駆体とを含む。

(もっと読む)

耐食性基体の製造方法

【課題】所望の腐食性の高い薬品に対して耐食性を示す基体を製造する方法を提供する。

【解決手段】少なくとも表面層がチタン、チタン合金、チタン合金酸化物又は酸化チタンからなる基体の表面に炭化水素を主成分とするガスの燃焼炎を直接当てて該基体の表面温度を550〜1100℃の範囲内で所定温度に制御して加熱処理するか、又は該基体の表面をその表面温度を550〜1100℃の範囲内で所定温度に制御した状態で炭化水素を主成分とするガスの燃焼ガス雰囲気中で加熱処理して炭素ドープ酸化チタン層を形成することにより、表面の耐食性を制御して所望の薬品環境に対して耐食性を有する基体を製造する。

(もっと読む)

101 - 120 / 328

[ Back to top ]