Fターム[4K030DA09]の内容

Fターム[4K030DA09]に分類される特許

41 - 60 / 328

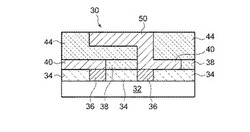

多相超低誘電膜の形成方法

【課題】誘電率が2.7以下であり、弾性計数および硬度の改善等、機械的特性を向上させた超低誘電率(k)膜、および膜の製造方法を提供する。

【解決手段】多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.4以下であり、ナノサイズの孔または空隙を有し、弾性係数が約5以上であり、硬度が約0.7以上である。好適な多相超低k誘電膜44は、Si、C、O、およびHの原子を含み、誘電率が約2.2以下であり、ナノサイズの孔または空隙を有し、弾性係数が約3以上であり、硬度が約0.3以上である。

(もっと読む)

シリコン発光素子に用いる活性層およびその活性層の製造方法

【課題】 基板の面内方向のキャリア拡散と基板垂直方向のキャリア注入を高効率に行うことのできる、シリコン発光素子用の活性層および該活性層の製造方法の提供を目的とする。

【解決手段】 シリコン発光素子に用いる活性層であり、シリコン化合物からなる第1の層と、該第1の層よりもバンドギャップが大きいシリコン化合物からなる第2の層とが基板上に交互に積層された多層膜構造を有する。また、複数のシリコンナノ粒子が多層膜構造の中に設けられている。第1の層に含まれるシリコン原子の量は、第2の層に含まれるシリコン原子の量よりも多く、複数のシリコンナノ粒子のうちの少なくとも一つは、前記第1の層と前記第2の層との境界面のうち少なくとも一つの面を越えて存在する。

(もっと読む)

低誘電材料及びその薄膜の製造方法

【課題】単一種のフルオロカーボンを含む二酸化前駆体のみを使用して、大量のフルオロカーボンを含有する二酸化ケイ素の低誘電材料薄膜を沈積でき、低誘電材料の耐熱性と耐水性を向上できる、低誘電材料及びその薄膜の製造方法を提供すること。

【解決手段】まず基板をプラズマ生成反応システムに入れ、その後フルオロカーボンを含む二酸化ケイ素前駆体を運ぶキャリアガスをプラズマ生成反応システム中に導入し、フルオロカーボンを含む二酸化ケイ素前駆体を基板上に形成させ、さらに加熱方式でフルオロカーボンを含む二酸化ケイ素前駆体を低誘電材料薄膜に転化させ、同時に低誘電材料薄膜の応力を除去し、より緊密な構造とする工程によって、各種異なる雰囲気下でも、フルオロカーボンを含む二酸化ケイ素前駆体が大量のフルオロカーボンを含有する二酸化ケイ素の低誘電材料薄膜を形成することができる。

(もっと読む)

窒化アルミニウムを被覆した耐蝕性部材およびその製造方法

【課題】 窒化アルミニウム(AlN)被覆膜(層)を耐熱性部材の表面に被覆した際に、反り変形のない寸法精度に優れた耐蝕性部材を提供する。

【解決手段】 被覆膜の結晶粒のAlN中に酸素を0.1質量%以上20質量%以下含有させて、被覆膜の熱膨張率を基材+に合わせるよう調整することを特徴とする。被覆膜の相対密度が50以上98%未満であることが好ましい。被覆膜が、化学気相成長法によって成膜され、その後、酸素雰囲気中で700℃以上1150℃以下の温度で加熱されること、あるいは、大気中で暴露させて水和物を形成させた後に不活性雰囲気中で900℃以上1300℃以下の温度で加熱処理されること、が好ましい。

(もっと読む)

ポロゲン、ポロゲン化前駆体、及び低誘電定数を有する多孔性有機シリカガラスフィルムを得るためにそれらを用いる方法

【課題】特性の向上した多孔性シリカガラスフィルムを提供する化学気相蒸着方法を提供する。

【解決手段】真空チャンバーに、オルガノシラン及びオルガノシロキサンからなる群から選択される少なくとも1つの前駆体、及び前駆体とは区別されるポロゲンを含めたガス状試薬を導入すること(ここに、ポロゲンは、非分岐構造及び2又はそれ未満の不飽和の度合いを有するC4〜C14環状炭化水素化合物である);エネルギーを真空チャンバー中のガス状試薬に適用してガス状試薬の反応を誘導し、基材上に予備的フィルムを蒸着させること(ここに、予備的フィルムはポロゲンを含有する);及び不安定有機物質の実質的に全てを予備的フィルムから除去して細孔及び2.6未満の誘電定数を有する多孔性フィルムを提供することを含む、多孔性有機シリカガラスフィルムを製造するための化学気相蒸着方法。

(もっと読む)

金属−絶縁体−金属キャパシタおよびその製造方法

【課題】等価酸化膜厚(EOT)が薄く、漏洩電流の小さいDRAM用のMIMキャパシタを提供する。

【解決手段】基板を準備するステップと、前記基板上に第1電気導電性層上を設けるステップと、原子層堆積法によって、前記導電性層上に層のサブスタックを設けるステップであって、前記サブスタックの少なくとも一層はTiO2層であり、サブスタックの他層は、ペロブスカイト相を形成するのに好適な組成を有する誘電体材料層であるステップとを含む。前記層のサブスタックを含む基板に熱処理を施し、結晶化した誘電体層を得る。サブスタックに存在する一連のTiO2層として改善した特性を有する金属−絶縁体−金属キャパシタを得るために、第2導電性層を熱処理の前または後に製造する。特に、本発明に係るMIMcapにおいて、誘電体層のk値は50〜100であり、MIMキャパシタのEOTは0.35nm〜0.55nmである。

(もっと読む)

気相成長装置

【課題】

2フローリアクタにおいて排気間に再び材料ガス流への中間反応ガスの巻き込みを防止し半導体素子の製造歩留まりを高める気相成長装置を提供することを目的とする。

【解決手段】

気相成長装置は、基板を担持して、これを加熱および回転するサセプタと、基板へ向かう材料ガス噴出口を有し、材料ガス噴出口から基板上に沿って材料ガスの層流を供給する材料ガスノズルと、基板へ向かう押さえガス噴出口を有し、押さえガス噴出口から押さえガスを、基板の法線方向から所定角度範囲で且つ基板の面積より広い面積で、押さえガス流として基板上に供給する押さえガス噴出器と、を備え、材料ガス噴出口および押さえガス噴出口から離れた材料ガスノズルの上方に離間して配置され且つ、押さえガス噴出口および材料ガス噴出口の間隙へ向かう遮断ガスを噴出する遮断ガス噴出口を有する遮断ガスノズルを有する。

(もっと読む)

半導体装置の製造方法

【課題】平坦なNiPtシリサイド層を形成する。

【解決手段】CVD法を用いて、シリコン層26(ゲート),29(ソース・ドレイン)上にPt層を形成する。次いで、CVD法を用いて、Pt層上にNi層を、Pt層より厚く形成する。次いで、シリコン層26,29、Pt層、及びNi層を熱処理することにより、NiPtシリサイド33を形成する。Pt層の平均膜厚が0.5nm以上2nm以下であるのが好ましい。またシリコン層は、例えばMISFETのソース・ドレインである。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】 基板を処理容器内に搬入する工程と、処理容器内に処理ガスを供給し排気することで、基板上に所定膜厚の金属膜を形成する処理を行う工程と、処理済基板を処理容器内から搬出する工程と、を有し、処理を行う工程では、金属膜を形成する途中もしくは金属膜を形成した後に処理容器内に酸素含有ガスおよび/または窒素含有ガスを熱またはプラズマで活性化して供給し排気することで、金属膜の底面もしくは表面を導電性の金属酸化層、導電性の金属窒化層または導電性の金属酸窒化層に改質する。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 高誘電率絶縁膜の吸湿を抑制し、信頼性を向上させる。

【解決手段】 処理容器内に基板を搬入する工程と、処理容器内で基板上に高誘電率絶縁膜を形成する工程と、処理容器内で高誘電率絶縁膜上に高誘電率絶縁膜よりも吸湿性の低い低吸湿性絶縁膜を形成する工程と、処理容器内より低吸湿性絶縁膜形成後の基板を搬出する工程と、を有する。

(もっと読む)

機能性フィルムの製造方法

【課題】真空中において長尺な基材フィルムを長手方向に搬送しつつ、基材フィルムへの無機膜の成膜、無機膜を保護するための保護フィルムの積層、積層体の巻取りを行う機能性フィルムの製造において、無機膜と保護フィルムとの間に存在する気泡に起因する無機膜の損傷を防止することを目的とする。

【解決手段】保護フィルムの積層に先立ち、無機膜の加熱処理を行うことにより、前記課題を解決する。

(もっと読む)

シリコンエピタキシャルウェーハの製造方法およびシリコンエピタキシャルウェーハ

【課題】{110}面からの傾斜角度が小さくてもヘイズレベルが良好で、かつシリコン単結晶エピタキシャル層の層厚均一性も良好であり、更に表面欠陥の少ないシリコンエピタキシャルウェーハの製造方法を提供する。

【解決手段】シリコン単結晶基板の主表面上にシリコン単結晶エピタキシャル層を気相成長させるシリコンエピタキシャルウェーハの製造方法であって、前記シリコン単結晶基板として、主表面が{110}面または{110}面からのオフアングル角度が0.5度未満のものを用い、かつ前記気相成長工程では、前記シリコン単結晶基板温度を1170℃〜1190℃として気相成長することを特徴とするシリコンエピタキシャルウェーハの製造方法。

(もっと読む)

半導体基板上での逆相境界の無いIII−V化合物半導体材料およびその製造方法

【課題】逆相境界(APB)の無いIII−V化合物半導体材料およびその製造方法を提供する。

【解決手段】III−V化合物半導体材料の製造方法は、a){001}配向を有する第1半導体材料からなる基板と、基板の上に位置し、これと接触する絶縁層と、絶縁層内に、少なくとも部分的に基板を露出させる凹部領域を用意する工程と、b)凹部領域において露出基板の上に位置し、これと接触するバッファ層を形成する工程工程と、c)バッファ層の表面を粗面化するために、熱処理を印加する工程とを含み、バッファ層が、熱処理の印加後に二重ステップ表面を有する丸み形状をなし、d)凹部領域を、バッファ層の二重ステップ表面の上に位置し、これと接触するIII−V化合物半導体材料で少なくとも部分的に充填する工程をさらに含む。

(もっと読む)

シリコン表面をパッシベーションする方法

【課題】良好なシリコン表面パッシベーション品質する表面パッシベーション方法を提供する。

【解決手段】シリコン表面をパッシベーションする方法であって、この方法は、(a)シリコン表面を洗浄する工程であって、最終工程が親水性のシリコン表面を得る化学的酸化工程である一連の工程に、シリコン表面を晒す工程を含む工程と、(b)進歩的な乾燥技術を用いて、洗浄したシリコン表面を乾燥させる工程と、(c)シリコン表面上に、ALDAl2O3層のような酸化物層を堆積する工程とを含む。

(もっと読む)

半導体領域の形成方法及び蓄電装置の作製方法

【課題】放電容量を高める等の蓄電装置の性能を向上させることが可能な蓄電装置の作製方法を提供する。また、蓄電装置等に用いることで性能を向上させることが可能な半導体領域の形成方法を提供する。

【解決手段】導電層上に、LPCVD法により、結晶性半導体で形成される複数のウィスカーを有する結晶性半導体領域を形成し、シリコンを含む堆積性ガスを含む原料ガスの供給を停止した後、結晶性半導体領域を加熱処理する結晶性半導体領域の形成方法である。また、当該結晶性半導体領域を蓄電装置の活物質層として用いる蓄電装置の作製方法である。

(もっと読む)

Co膜形成方法

【課題】膜中及び膜表面の不純物が効果的に除去でき、Cu配線構造に適用したときにバリア層及びCu配線層に対する密着性に優れて一層の低抵抗を実現できるCo膜形成方法を提供する。

【解決手段】基材Sを処理室10内に配置して処理室内を真空引きすると共に、基材を一の所定温度に加熱し、アルキル基を有するイオン又は分子がコバルトに配位した有機金属材料Lを気化させ、気化させた有機金属材料を基材表面に供給し、有機金属材料を熱分解させてCo膜を成膜する。その後、同一の処理室内で、またはCo膜が成膜された基材を他の処理室内に配置し、この基材をアンモニアガスと水素ガスとを含む混合ガス雰囲気中にて他の所定温度でアニールする。

(もっと読む)

炭化珪素半導体デバイスの製造方法

【課題】炭化珪素ウエハの表面の全体に渡って荒れの発生のない炭化珪素半導体デバイスの製造方法を提供とする。

【解決手段】本炭化珪素半導体デバイスの製造方法は、炭化珪素ウエハ10に不純物30iをイオン注入する工程と、不純物30iがイオン注入された炭化珪素ウエハ10上にダイヤモンド層40を形成する工程と、ダイヤモンド層40が形成された炭化珪素ウエ10を熱処理することにより、炭化珪素ウエハ10内に不純物30iが活性化した不純物領域30を形成する工程と、を備える。

(もっと読む)

成膜方法及び処理システム

【課題】比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成することが可能な成膜方法を提供する。

【解決手段】絶縁層1が表面に形成された被処理体Wに対して成膜処理を施す成膜方法において、第1の金属よりなる第1の薄膜60を形成する第1の薄膜形成工程と、前記第1の薄膜を酸化して酸化膜60Aを形成する酸化工程と、前記酸化膜上に第2の金属を含む第2の薄膜62を形成する第2の薄膜形成工程とを有する。これにより、比誘電率の低い絶縁層の表面にMn等の金属を含む薄膜、例えばMnOxを効率的に形成する。

(もっと読む)

成膜方法および成膜装置

【課題】凹凸形状部位にもリーク電流が小さく高誘電率のジルコニア系膜を確実に成膜することができる成膜方法および成膜装置を提供すること。

【解決手段】真空保持可能な処理容器内に被処理体を挿入し、処理容器内を真空に保持した状態とし、処理容器内にジルコニウム原料と酸化剤とをこの順に供給して被処理体上にZrO膜を形成する第1工程と、前記処理容器内にジルコニウム原料とシリコン原料と酸化剤とをこの順で供給して被処理体上にSiがドープされたZrO膜を形成する第2工程とを、それぞれの回数を調整して実施することにより、膜中のSi濃度を制御しつつ所定膜厚のジルコニア系膜を成膜する。

(もっと読む)

CVD炉の清浄度評価方法及びエピタキシャル基板の製造方法

【課題】半導体の製造に用いる装置の清浄度を、簡便かつ高感度で、局所的に解析出来る評価方法を提供することを目的とする。

【解決手段】基板に膜を形成する際に用いられるCVD炉の清浄度を評価する方法であって、少なくとも、CVD炉にて基板に膜を形成し、該成膜後の基板を非酸化性雰囲気下にてアニールした後、該アニール後の基板上に生成するパーティクル状の異物の数及び分布を観察することによりCVD炉の清浄度を評価することを特徴とするCVD炉の清浄度評価方法。

(もっと読む)

41 - 60 / 328

[ Back to top ]