Fターム[4M104BB13]の内容

Fターム[4M104BB13]の下位に属するFターム

Fターム[4M104BB13]に分類される特許

121 - 140 / 1,522

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

薄膜トランジスタとその製造方法、および当該薄膜トランジスタを用いた画像表示装置

【課題】隔壁形成プロセスを省き、かつ、塗布法により半導体溶液を所望の場所に形成し、トランジスタ素子分離を行うことのできる薄膜トランジスタを提供する。

【解決手段】基板上に形成された梯子状の凸部を有するゲートバス電極と、ゲートバス電極の表面形状に沿うように当該ゲートバス電極上および基板上に形成されたゲート電極と、ゲート電極の凹凸に沿うようにゲート電極上および基板上に形成されたゲート絶縁体層と、ゲート絶縁体層の凹部内に形成された半導体層と、半導体層の中央に形成された保護膜と、半導体層の両端部で接続されたソース電極とドレイン電極とを備える。

(もっと読む)

半導体装置

【課題】リーク電流を抑制した半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、第1導電型の半導体層、複数のトレンチ、絶縁層、導電層、第1半導体拡散層、及びアノード電極を有する。半導体層は、半導体基板上に形成され第1の不純物濃度よりも小さい第2の不純物濃度を有する。複数のトレンチは、半導体層の上面から下方に延びるように半導体層中に形成されている。導電層は、絶縁層を介してトレンチを埋めるように形成され且つ半導体層の上面から第1の位置まで下方に延びる。第1半導体拡散層は、複数のトレンチの間に位置する半導体層の上面から第2の位置に達し且つ第2の不純物濃度より小さい第3の不純物濃度を有する。アノード電極は、第1半導体拡散層とショットキー接合されている。半導体層の上面から第2の位置までの長さは、半導体層の上面から第1の位置までの長さの1/2以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】素子面積を増加させずに順電圧降下を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域と、第1電極と、第2半導体領域と、絶縁領域と、第2電極と、を備える。第1半導体領域は、第1部分と、第1主面上において第1主面に直交する第1方向に延在した第2部分と、を有する第1導電形の半導体領域である。第1電極は、第2部分と対向して設けられた金属領域である第3部分と、第3部分と、第2部分と、をむすぶ第2方向に延在し、かつ第1方向に延在する第4部分と、を有する。第2半導体領域は、第2部分と、第3部分と、のあいだに設けられ、第1半導体領域よりも不純物濃度の低い第1濃度領域を有し、第3部分とショットキー接合した第1導電形の半導体領域である。絶縁領域は、第4部分と、第2半導体領域と、のあいだに設けられる。第2電極は、第1部分と導通する。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

窒化ガリウム半導体素子

【課題】高出力の窒化ガリウムショットキー・ダイオード素子を提供する。

【解決手段】1〜6μmの厚さを有するn+型ドープしたGaNダイオードから製造した窒化ガリウムベースの半導体ショットキー・ダイオードをサファイア基板の上に配設する。1μmを超える厚さを有するn−型ドープしたGaNダイオードを、複数の細長形の指にパターン化した前記n+型ドープGaNダイオード上に配設し、金属層をn−型ドープGaN層上に配設し、それとの間にショットキー接合を形成する。細長形の指の層厚、長さおよび幅は、降伏電圧が500Vを超え、電流容量が1アンペアを超え、かつ順方向電圧が3V未満である素子を得るように最適化される。

(もっと読む)

半導体装置及び電子機器

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導

体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作

製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって

形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチ

ング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを

用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

半導体装置の製造方法

【課題】電解めっき工程において、めっき膜の膜厚均一性を向上させる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、集積回路が形成された第1の領域と、前記第1の領域を囲む第2の領域と、を有する半導体ウエハーの、前記第1の領域及び前記第2の領域に第1の導電層を形成する工程と、前記第1の導電層の上にレジスト層を形成する工程と、前記第2の領域の前記第1の導電層の第1の部分の上の第1レジスト層を残し、前記第2の領域の前記第1の導電層の第2の部分の上の第2レジスト層を除去するパターニング工程と、電極と、前記電極の電気的接続部に連続し、前記電極に電流を供給する配線と、を有する治具を、前記電気的接続部が前記第1レジスト層と接するように配置する工程と、前記電極に前記電流を供給して、電解めっきにより前記第1の導電層の上に第2の導電層を形成する工程と、を有する。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

電子素子用金属層、電子素子用金属層積層体、電子素子、トランジスタ素子

【課題】電流のリークを抑制する電子素子用金属層を提供する。

【解決手段】被形成面12に、金属インクを塗布し金属粒子層を形成しパターニングする。基板側からランプ照射し、金属粒子層の下層部分のみを溶融させ、下層部分の金属粒子どうしを融着させる。金属粒子の融着層14Aと金属粒子の非融着層14Bとをこの順で有する積層体で構成されたゲート電極14とする。

(もっと読む)

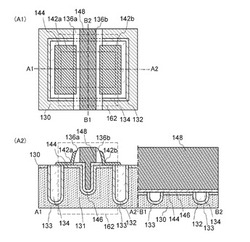

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体装置とその製造方法

【課題】高耐圧な半導体素子を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、第一と第二の主面を有する炭化珪素基板と、炭化珪素基板の第一の主面に設けられた第一導電型の第一の炭化珪素層と、第一の炭化珪素層の表面に形成された第二導電型の第一の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第一導電型の第二の炭化珪素領域と、第一の炭化珪素領域の表面に形成された第二導電型の第三の炭化珪素領域と、第一の炭化珪素層、第一の炭化珪素領域および第三の炭化珪素領域の表面に連続的に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された炭化珪素からなる第一の電極と、第一の電極上に形成された第二の電極と、第一と第二の電極を被覆する層間絶縁膜と、第二の炭化珪素領域と第三の炭化珪素領域と電気的に接続される第三の電極と、炭化珪素基板の第二の主面に形成された第4の電極と、を具備することを特徴とする。

(もっと読む)

半導体装置の作製方法

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

有機電子素子用電極、有機トランジスタ素子、インクジェットインク

【課題】接触抵抗を低減した有機電子素子用電極、及びこれを利用した有機トランジスタ素子を提供することを課題とする。

【解決手段】カーボンナノホーンを含んで構成された有機電子素子用電極、及び当該電極を、ソース電極18、及びドレイン電極20として適用した有機トランジスタ素子。

(もっと読む)

半導体発光素子及びその製造方法

【課題】高輝度化を図ることができる半導体発光素子及びその製造方法を提供する。

【解決手段】実施形態に係る半導体発光素子は、構造体と、第1電極層と、電極層と、無機膜と、を備える。構造体は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、第1半導体層と第2半導体層との間に設けられた発光層と、を有する。電極層は、構造体の第2半導体層の側に設けられる。電極層は、金属部と、複数の開口部と、を有する。金属部は、第1半導体層から第2半導体層に向かう方向に沿った厚さが10nm以上、100nm以下である。開口部は、前記方向に沿って金属部を貫通し、円相当直径が10nm以上、5μm以下である。無機膜は、前記方向に沿った厚さが20nm以上、200nm以下で、金属部の表面及び開口部の内面を覆うように設けられ、発光層から放出される光に対して透過性を有する。

(もっと読む)

半導体装置の製造方法

【課題】高歩留まりの薄型半導体装置の製造方法を提供する。

【解決手段】まず、半導体ウェハ10の第1の主面S1に、複数の素子領域3およびこの素子領域3にコンタクトする端子電極5を形成し、こののち半導体ウェハ10の第1の主面S1と対向する第2の主面S2を、半導体ウェハ10の外周縁部を残して、所望の厚さとなるまで、薄肉化する。そして、薄肉化された半導体ウェハ10の前記第2の主面S2に、金属層6を形成し、こののち、金属層6上に絶縁被膜7を形成し、最後に、半導体ウェハ10の素子領域3毎にダイシングラインD.L.に沿って分割することで、分断された個々の半導体装置を得るものである。

(もっと読む)

ショットキーバリア型半導体装置

【課題】低バイアス領域からリーク電流IRの低減効果を得ることのできるショットキーバリア型半導体装置を提供する。

【解決手段】表面に第1導電型を有する第1の半導体層2を有する半導体基板と、第1の半導体層の表面から所定の深さに設けられ、第1導電型の半導体層よりも低濃度の第1導電型を有する第2の半導体層3と、第1の半導体層の表面から所定の深さに配設されたジャンクションバリアとして第2導電型を有する複数の第3の埋め込み半導体層5と、第1の半導体層の表面で第3の埋め込み層を囲むように環状に形成された、第2導電型を有するガードリング4と、第1の半導体層およびガードリングに接するように配置された金属層6を具備したショットキーバリア型半導体装置であって、第2の半導体層の比抵抗が第1の半導体層の比抵抗よりも高い。

(もっと読む)

ショットキーバリア型半導体装置

【課題】リーク電流IRの低減を維持しつつ耐圧の向上をはかることのできるショットキーバリア型半導体装置を提供する。

【解決手段】ショットキーバリア型半導体装置において、ガードリング4の外側で、第1の半導体層の表面から所定の深さに配設されたジャンクションバリア5としての埋め込み半導体層を具備する。

(もっと読む)

半導体発光素子及び半導体発光装置

【課題】高輝度、高効率、高信頼性を達成する半導体発光素子を提供する。

【解決手段】実施形態に係る半導体発光素子は、積層構造体と、電極と、を備える。積層構造体は、窒化物系半導体からなる第1導電形の第1半導体層と、窒化物系半導体からなる第2導電形の第2半導体層と、前記第1半導体層と前記第2半導体層との間に設けられた発光層と、を有する。電極は、第1金属層、第2金属層及び第3金属層を有する。第1金属層は、第2半導体層の発光層とは反対側に設けられ、銀または銀合金を含む。第2金属層は、第1金属層の第2半導体層とは反対側に設けられ、金、白金、パラジウム、ロジウム、イリジウム、ルテニウム、オスミウムの少なくともいずれかの元素を含む。第3金属層は、第2金属層の第1金属層とは反対側に設けられる。第3金属層の第1半導体層から第2半導体層に向かう方向に沿った厚さは、第2金属層の前記方向に沿った厚さ以上である。

(もっと読む)

トランジスタ装置

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース18、ドレイン20、およびゲート22を含む。第1のスペーサ層26が、活性領域の上方でソースとゲートの間にあり、第2のスペーサ層28が、活性領域の上方でドレインとゲートの間にある。第1のスペーサ層上の第1のフィールドプレート30、及び第2のスペーサ層上の第2のフィールドプレート32が、ゲートに接続される。第3のスペーサ層34が、第1のスペーサ層、第2のスペーサ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、第3のフィールドプレート36が、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

121 - 140 / 1,522

[ Back to top ]