Fターム[4M104BB30]の内容

Fターム[4M104BB30]に分類される特許

1,441 - 1,457 / 1,457

高K誘電体膜

誘電体層(14,22,24,32)は、ランタン、ルテチウム、及び酸素により構成され、かつ2つの導体の間、または導体(14,20,34)と基板(12,26,30)との間に形成される。一の実施形態では、誘電体層は基板を覆って形成され、境界層を追加する必要がない。別の実施形態では、誘電体層(22,42,46)に含まれる元素の分布は、ランタン含有量またはルテチウム含有量に関して傾斜する、または誘電体層(22,42,46)は別の構成として、アルミニウムを含むことができる。更に別の実施形態では、絶縁層を導体または基板と誘電体層との間、または導体及び基板の両方と誘電体層との間に形成する。誘電体層は、分子ビームエピタキシー法によって形成することが好ましいが、原子層化学気相成長、物理気相成長、有機金属化学気相成長、またはパルスレーザ堆積によって形成することもできる。  (もっと読む)

(もっと読む)

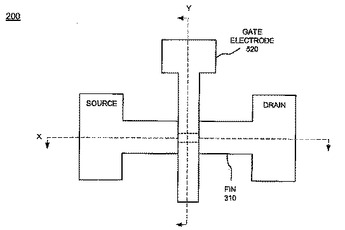

セルフアラインされたダマシンゲート

基板上のフィン領域、ソース領域、およびドレイン領域をパターン化するステップと、フィン領域中にフィン(310)を形成するステップと、フィン領域中にマスク(320)を形成するステップと、を含む、MOS電界効果トランジスタ(MOSFET)(200)を形成する方法である。この方法は、MOSFETのチャネル領域(330)を露出するように、マスク(320)をエッチングするステップと、チャネル領域(330)中のフィン(310)の幅を薄くするようにフィン(310)をエッチングするステップと、フィン(310)上にゲートを形成するステップと、ゲート、ソース領域およびドレイン領域に対するコンタクトを形成するステップと、をさらに含む。  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

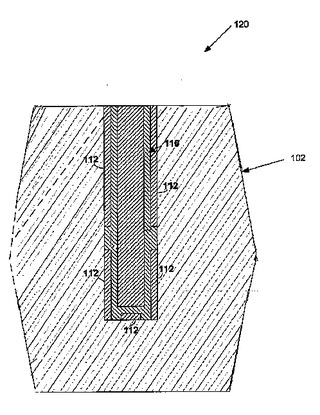

無電解メッキ化学反応を用いた深いビアシードの修復

高アスペクト比ビア内に連続シード層を形成する方法とそれに関連付けられる構造体を記載する。この方法は、基板内に凹部(104)を形成する段階と、凹部内に非連続金属層を形成する段階と、凹部内の非連続金属層(112)と、少なくとも1つの非堆積領域(109)を活性化させる段階と、凹部内の非連続金属層及び少なくとも1つの非堆積領域上にシード層(116)を無電解メッキする段階と、実質的にボイドがなく、金属が充填された凹部を形成するようシード層上に金属充填層を形成する段階を含む。  (もっと読む)

(もっと読む)

チャンバに対してガスを出し入れする装置

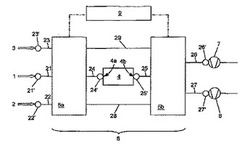

【課題】処理チャンバから排出される種についての交差反応を著しく低減できるような装置を提供する。

【解決手段】装置が、チャンバ入口とチャンバ出口とを有するチャンバと、第1のガス流を受け入れるための第1の入口と、第2のガス流を受け入れるための第2の入口と、第1のガス流を第1の真空ポンプへと出力する第1の出口と、第2のガス流を第2の真空ポンプへと出力する第2の出口と、導管ネットワークであって、第1の入口を第1の出口に結合し、第2の入口を第2の出口に結合し、それぞれのガス流について、第1の流路と第2の流路とをそれぞれの入口と出口との間に形成し、第1の流路はチャンバ入口とチャンバ出口とを通り抜け、第2の流路はチャンバを迂回するような上記導管ネットワークと、ネットワークを通り抜けるガス流の経路を割り当てて、あるガス流が第1の流路に沿って流れるとき、他方のガス流を第2の流路に沿って流れさせる経路割当手段と、を備えている。

(もっと読む)

high−kゲート誘電体プロセスインテグレーションのための界面酸化プロセス。

【課題】 high−kゲート誘電体プロセスインテグレーションのための界面酸化プロセスの提供。

【解決手段】 界面酸化層を有した微細構造物を形成する方法は、この微細構造物内のhigh−k層の形成と関係した基板の酸化特性を制御するように拡散フィルタ層を使用することにより提供される。拡散フィルタ層は、表面の酸化を制御する。界面酸化層は、拡散フィルタ層上へのhigh−k層の堆積の後に実行される酸化プロセス中に、または拡散フィルタ層上へのhigh−k層の堆積中に、形成されることができる。

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

半導体基板上の、超臨界流体による物質の蒸着

集積回路デバイス製造のための半導体基板のような基板上への、超臨界流体を利用した物質の蒸着。蒸着は、基板表面に蒸着される物質の前駆体を含む、超臨界流体をベースとする組成物を使用して行われる。そのようなアプローチにより、気相蒸着工程に必要な揮発性および搬送性がないために、蒸着への適用には全く不適切であった前駆体の使用が可能になる。 (もっと読む)

多層配線構造の製造方法

【課題】高集積化、微細化されたパターンにおいて、ビアホール等を良好に埋め込み、かつ電気抵抗率の低い埋め込み型の多層配線構造を提供する。

【解決手段】埋め込み型の多層配線構造の製造方法が、絶縁層に孔部を形成する工程と、孔部の表面に、物理的真空堆積法で、平均膜厚が0.2nm以上で10nm以下である触媒層6、または触媒層の平均膜厚が、触媒層の材料原子の1原子層以上で10nm以下である触媒層6、を形成する工程と、触媒層を触媒に用いた無電解めっき法により、孔部の表面に無電解めっき層7を形成する工程と、無電解めっき層をシード層に用いた電解めっき法で、孔部を電解めっき層8で埋め込む工程とを含む。

(もっと読む)

バリヤ金属上に直接銅めっきするマルチステップ電着法

本発明の実施形態は、基板表面に、通常はバリヤ層に銅シード層を堆積させる方法を教示している。その方法は、基板表面を銅溶液に入れるステップであって、該銅溶液が錯体形成銅イオンを含んでいる、前記ステップを含んでいる。電流又はバイアスを基板表面に印加し、錯体形成銅イオンを還元してバリヤ層に銅シード層を堆積させる。 (もっと読む)

バリヤ物質の原子層堆積

1以上の物質層のバリヤ層を原子層堆積により堆積させるために基板を処理する方法が提供される。一態様においては、金属含有化合物の1以上のパルスと窒素含有化合物の1以上のパルスを交互に導入することにより基板表面の少なくとも一部上に金属窒化物バリヤ層を堆積させるステップと、金属含有化合物の1以上のパルスと還元剤の1以上のパルスを交互に導入することにより金属窒化物バリヤ層の少なくとも一部上に金属バリヤ層を堆積させるステップとを含む基板を処理する方法が提供される。金属窒化物バリヤ層及び/又は金属バリヤ層の堆積前に基板表面上で浸漬プロセスが行われてもよい。 (もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

多端子カルコゲニドスイッチングデバイス

抵抗状態および導電状態間で切替可能なカルコゲニド材料を含む多端子電子スイッチングデバイスである。このデバイスは、第1の端子と、第2の端子と、制御端子を備える。制御端子に制御信号を印加することによって第1の端子および第2の端子間の前記カルコゲニド材料の導電性および/または第1の端子および第2の端子間の前記カルコゲニド材料を抵抗状態から導電状態へスイッチするのに必要な閾値電圧を変調する。このデバイスは回路またはネットワーク内で相互接続デバイスまたは信号付与デバイスとして用いることもできる。 (もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

多層配線構造の製造方法及びその構造

【課題】 上層配線層と下層配線層とを、アスペクト比の高いビアコンタクトで接続した多層配線構造を提供する。

【解決手段】 多層配線構造のビアコンタクト形成工程が、ビアホールの底面上に触媒層を設け、触媒層上にビアホールの上方に向ってめっき金属層を成長させ、めっき金属層でビアホールを充填する無電解めっき工程からなる。

(もっと読む)

窒化物系III―V族化合物半導体装置の電極構造

【課題】 半導体上の膜付着力が強く、かつ温度特性が優れたショットキー電極を備えた窒化物系III−V族化合物半導体装置の電極構造を提供する。

【解決手段】 この窒化物系III−V族化合物半導体装置の電極構造は、電極4の材料として金属窒化物(窒化タングステン)を用いたので、半導体GaN層3への膜付着力が強く、かつ、加熱によってショットキー特性が劣化することがないショットキー電極4を得ることができた。

(もっと読む)

1,441 - 1,457 / 1,457

[ Back to top ]