Fターム[4M104CC03]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574) | ショットキー接触電極 (1,047)

Fターム[4M104CC03]に分類される特許

201 - 220 / 1,047

半導体装置およびその製造方法

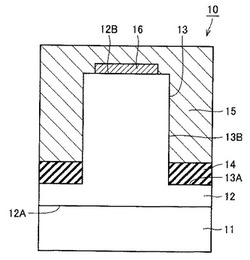

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の表皮効果の抑制と低抵抗化を図る。

【解決手段】第1配線部41と、その第1配線部41の周りを被覆する、高融点金属窒化物を含む第2配線部42とを含む配線40aを形成する。このような配線40aにおける第2配線部42は、第1配線部41側から外周に向かって窒素含有率が高くなる部分を有するように形成する。これにより、配線40aにおける表皮効果が抑制されると共に、配線40aの低抵抗化が図られるようになる。

(もっと読む)

電界効果トランジスタ

【課題】導体半導体接合を用いた電界効果トランジスタのオフ電流を低減せしめる構造を提供する。

【解決手段】半導体層1に、半導体層1の電子親和力と同程度かそれ以下の仕事関数の材料よりなる第1の導体電極3a、第2の導体電極3bを接して設け、さらに、半導体層1のゲートの形成された面と逆の面に接して、半導体層1の電子親和力より大きな仕事関数の材料で、半導体層を横切るようにして、第3の導体電極2を形成することにより、半導体層中にショットキーバリヤ型の接合を形成し、この部分のキャリア濃度が極めて低いことから、オフ電流を低減できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体装置のソース電極、ドレイン電極及びゲート電極を形成するいずれの領域においても、残渣のない良好な半導体/金属界面が得られるようにする。

【解決手段】化合物半導体装置の製造方法を、基板1上に化合物半導体積層構造4を形成する工程と、化合物半導体積層構造上に金属膜5A〜5Cを形成する工程と、金属膜上にソース電極7及びドレイン電極8を形成する工程と、金属膜の一部を酸化又は窒化して、金属酸化物膜又は金属窒化物膜5CXを形成する工程と、金属酸化物膜又は金属窒化物膜上にゲート電極9を形成する工程とを含むものとする。

(もっと読む)

シリコンおよびIII−V族のモノリシック集積デバイス

【課題】シリコン基板上にIII−V族半導体で形成されたHEMTとシリコン面に形成されたショツトキーダイオードのモノリシック集積デバイスを開示する。

【解決手段】少なくとも1つのビアは、III−V族半導体を通じて延在して、III−V族トランジスタの少なくとも1つの端子をシリコン基板に形成されたシリコンデバイスに結合させる。シリコンデバイスはショットキーダイオードと、III−V族トランジスタはGaNHEMTとすることができる。ショットキーダイオードのアノードは、一実施形態においては、シリコン基板202に形成され、他の実施形態においては、シリコン基板上の低濃度にドープされたエピタキシャルシリコン層204に形成される。HEMTはGANで構成されたチヤネル層212、AlGaNで構成された電子供給層214より構成される。

(もっと読む)

広バンドギャップショットキー障壁デバイス用の多層拡散障壁

窒化物半導体デバイス

【課題】 窒化物半導体デバイスを提供する。

【解決手段】 一実施形態では、デバイスはIII族窒化物チャネル層(3)とIII族窒化物チャネル層(3)上のIII族窒化物障壁層(4)とを含み、III族窒化物障壁層(4)は第1部分(4−1)と第2部分(4−2)とを含み、第1部分(4−1)は第2部分(4−2)より薄い厚さを有する。pドープIII族窒化物ゲート層部(5)は、III族窒化物障壁層(4)の少なくとも第1部分(4−1)上に配置され、ゲートコンタクト(10)はpドープIII族窒化物ゲート層部(5)上に形成される。

(もっと読む)

半導体装置

【課題】Ti、PtおよびAuからなるゲート電極を有するリセス構造を有し、Ti上のPt若しくはAuが、素子領域表面のAlGaAs層に拡散することを抑制する半導体装置を提供する。

【解決手段】GaAs基板11上に形成された素子領域16と、第1のリセス領域25と、第2のリセス領域26と、第1のリセス領域25外の素子領域16上に、互いに離間して形成されたドレイン電極13およびソース電極14と、第2のリセス領域26の表面の一部に接し、第1のリセス領域25の表面の一部に接するゲート電極15を具備し、最下層が、第1のリセス領域25、および第2のリセス領域26の表面の一部に接するように、隙間を有して形成された第1のTi層29と、第1のTi層29上に、第1のTi層29の隙間を埋めるように形成されたAl層30と、Al層30上に形成されたPt層32と、Pt層上に形成されたAu層33と、を含むように構成する。

(もっと読む)

ヘテロ接合障壁領域を含む半導体デバイス及びその製造方法

電界効果トランジスタ

【課題】電流コラプスが抑制された窒化物半導体を用いた電界効果トランジスタを容易に実現できるようにする。

【解決手段】電界効果トランジスタは、基板100の上に形成され、第1の窒化物半導体層122及び第2の窒化物半導体層123を有する半導体層積層体102を備えている。半導体層積層体102の上には、互いに間隔をおいてソース電極131及びドレイン電極132が形成されている。ソース電極131とドレイン電極132との間には、ソース電極131及びドレイン電極132と間隔をおいてゲート電極133が形成されている。ドレイン電極132の近傍には正孔注入部141が形成されている。正孔注入部141は、p型の第3の窒化物半導体層142及び第3の窒化物半導体層142の上に形成された正孔注入電極143を有している。ドレイン電極132と正孔注入電極142とは、電位が実質的に等しい。

(もっと読む)

半導体装置

【課題】半絶縁性基板に形成されたゲートパッドにマイナスの電圧が印加され、半絶縁性基板の裏面に形成された裏面電極にプラスの電圧が印加されても、リーク電流を抑制できる半導体装置を提供する。

【解決手段】裏面電極10が形成された半絶縁性基板11の表面上に並列に形成された、複数のゲート電極15がゲート電極接続部21に接続されるとともに、このゲート電極接続部21が複数に分割された半導体装置であって、ゲート電極接続部21間の半絶縁性基板11の表面に形成されたn型の抵抗層22と、このn型の抵抗層22の周囲を覆うように、p型不純物層23と、このp型不純物層23の周囲を覆うように、所望の濃度で形成されたn型不純物層24と、を具備し、ゲートパッド29は、ゲート電極接続部21と、このゲート電極接続部21に隣接するn型の抵抗層22上の引き出し電極25とを接続するように形成される。

(もっと読む)

ショットキーバリアダイオードを備えた炭化珪素半導体装置およびその製造方法

【課題】ショットキーバリアハイトの低減とリーク電流の低減を両立する。

【解決手段】ショットキー電極4とSiCとの界面にSiOXにて構成される界面層が形成されることなく、ショットキー電極4を構成する金属の各粒子がSiCの表面において、原子配列が連続的となった格子整合した状態となるようにする。具体的には、ショットキー電極4を構成する金属の粒子構造が柱状構造ではなく粒状構造となるようにし、柱状構造となっている場合と比較して、粒子間の境界を通じて界面に酸素が取り込まれ難くなるようにすることで、SiOXが形成されないようにしてショットキー電極4を構成する金属をSiCと格子整合させる。

(もっと読む)

半導体発光装置

【課題】局所的な電流集中を防止して均一な発光分布を得ることができる半導体発光装置を提供する。

【解決手段】半導体発光装置は、支持基板と、支持基板上に設けられた光反射性を有する反射電極と、反射電極上に設けられた発光層を含むAlGaInP系半導体膜と、半導体膜上に設けられた表面電極と、を含む。表面電極は、半導体膜上に分散配置された複数の電極片からなるオーミック電極を含む。反射電極は、オーミック電極を構成する電極片の各々を挟んだ両側において電極片に沿うように設けられた線状のライン電極および複数の島状のドット電極からなる。ライン電極とドット電極との距離をa、オーミック電極とドット電極の水平距離をb、互いに隣接するドット電極間の距離をcとしたときに、b>a且つ0.8(a2+2ab)1/2<c<2.4(a2+2ab)1/2を満たすように表面電極および反射電極が配設される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】表面平坦性に優れ、電極のパターン形成性に優れるオーミック接合層を備える半導体装置を提供する。

【解決手段】n型のSiC半導体基体1と、SiC半導体基体1の一方の主表面1bとオーミック接触するカソード電極5と、SiC半導体基体1の他方の主表面1aに形成されたp型SiCからなる第1半導体領域6aと、他方の主表面1aに形成されたn型SiCからなる第2半導体領域6bと、第1半導体領域6aにオーミック接触するオーミック接合層7と、第2半導体領域6bにショットキー接触するショットキー接合層8と、を備え、オーミック接合層7が、第1半導体領域6a側からチタンとニッケルとを含む合金からなると共に、その上にモリブデンを主成分とする金属層を有し、ショットキー接続層8が、モリブデンを主成分とする金属からなることを特徴とする半導体装置である。

(もっと読む)

整流素子およびその製造方法

【課題】定常損失を低減しつつ耐圧を向上することのできる整流素子およびその製造方法を提供する。

【解決手段】整流素子10は、ショットキー電極5、3と、カソード電極4との電位差が変化することにより、ショットキー電極5とカソード電極4との間に電流を流す状態と、ショットキー電極5とカソード電極4との間に存在するn-半導体層2を空乏層化することによって電流経路を遮断する状態とを選択可能である。上記ショットキー障壁φBn1が、0.68eV<φBn1<1.05eVという関係を満足し、かつ250℃の温度でもショットキー電極5とn-半導体層2とのショットキー接触を確保できる。上記ショットキー障壁φBn2は、1.06eV<φBn2という関係を満足する。

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】凹部4c内に形成されたi型(イントリンシック半導体)側壁層5を介してp+型ゲート領域6を形成する。このような構成とすれば、n+型層4とp+型ゲート領域6との間にさらにp+型ゲート領域6よりも低濃度のp-型層が必要とされない。このため、n-型チャネル層3に直接接触している高濃度のp+型ゲート領域6によって、n-型チャネル層3内に伸びる空乏層幅を制御できる。したがって、n+型層4とp+型ゲート領域6との間にさらにp-型層が備えられる場合と比較して、ゲート印加電圧が高電圧になることを抑制できる。また、p+型ゲート領域6の側面がi型側壁層5によってn+型層4と分離されるため、ゲート−ソース間およびゲート−ドレイン間のキャパシタンスを低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度と、優れた縦方向耐圧とを得た上で、安定して低いオン抵抗を確保することができる、半導体装置等を提供する。

【解決手段】本発明の半導体装置は、n型ドリフト層4/p型層6/n型表層8を含むGaN系積層体15、に形成され、GaN系積層体には、開口部5が設けられ、再成長層27と、ゲート電極11と、ソース電極31と、ドレイン電極39とを備え、再成長層27は電子走行層22および電子供給層26を含み、チャネルが二次元電子ガスであり、p型層6とn型表層8との間、および開口部を囲むGaN系積層体の端面と再成長層との間、の少なくとも一方に、GaNよりも格子定数が小さいエピタキシャル層が挿入されていることを特徴とする。

(もっと読む)

201 - 220 / 1,047

[ Back to top ]