Fターム[4M104DD08]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は絶縁膜の除去方法 (1,213) | ドライエッチ (710)

Fターム[4M104DD08]に分類される特許

81 - 100 / 710

半導体装置

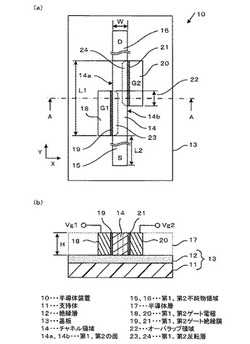

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】イオン注入を用いることなく2次元正孔ガスの所期の濃度分布を容易且つ確実に得て、電界集中のなだらかな緩和を実現する高信頼性の窒化物半導体装置を得る。

【解決手段】n−GaN基板1のN面上に形成されたn−GaN層2と、n−GaN層上に形成されたAlGaNからなるJTE構造10と、n−GaN層2上に形成されたアノード電極4とを有しており、n−GaN層2のJTE構造10との界面に、アノード電極4から離間するほど正孔濃度が低くなるように、2次元正孔ガスが生成される。

(もっと読む)

パターンの形成方法

【課題】LELEプロセスよりも少ない工程数で、フォトリソグラフィ技術を2度使用することなく、微細なホール又はトレンチパターンを形成する方法を提供すること。

【解決手段】被処理体の上にレジスト膜を成膜し、成膜した前記レジスト膜をパターニングする、レジスト膜形成工程と、前記被処理体及び前記レジスト膜を被覆するようにスペーサ膜を成膜して、前記スペーサ膜で囲まれた凹部を形成する、スペーサ膜成膜工程と、前記凹部の底面にある前記被処理体及び前記レジスト膜の上面を露出させると共に、前記レジスト膜の側面側に前記スペーサ膜が残るようにエッチングして、前記凹部から第1の開口部を形成する、第1開口部形成工程と、前記レジスト膜を除去することにより第2の開口部を形成する、第2開口部形成工程と、を含むパターンの形成方法。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】実施形態によれば、ホールの深さのばらつきを防ぐ半導体装置の製造方法及び半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、複数の第1の開口と第1の開口よりも密に並んだ複数の第2の開口とを有するマスクを用いて層間絶縁層61をドライエッチングし、第1の開口の下で下地層10に達する第1のホールと、第2の開口の下で下地層10に達する第2のホール41とを同時に形成する工程を備えている。第1のホールは他の第1のホールとは接することなく下地層10に達する。ドライエッチングの開始後、複数の第2の開口のそれぞれの下に複数のホールhが形成され、ドライエッチングの進行に伴って、複数のホールhは少なくとも開口端を含む上部42で互いにつながる。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトとアクティブエリアとの間のショートマージンを確保できる半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置は、半導体基板と、前記半導体基板の上層部分に形成され、前記上層部分を第1方向に延びる複数本のアクティブエリアに区画する複数本の素子分離絶縁体と、前記アクティブエリアに接続されたコンタクトと、を備える。そして、各前記アクティブエリアの上面のうち、前記第1方向における一部の領域には、前記第1方向に対して直交する第2方向において前記アクティブエリアの全体にわたって凹部が形成されている。前記第1方向において、隣り合う前記アクティブエリアにそれぞれ接続された2本の前記コンタクトの位置は相互に異なる。前記コンタクトは前記凹部の側面に接し、底面には接していない。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、フィールドプレート構造を絶縁膜の開口中心に対してばらつきなく形成できる半導体装置の製造方法を提供することを目的とする。

【解決手段】本願の発明にかかる半導体装置の製造方法は、半導体層の表面に絶縁膜を形成する工程と、該絶縁膜の表面に開口を有するレジストを形成する工程と、該レジストと架橋反応するパターンシュリンク剤を該レジストに付着させ、該レジストの内周に硬化層を形成する工程と、該レジスト及び該硬化層をマスクとして該絶縁膜をエッチングする工程と、該硬化層を除去する工程と、該半導体層、該絶縁膜、及び該レジストの表面に金属層を形成する工程と、リフトオフ法により該レジスト及び該レジストの表面の該金属層を除去する工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、異なる膜特性を有する絶縁膜に形成されるコンタクト形状の制御性を向上させる。

【解決手段】半導体基板に素子領域を形成し、半導体基板の第1の領域上に、第1の絶縁膜を形成し、半導体基板の第2の領域上に、膜応力及びコンタクトの形成の際のエッチング加工時のエッチングレートが、第1の絶縁膜と異なる第2の絶縁膜を形成し、少なくとも第2の絶縁膜において、コンタクトが形成されるコンタクト領域に選択的にUV光を照射し、UV光を照射した後、第1の絶縁膜及び前記第2の絶縁膜をエッチングして前記コンタクトを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】配線加工時のエッチングレートの極端な上昇を抑え、プロセスを安定化させる。

【解決手段】炭化珪素基板1上に形成された炭化珪素層20の上に、ソース電極8、ゲート電極9、層間絶縁膜10、層間絶縁膜10上に形成されたソース電極上部配線11およびゲート電極上部配線12とが形成され、ソース電極上部配線11とゲート電極上部配線12の下には、これらの上部配線を構成する金属が炭化珪素層20に拡散することを抑制するためのバリアメタル16が形成されている。層間絶縁膜10には、炭化珪素層20上に形成されたソース電極8およびゲート電極9に到達するようにコンタクトホール13、15が形成されており、バリアメタル16はコンタクトホール内の電極と上部配線との界面、層間絶縁膜10の側壁と上部配線との界面、および側壁の上端部近傍と上部配線との界面にのみ形成されている。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】炭化珪素半導体層に設けられたリセス底部の不純物領域を含む終端構造の形成において、リセスの底端部に発生したノッチを除去あるいは緩やかな形状にする。

【解決手段】ガードリング6の形成領域のSiCドリフト層2にリセス7を形成したとき、リセス7の底端部に尖ったノッチ11が現れる。リセス7の形成後、リセス7の内部を含むSiCドリフト層2の表面を熱酸化して酸化層12を形成し、当該酸化層12をエッチングにより除去すると、ノッチ11は緩やかな形状になる。

(もっと読む)

半導体装置の製造方法

【課題】工程を簡素化して歩留まりを向上すると共に、安定した形状の電極を再現性よく得ることができる半導体装置の製造方法を提供する。

【解決手段】第1のレジスト膜11と、第1のレジスト膜11の開口よりも小さな開口を有する第2のレジスト膜12とを用いて、SiO2絶縁膜10を異方性ドライエッチングによってエッチングして、SiO2絶縁膜10にテーパ状の開口部101を形成する。このため、GaN層1を斜めに設置し直してSiO2絶縁膜10をエッチングする必要がなく、GaN層1を水平に設置したままSiO2絶縁膜10をエッチングすることができ、工程を簡素化できる。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】DRAMセルとロジックを混載したLSIデバイスにおけるアスペクト比の大きいコンタクト構造において、素子分離絶縁膜および不純物拡散層のオーバエッチングを抑制して、接合リークを抑制することを課題とする。

【解決手段】周辺MOSトランジスタを覆う第1エッチングストッパ層121と、DRAMメモリセルのキャパシタ部上層に第2エッチングストッパ層122が形成され、周辺MOSトランジスタの不純物拡散層113は、第1、第2エッチングストッパ層121、122を貫通する電極層131により、上記キャパシタ部上層に形成された金属配線層と接続され、不純物拡散層113の少なくとも一つは素子分離絶縁膜102の境界上に電極層131を接続し、素子分離絶縁膜102上に形成された電極層131の底部の不純物拡散層113表面からの深さ寸法は、不純物拡散層113の接合深さ寸法もより短く形成されたものである。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】耐圧が高く破壊等が生じにくい、信頼性の高い半導体装置を提供する。

【解決手段】基板上に形成された第1の半導体層12と、前記第1の半導体層上に形成された第2の半導体層14と、所定の領域の前記第2の半導体層の一部または全部を除去することにより形成されているゲートリセス22と、前記ゲートリセス及び第2の半導体層上に形成されている絶縁膜31と、前記ゲートリセス上に絶縁膜を介して形成されているゲート電極32と、前記第1の半導体層または前記第2の半導体層上に形成されているソース電極33及びドレイン電極34と、を有し、前記ゲートリセスの底面は、中央部分23aが周辺部分23bに対し高い形状であることを特徴とする半導体装置。

(もっと読む)

電力用半導体装置

【課題】オン電圧および損失の低減を可能にする電力用半導体装置を提供する。

【解決手段】pベース層2の表面からn−層1の第1の主面に対して垂直方向で、n−層1内に達する位置まで形成され、その後n−層1の第1の主面に対して水平方向で、片側に所定の長さ延出した底部3dを有したL字形のトレンチゲート21を備え、さらに所定の隣合うL字形のトレンチゲート21の底部21dの延出方向が対向するようにして、それぞれの底部21dの間隔が、n−層1の第1の主面に対して垂直方向に形成されている部分の間隔より狭くなるようにしたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで高い信頼性を有する、半導体装置およびその製造方法を提供すること。

【解決手段】n型半導体基板の一方の主面に、p型ベース領域とn型エミッタ領域と所要の位置にゲート絶縁膜を介して載置されるゲート電極とからなるMOSゲート構造と該MOSゲート構造を沿面方向に取り巻く耐圧構造部とを有し、他方の主面に1μm以下の浅い逆阻止接合を有するp型コレクタ層を備える半導体装置において、前記コレクタ層の他方の主面上に、バッファ絶縁層を介して被覆されるコレクタ電極が、前記バッファ絶縁層に設けられたコンタクトホールを通して前記コレクタ層と導電接触する半導体装置とする。

(もっと読む)

半導体エピタキシャル結晶基板及びその製造方法

【課題】高性能の窒化ガリウム系トランジスタを製造するための、誘電体膜付の半導体エ

ピタキシャル結晶基板を提供すること。

【解決手段】下地基板1上にエピタキシャル法によって、バッファ層2、チャネル層3、

及び電子供給層4から成る窒化ガリウム半導体結晶層を形成した後、エピタキシャル成長

炉内で連続してAlNを電子供給層4上に誘電体膜の前駆体として積層し、しかる後、積

層した前駆体に対して酸化処理を施すことによって誘電体膜5を形成する。

(もっと読む)

半導体装置

【課題】本発明は、薄膜トランジスタのソース領域やドレイン領域へのコンタクトを確実

にした半導体装置を提供するものである。

【解決手段】本発明における半導体装置において、半導体層上の絶縁膜およびゲイト電極

上に形成された第1の層間絶縁膜と、前記第1の層間絶縁膜の上に形成された第2の層間

絶縁膜と、前記第2の層間絶縁膜、前記第1の層間絶縁膜、および前記絶縁膜に設けられ

たコンタクトホールとを有する。前記第1の絶縁層の膜厚は、前記積層の絶縁膜の合計膜

厚の1/3以下に形成する。

(もっと読む)

81 - 100 / 710

[ Back to top ]