Fターム[4M104DD15]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744)

Fターム[4M104DD15]の下位に属するFターム

Fターム[4M104DD15]に分類される特許

161 - 180 / 226

半導体素子

【課題】電極または金属配線と所望の絶縁膜とを密着でき、所望の低リーク電流特性および高耐圧特性を得ることができること。

【解決手段】この発明にかかるHEMT100は、基板1の上部に形成された化合物半導体層の電子供給層5の上部に、ソース電極6とゲート電極7とドレイン電極8と絶縁膜9,10とを有する。ソース電極6、ゲート電極7、およびドレイン電極8と絶縁膜10との各接合界面には窒化物系の接合膜11a,11d,11cが形成され、ゲート電極7と絶縁膜9との接合界面には窒化物系の接合膜11bが形成される。接合膜11a,11d,11cは、ソース電極6、ゲート電極7、およびドレイン電極8と絶縁膜10とをそれぞれ接合する。接合膜11bは、ゲート電極7と絶縁膜9とを接合する。

(もっと読む)

半導体装置及びその製造方法

【課題】ボイドによるコンタクトホール間のショート不良を防止する半導体装置及びその製造方法を提供すること。

【解決手段】本発明の一形態の半導体装置は、半導体基板(101)上に形成された第1及び第2のMOSFETと、前記第1のMOSFET上に形成された第1の応力膜(110)と、前記第2のMOSFET上に形成されるとともに、前記第1の応力膜の端部に積層され、前記第1の応力膜の側面との間にボイド(V)を有するように形成された第2の応力膜(112)と、前記第1の応力膜及び前記第2の応力膜上に形成される絶縁膜と、を備え、前記第1の応力膜と前記第2の応力膜との境界部に、前記第1の応力膜と前記第2の応力膜のどちらにも覆われていない領域(A)を有し、前記領域及び前記ボイドの少なくとも一部に前記絶縁膜が埋め込まれている。

(もっと読む)

電子部品の製造方法

【目的】シード膜の溶解を抑制し、電解めっき後のめっき膜の未析や欠陥の発生を低減する方法を提供することを目的とする。

【構成】本発明の一態様の電子部品の製造方法は、基板上にシード膜を形成するシード膜形成工程(S110)と、前記シード膜を冷却する冷却工程(S112)と、冷却された前記シード膜をめっき液に浸漬させ、前記シード膜をカソードとして電解めっきを行なうめっき工程(S114)と、を備えたことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】低抵抗なコンタクトを歩留まり良く形成することができる半導体装置及びその製造方法を提供する。

【解決手段】ニッケルシリサイド層7が十分な膜厚を有する領域にコンタクトホール11を形成するとともに、金属シリサイド層7のエッチングを行い金属シリサイド層7に凹部を形成する。次いで、コンタクトホール11を所望のコンタクト径まで拡大する。これにより、コンタクトホールの底部を占めるシリサイド面積率を下げることなく、所望のコンタクトホール11のボトム面積を確保することができ、コンタクト抵抗上昇に起因する製造歩留まり低下を抑制することができる。

(もっと読む)

支持されたゲート電極を備えるトランジスタの作製方法およびそれに関連するデバイス

貫通する開口を備える保護層を基板上に形成し、さらにこの開口の中にゲート電極を形成することによって、トランジスタは作製される。ゲート電極の第1の部分は、開口の外側に存在する保護層の表面部分で横方向に延在し、ゲート電極の第2の部分は、保護層から間隔を空けて配置され、第1の部分を越えて横方向に延在する。関連したデバイスおよび作製方法も述べられる。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体装置の低抵抗化を図る。

【解決手段】 本発明の半導体装置は、N型の半導体基板1に形成されたエピタキシャル層2と、前記エピタキシャル層2に形成されたP型の不純物拡散層3と、前記不純物拡散層3の表層から前記エピタキシャル層2の所定深さ位置まで形成されたトレンチ溝4と、前記トレンチ溝4内に絶縁層5を介して導電層が埋設されて成るゲート電極6と、前記不純物拡散層3の表層で、かつ前記トレンチ溝4の両側壁部に前記絶縁層5に隣接して形成されたソース層7と、前記エピタキシャル層2の表層から前記半導体基板1を貫通するように貫通孔1Aが穿設され、この貫通孔1A内に貫通電極構造を成すように形成されたドレイン層9と、前記半導体基板1の裏面に形成され、前記ドレイン層9の底部と電気的に接続された金属層14とを具備したことを特徴とする

(もっと読む)

金属配線とその製造方法、薄膜トランジスタ、電気光学装置、及び電子機器

【課題】液相法を用いて形成され、さらに拡散による不都合を解消するとともに、平坦性をも有した金属配線とその製造方法、さらには拡散や平坦性の低下に起因する特性の低下を防止した薄膜トランジスタと、これを備えた電気光学装置、電子機器を提供する。

【解決手段】基板P上に液相法で形成された金属材料からなる主導電層66、67、81と、主導電層66、67、81上に液相法で形成されたキャップ層68a、82とを備えた金属配線34、35、80aである。キャップ層68a、82は、有機金属又は無機金属塩の溶液が主導電層66、67、81上に配され、焼成されたことによって形成されている。金属配線80aはボトムゲート型薄膜トランジスタ60のゲート電極となっている。

(もっと読む)

膜形成方法

【課題】 膜の内部応力を向上できる膜形成方法を提供する。

【解決手段】 この膜形成方法では、まず、基板2を第1の方向Z1に反らせる。次に、反った基板2上に膜4を形成する。次に、反った基板2を第1の方向Z1とは反対の第2の方向Z2に反らせる。

(もっと読む)

表示装置とその製造方法

【課題】TFT基板に形成する薄膜トランジスタのゲート絶縁膜を高誘電率材料を用いた厚膜とし、かつ十分なイオンをドーピングする。

【解決手段】膜厚が厚い高誘電率材料からなるゲート絶縁膜3にコンタクトホール7aを形成した後でイオンドーピングしてn+領域7を形成する。

(もっと読む)

半導体デバイス用の自己整合ショットキー接合の形成方法

半導体デバイスに対し、自己整合ショットキー接合(29)を形成する方法である。ゲートエッチング及びスペーサ形成の後、接合領域を画成する凹所を半導体基板(10)に形成し、そこに、SiGe層(22)を選択的に成長させる。その後、誘電体層(24)をゲート(14)及びSiGe層(22)の上に設け、コンタクトエッチングを行って、コンタクトホール(26)を形成してから、SiGeの材料(22)を除去して、接合領域にキャビティ(28)を作成する。最後に、キャビティ(28)を金属で満たして、接合(29)を形成する。このようにして、抵抗率が比較的低く、形状及び位置を良好に制御することができる、ショットキー接合を自己整合で形成する方法が提供される。  (もっと読む)

(もっと読む)

多層構造の形成方法

基板に電気化学エッチングまたは電気めっきを施すことにより多層構造を形成する方法。基板上にシード層を形成し、その上に主電極を形成する。主電極は、基板から複数の電気化学セルを形成するためのパターン層を有する。電圧が印加され、シード層がエッチングされて、またはシード層に材料がめっきされて形成された構造(8)の間に誘電体(9)が堆積される。誘電体層は下層構造を露出するために平坦化され、別の構造層が第1の構造層上に形成される。または、誘電体層は2層の厚さで形成され、下層構造の上端部を選択的に露出するために選択的にエッチングされる。また、複数の構造層を1工程で形成しても良い。 (もっと読む)

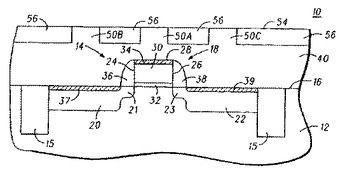

犠牲マスキング構造を用いた半導体装置の製造方法

犠牲マスキング構造(50)を用いた半導体装置(10)の製造方法を提供する。半導体デバイスは半導体基板(12)から形成され、誘電材料からなる層(40)は半導体基板(40)および半導体デバイスの上に形成される。誘電材料からなる層(40)は、半導体基板(12)上に直接に形成される場合もあれば、中間層によって半導体基板(12)から間隔があいている場合もある。側壁を有するポストまたは凸部(50)が、誘電材料からなる層(40)から形成される。好ましくは誘電材料からなる層(40)とは異なる電気絶縁材料(52)がポスト(50)の側壁に隣接して形成される。電気絶縁材料(52)は平坦化され、ポスト(50)が除去されて、半導体デバイスの一部または中間層材料の一部を露出させ得る開口を形成する。導電性材料が開口に形成される。  (もっと読む)

(もっと読む)

逆ソース/ドレイン金属コンタクトを有する電界効果トランジスタ(FET)及びその製造方法

【課題】 コンタクト間隔及び寄生容量の問題に対する解決策を提供する、改善されたFET設計を構築する。

【解決手段】 本発明は、下方の第1の誘電体層内に配置された下部と上方の第2の誘電体層内に配置された上部とを有する逆ソース/ドレイン金属コンタクトを含む電界効果トランジスタ(FET)に関する。逆ソース/ドレイン金属コンタクトの下部は、上部より大きい断面積を有する。好ましくは、逆ソース/ドレイン金属コンタクトの下部は、約0.03μm2から約3.15μm2の範囲の断面積を有し、こうした逆ソース/ドレイン金属コンタクトは、約0.001μmから約5μmの範囲の距離だけ、FETのゲート電極から間隔を空けて配置される。

(もっと読む)

画素電極形成方法、デバイス製造方法及び電気光学装置並びに電子機器

【課題】画素の表示特性の低下を防止する。

【解決手段】基板P上に画素電極形成材料を含む液滴を吐出して画素電極45を形成す

る。基板P上に隔壁形成材料の薄膜を形成する工程と、薄膜の表面に撥液処理を施す工程

と、撥液処理が施された薄膜をパターニングして、画素電極45の形状に応じた隔壁61

を形成する工程と、隔壁61の間の凹部に液滴を吐出する工程とを有する。

(もっと読む)

膜パターンの形成方法、デバイスの製造方法、デバイス、電気光学装置、及び電子機器

【課題】基板に対する膜パターンの密着力を向上し、膜パターンを良好に形成することが

できる膜パターンの形成方法を提供する。

【解決手段】機能液を基板上に供給して膜パターンを形成する際、基板と膜パターンとの

密着力を向上させるための中間層を基板上に形成する工程と、中間層上に機能液を供給す

ることによって膜パターンを形成する工程とを経て形成する。中間層はシロキサン結合を

主鎖とした無機材料を含む。

(もっと読む)

膜パターンの形成方法、デバイスの製造方法、デバイス、電気光学装置、及び電子機器

【課題】所望位置に所望状態で機能液を供給し、膜パターンを良好に形成することができ

る膜パターンの形成方法を提供する。

【解決手段】機能液を基板上に供給して膜パターンを形成する際、基板上にバンクを形成

するための感光材を塗布する工程と、膜パターンに応じて感光材を露光する工程と、露光

された感光材を現像してバンクを形成する工程と、現像により形成されたバンクの上面を

撥液性にする工程と、バンクによって区画された領域に機能液を供給する工程と、バンク

を焼成する工程とを経て形成する。現像し、バンクの上面を撥液性にした後、焼成する前

に、機能液を供給する動作が行われる。

(もっと読む)

半導体装置およびその製造方法

【課題】 金属材料からなるゲート電極を有するnチャネル型MISトランジスタおよびpチャネル型MISトランジスタの製造工程を簡略化する。

【解決手段】 ゲート絶縁膜5上に堆積したルテニウム膜をパターニングすることによって、nチャネル型MISトランジスタおよびpチャネル型MISトランジスタのそれぞれのゲート電極を同時に形成する。次に、それぞれのゲート電極に酸素を導入することによって、仕事関数が大きいゲート電極6Aに変換する。その後、nチャネル型MISトランジスタのゲート電極6Aを水素アニールで選択的に還元することによって、仕事関数の小さいゲート電極6Bに変換する。

(もっと読む)

微小電気機械式装置の作製方法

【課題】微小構造を有するマイクロマシンの量産に際して、微小構造体と微小構造体を制御する半導体素子を同一基板上に形成し、コストを低減する方法を提供する。

【解決手段】マイクロマシンの作製に際して、膜のパターン形成を行うためのマスク材料を用いて犠牲層を形成し、半導体素子を形成する領域におけるマスクの除去と、微小構造体を形成する領域における犠牲層とマスクの除去を同一の工程にて行う。具体的には絶縁性基板上に選択的に犠牲層103を形成し、犠牲層を覆って半導体層104を形成し、半導体層上にマスク105を形成し、マスクを用いて半導体層をエッチングし、マスク及び犠牲層の除去を同時に行う微小電気機械式装置の作製方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置のより微細化に適し、しかも低コストである半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体シリコン基板表面上に形成されたポリシリコン膜からなるゲート電極構造とこれを覆う層間絶縁膜を有する半導体装置の製造方法において、層間絶縁膜形成後、層間絶縁膜を貫いてコンタクトホールを開口させて所望のコンタクト面を露出させる工程、少なくともコンタクトホール側壁部及びコンタクト面上に絶縁膜を堆積させる工程、絶縁膜をエッチバックすることによりコンタクトホール側壁部にサイドウォール状絶縁膜を形成することを特徴とする半導体装置の製造方法を提供する。

(もっと読む)

高性能の有機デバイス製造用レーザアブレーション法

レーザアブレーション法を利用して有機トランジスタのチャンネル長を画定する。基板を金属堆積あるいは導電性ポリマー堆積でコーティングして、レーザアブレーションにより達成可能な分解能を向上させるべく薄膜に適用する。レーザアブレーション法はロール毎のプロセスに利用でき、プリント電子技術を生成するのに適当な速度、量、価格、分解能を達成する。 (もっと読む)

161 - 180 / 226

[ Back to top ]