Fターム[4M104DD15]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744)

Fターム[4M104DD15]の下位に属するFターム

Fターム[4M104DD15]に分類される特許

61 - 80 / 226

半導体装置の作製方法

【課題】電気的特性が向上した、酸化物半導体を用いた半導体装置の作製方法を提供することを目的の一とする。

【解決手段】酸化物半導体膜と、酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有する半導体装置の作製方法であって、酸化物半導体膜上に接して、酸化ガリウムを含む第1の絶縁膜を形成し、第1の絶縁膜上に接して第2の絶縁膜を形成し、第2の絶縁膜上にレジストマスクを形成し、第1の絶縁膜および第2の絶縁膜にドライエッチングを行ってコンタクトホールを形成し、レジストマスクを、酸素プラズマによるアッシングを用いて除去し、コンタクトホールを介して、ゲート電極、ソース電極またはドレイン電極のいずれか一または複数と電気的に接続される配線を形成する、半導体装置の作製方法である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート−ソース間の容量低減及びソース抵抗を低減させ、且つ耐圧向上、高出力化及び高周波化を、容易且つ確実に可能とする量産化に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極19を形成する際に、4層の電子線レジスト11〜14を用いてゲート開口17を形成し、ゲート開口17内に、キャップ層5の表面との接触面を含む幹状の下方部分19aと下方部分19aから傘状に拡がる上方部分19bとが一体形成されてなり、下方部分19aの接触面がドレイン電極7に比べてソース電極6に偏倚した位置に設けられており、上方部分19bの傘状の下端面のうちソース電極6側の部位がドレイン電極7側の部位よりもキャップ層5の表面からの高さが高いゲート電極19を形成する。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38及びソース電極34はドレイン電極36を囲み、ソース電極34の上部に、ゲート電極38の上方を通過してドレイン電極36側に庇状に突き出したフィールドプレート170が形成され、GaN系エピタキシャル基板32の表面層とフィールドプレート170との間に、誘電体膜46が形成され、誘電体膜46は、フィールドプレート170の直下領域においてフィールドプレート終端面と面一状態となるように切れ込み、その下端からドレイン電極36に接続するようにドレイン電極36に向かって延びている。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38の上部に、ドレイン電極36側及びソース電極34側に庇状に突き出したフィールドプレート40が形成され、基板32の表面層とフィールドプレート40との間に誘電体膜46が形成され、誘電体膜46は、フィールドプレート40のドレイン電極36側及びソース電極34側の終端面と面一状態となるように切れ込み、ドレイン電極36側の下端からドレイン電極36に接続するようにドレイン電極36に向かって延びており、且つ、ソース電極34側の下端からソース電極34に接続するようにソース電極34に向かって延びている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

整流器ブリッジ回路

【課題】本発明の課題は、ロードダンプの場合、すなわち負荷の遮断の急に行われる場合にも、ロードダンプエネルギが全てのダイオードに均等に分配される整流器ブリッジ回路を提供することである。

【解決手段】前記課題は、請求項1に従う整流器ブリッジ回路によって解決される。

(もっと読む)

半導体装置の製造方法

【課題】デュアルゲート構造を有する半導体装置の製造技術において、MISFETのしきい値電圧の上昇を抑制することができる製造技術を提供する。

【解決手段】ポリシリコン膜PF1上にレジスト膜FR2を形成する。そして、レジスト膜FR2に対して露光・現像処理を施すことにより、レジスト膜FR2をパターニングする。その後、パターニングしたレジスト膜FR2をマスクにしたイオン注入法により、露出しているnチャネル型MISFET形成領域NTRのポリシリコン膜PF1にアルゴン(Ar+)を導入する。このアルゴン注入工程により、nチャネル型MISFET形成領域NTRのポリシリコン膜PF1はアモルファス化する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】ゲート電極の形成工程におけるフォトレジスト層を露光した際に、露光不良によりレジスト残渣が発生しないようにすること。

【解決手段】本発明の電界効果トランジスタ100は、半導体基板1上にゲート電極を備えた電界効果トランジスタで、半導体基板1上に設けられた誘電体膜2と、この誘電体膜2の開口部に設けられたフット部8と、このフット部8上及び誘電体膜2上に設けられたヘッド部9とを備え、誘電体膜の膜厚t1が、0.9k×λ/2|n1−n2|<t1<1.1k×λ/2|n1−n2|(ただしkは自然数であり、屈折率n1は所定の波長λを有する露光光に対する誘電体膜の屈折率n1(>2.1)、屈折率n2はフォトレジスト層の屈折率)である。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と第1のコンタクトプラグとが接触する接触幅を充分に確保する。

【解決手段】半導体基板10の上に、エッチングストッパー膜17、第1の層間絶縁膜18及び第2の層間絶縁膜19を順次形成する。次に、第1,第2の層間絶縁膜18,19を貫通し、且つ、エッチングストッパー膜17を露出する第1のホール23を形成する。次に、酸素ガスを含むプラズマを用いたプラズマ処理により、第2の層間絶縁膜19における第1のホール23の側壁に露出する部分を変質して、第1の変質層25を形成する。次に、第1の変質層25を除去して、第2のホール27を形成する。次に、エッチングストッパー膜17における第2のホール27に露出する部分を除去して、第1のコンタクトホール29を形成する。次に、第1のコンタクトホール29に、第1のコンタクトプラグ32Aを形成する。

(もっと読む)

半導体装置の製造方法

【課題】ボイド、ディッシング、及びエロージョンの発生を抑制することのできる半導体装置の製造方法を提供する。

【解決手段】絶縁膜に幅の異なる複数の開口部36,37を形成し、次いで、絶縁膜の上面、及び幅の異なる複数の開口部内にシード層38を形成し、次いで、第1の成長速度により、シード層の表面を覆う第1のめっき膜71を形成し、次いで、第1の成長速度よりも速く、かつボイドを生じさせない第2の成長速度により、第1のめっき膜の表面に第2のめっき膜72を形成し、次いで、第2の成長速度よりも速い第3の成長速度により、第2のめっき膜上に第3のめっき膜73を形成し、その後、シード層及び第1乃至第3のめっき膜のうち、絶縁膜の上面よりも上方に形成された部分を研磨により除去することで、開口部内に少なくとも第1及び第2のめっき膜よりなる導電部を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

窒化物半導体装置

【課題】GaN系の窒化物半導体を用いたデバイスのゲートリセス量の制御性を向上することで、閾値電圧の面内均一性を向上することができる窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、基板101上に形成された第1のGaN系半導体からなるバッファ層102と、第2のGaN系半導体からなるキャリア走行層103と、第3のGaN系半導体からなるキャリア供給層104とを備えている。キャリア供給層104の上には第1の絶縁膜105と、アルミニウムを含む第2の絶縁膜106と、第1の絶縁膜105より膜厚が厚い第3の絶縁膜107とが形成されている。ソース電極108及びドレイン電極109は第1の絶縁膜105上に形成されている。ゲート電極110は、リセス構造を含む第2の絶縁膜106及び第3の絶縁膜107上に形成されている。

(もっと読む)

電子デバイス及びオーミック電極形成方法

【課題】製造工程において高温で短時間のアニールを可能にすることにより、イオン注入の工程が不要なAlxGa1−xN/AlyGa1−yNヘテロ接合のオーミック電極を備える電子デバイスを提供する。

【解決手段】

電子デバイスは、ワイドバンドギャップ化合物半導体層と、前記ワイドバンドギャップ化合物半導体層上に形成されるオーミック電極とを含む電子デバイスであって、前記ワイドバンドギャップ化合物半導体層は、IniAljGakN(i+j+k=1,0≦i≦1,0<j≦1,0≦k<1)からなる化合物半導体バリア層とAlyGa1−yN(0<y≦1)からなる化合物半導体チャネル層からなり、前記オーミック電極は、前記化合物半導体バリア層上に密着層が積層され、前記密着層上にオーミック層が積層されて形成された電極であり、前記密着層はZrからなるようにする。

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

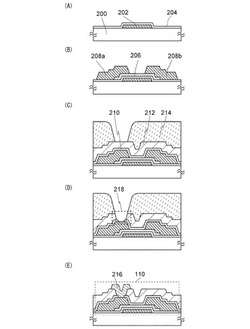

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

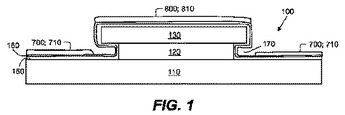

表示装置、表示装置の製造方法および電子機器

【課題】製造工程を簡略化することが可能な表示装置の製造方法を提供する。

【解決手段】表示装置1は次のようにして製造する。まず、基板10上に、ゲート電極層11、ゲート絶縁膜12および半導体層13を順に形成した後、領域10A,10Bに渡りソース・ドレイン電極層15を形成する。ソース・ドレイン電極層15が、電極層15aと上部金属層15bとを有することにより、その後の工程で、画素間絶縁膜17をパターニング形成する際、電極層15aが損傷を受けずに済む。画素間絶縁膜17の形成後、領域10Aにおいて、ソース・ドレイン電極層15のうち上部金属層15bを選択的に除去することにより、電極層15aの表面を露出させる。この露出した電極層15a上に有機層18およびカソード電極19を形成することで、領域10Aに、ソース・ドレイン電極層15(電極層15a)をアノード電極として用いた有機発光素子1aを形成する。

(もっと読む)

マスクの製造方法、及び半導体装置の製造方法

【課題】開孔径が均一で開孔径の制御が容易な、微細化に適した開孔パターンを有するマスクを製造する。

【解決手段】第1及び第2のマスク層内に開孔を設ける。この後、第1のマスク層内の開孔の径よりも第2のマスク層内の開孔の径を、Xの量だけ大きくする。この後、第2のマスク層内の開孔内にマスク材料を形成することによって第2のマスク層内の開孔内に、Xの径の空洞部を形成する。この空洞部を開孔として有する第2のマスク層及びマスク材料を、マスクとして形成する。

(もっと読む)

61 - 80 / 226

[ Back to top ]