Fターム[4M104DD22]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 表面処理 (1,044)

Fターム[4M104DD22]の下位に属するFターム

Fターム[4M104DD22]に分類される特許

201 - 220 / 634

表示装置およびこれに用いるCu合金膜

【課題】Cu系材料の特徴である低電気抵抗を維持しつつ、ガラス基板との密着性に優れた、表示装置用Cu合金膜を提供する。

【解決手段】基板上にて、ガラス基板と直接接触する表示装置用Cu合金膜であって、該Cu合金膜は、Ti、AlおよびMgよりなる群から選択される1種以上を合計で0.1〜10.0原子%含有することを特徴とする。本発明は、前記表示装置用Cu合金膜が薄膜トランジスタに用いられている点に特徴を有する表示装置も含むものである。該表示装置としては、該薄膜トランジスタがボトムゲート型構造を有するものであって、前記表示装置用Cu合金膜が、該薄膜トランジスタのゲート電極および走査線に用いられ、ガラス基板に直接接触されている態様が好ましい。

(もっと読む)

有機薄膜トランジスタの製造方法、有機薄膜トランジスタ素子及び表示装置

【課題】1回のインクジェット吐出により基板上に、分離された複数の薄膜を成膜可能な有機薄膜トランジスタの製造方法を提供し、該製造方法によりOff電流が低く、且つ、平均移動度が良好な有機薄膜トランジスタを提供し、且つ、該トランジスタを具備する表示装置を提供する。

【解決手段】基板上に、導電層、絶縁層、有機半導体層の少なくとも一層をインクジェットプロセスで成膜する工程を有する有機薄膜トランジスタの製造方法において、

該導電層、該絶縁層及び該有機半導体層の少なくとも一層を成膜する際、1回のインクジェット吐出によって、該基板上に、分離された複数の薄膜を成膜する工程を有することを特徴とする有機薄膜トランジスタの製造方法。

(もっと読む)

銅配線基板の製造方法

【課題】 電気抵抗のさらなる低減化と基板表面に対する銅薄膜の密着性の確保との両方を高いレベルで達成することができ、かつスパッタリングプロセスで用いられる金属ターゲット材のコスト削減やそれを用いたスパッタリングプロセスを中心として全体的な製造プロセスのコスト低減を達成することを可能とした、銅配線基板の製造方法を提供する。

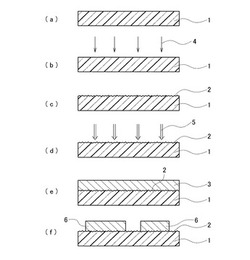

【解決手段】 本発明の銅配線基板の製造方法は、ガラスまたは石英からなる基板1の表面2に、例えばArガスのような不活性ガスのプラズマ4を照射することで、その表面2に改質を施して、その基板1の表面2自体における純Cuに対する密着性を向上させ、その基板1の表面2の直上に、銅薄膜3をスパッタリングによって形成することを特徴としている。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム系の化合物半導体層のN原子面上に比較的簡単に低抵抗な電極を形成することが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】ショットキーバリアダイオード1は、導電型がn型であるGaN基板2およびn−GaNエピタキシャル層3と、オーミック電極6とを備える。オーミック電極6はGaN基板2のN原子面9に接触して形成される。オーミック電極6においてN原子面9に接している接触電極層6aの主成分はNi、Au、Pd、Mo、Ru、Te、Rh、Co、Re、Os、Ir、Ptからなる群から選択される1つである。

(もっと読む)

ショットキーバリアダイオード

【課題】 フィールドプレート構造により逆方向耐電圧の向上したショットキーバリアダイオードを提供する。

【解決手段】 主表面を有する窒化ガリウム系化合物のエピタキシャル層と、 前記主表面上に形成され、開口部が形成されている窒化絶縁層と、前記開口部の内部に、前記主表面に接触するように形成されたショットキー電極と、前記ショットキー電極に電気的に接続するとともに、前記窒化絶縁層に重なるように形成された、フィールドプレート電極と、を備え、前記窒化絶縁層と前記エピタキシャル層との界面での固定電荷密度が、1.2×1012cm−2未満である。

(もっと読む)

有機トランジスタ及び有機トランジスタの製造方法

【課題】製造コストの低い溶液法を使用でき、さらに、有機半導体層への影響が少なく機械的強度や熱的安定性に優れた電極を備える有機トランジスタを提供する。

【解決手段】有機半導体層14と、有機半導体層14にゲート絶縁層13を介して形成されたゲート電極12と、有機半導体層14に接して対向する位置に形成されている炭素材料からなるソース電極15及びドレイン電極16とを備える有機トランジスタを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートオーバーラップ幅が小さく高速応答が可能で低消費電力のTFTを低コストで実現することができる半導体装置及びその製造方法を提供する。

【解決手段】基板11上に形成されるゲート電極12と、ゲート電極12を覆うように形成されるゲート絶縁膜13と、基板11上であってゲート電極12の近傍にめっきにより形成されるソース電極14と、基板11上であってゲート電極12の近傍に、ソース電極14とゲート電極12を挟んで反対側に位置するようにめっきにより形成されるドレイン電極15と、ソース電極14、ドレイン電極15及びゲート絶縁膜13を覆うように形成される半導体膜16とを有する半導体装置10において、基板11は、めっき触媒を含有し、ソース電極14及びドレイン電極15は、めっき触媒に直接接触して形成されていることを特徴とする半導体装置10。

(もっと読む)

半導体装置の製造方法

【課題】接合リーク電流の低減が図られる半導体装置の製造方法を提供する。

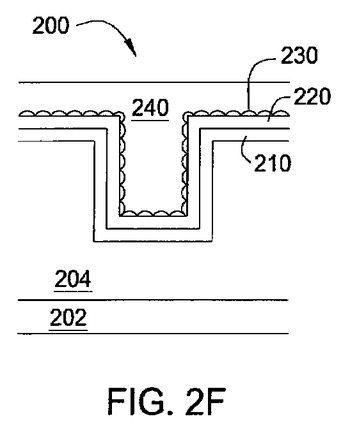

【解決手段】半導体基板1に所定の深さのトレンチが形成され、そのトレンチ5内に分離酸化膜6が形成される。不純物イオンを注入することにより、分離酸化膜6の表面に、分離酸化膜6のエッチング特性とは異なるエッチング特性を有する改質層7が形成される。半導体基板の領域に、トランジスタ等の所定の半導体素子が形成される。半導体基板1上に、エッチングストッパ膜10および層間絶縁膜16が形成される。その層間絶縁膜16およびエッチングストッパ膜に、金属シリサイド9の表面を露出するコンタクトホール16a,16bが形成される。コンタクトホール16a,16b内にプラグ18a,18bが形成される。

(もっと読む)

積層構造体、多層配線基板、アクティブマトリックス基板、画像表示装置及び積層構造体の製造方法

【課題】インクジェットにより短時間に配線の形成が可能な積層構造体を提供する。

【解決手段】基板と、基板上において、高表面エネルギー領域と、低表面エネルギー領域とが形成されている濡れ性変化層と、濡れ性変化層の高表面エネルギー領域上において導電性材料により形成された導電層とを有し、導電層は、インクジェットヘッドにより導電性材料を含む液体を吐出することにより形成されるものであって、インクジェットヘッドの副走査方向に延びたパターンの導電層となる高表面エネルギー領域には、前記インクジェットヘッドの主走査方向に延設された高表面エネルギー領域の液滴供給領域が形成されていることを特徴とする積層構造体を提供することにより上記課題を解決する。

(もっと読む)

障壁表面上のコバルト堆積

本発明の実施形態は、障壁層上にコバルト層を堆積させた後、コバルト層上に銅または銅合金などの導電材料を堆積させるプロセスを提供する。一実施形態では、基板表面上に材料を堆積させる方法であって、基板上に障壁層を形成するステップと、気相成長プロセス(たとえば、CVDまたはALD)中に基板をジコバルトヘキサカルボニルブチルアセチレン(CCTBA)および水素に露出させて障壁層上にコバルト層を形成するステップと、コバルト層を覆うように導電材料を堆積させるステップとを含む方法が提供される。いくつかの例では、障壁層および/またはコバルト層は、熱プロセス、インサイチュプラズマプロセス、または遠隔プラズマプロセスなどの処理プロセス中にガスまたは試薬に露出させることができる。  (もっと読む)

(もっと読む)

無電解めっき方法および無電解めっき装置

【課題】触媒付与処理を行った後、配線表面における異状粒状金属の発生及び配線表面のめっき膜のラフネス悪化を防止しつつ、コバルト合金膜等のめっき膜を配線の表面に選択的に形成できるようにする。

【解決手段】絶縁膜に設けた配線用凹部内に金属を埋込んで形成した埋込み配線を有する基板を用意し、基板表面を触媒付与液に接触させて配線表面に触媒を付与し、触媒付与後の基板表面に洗浄液を供給しつつ該表面を物理的に洗浄し、しかる後、基板表面に無電解めっきを行って配線表面にめっき膜を選択的に形成する。

(もっと読む)

C12A7エレクトライドからなる導電性素子材料表面に対するオーミック接合形成方法

【課題】冷電子放出源や有機EL等の素子へC12A7エレクトライドを応用するために

、大気中でも界面が劣化することが少ない、オーミック表面を形成すること。

【解決手段】12CaO・7Al2O3エレクトライドを導電性素子材料として、その表

面に金属を蒸着してオーミック接合を形成する方法において、該素子材料表面をリン酸処

理して改質した後、該素子材料表面に金属を蒸着することによって、該素子材料表面と該

金属との界面の接触抵抗を0.5Ω・cm2未満とすることを特徴とするC12A7エレ

クトライドからなる導電性素子材料表面に対するオーミック接合形成方法。

(もっと読む)

電解処理装置及び電解処理方法

【課題】例えばルテニウム膜をシード層として該ルテニウム膜の表面にダイレクトめっきを行うのに先立って、たとえ300mmウェーハ等の大型の高抵抗基板であっても、ルテニウム膜表面の不動態層を確実に除去することで、その後のめっき時におけるターミナルエフェクトを改善し、しかも、めっき膜の膜質を改善し、微細配線パターンの内部にボイドのないめっき膜を埋込むことができる電解処理装置及び電解方法を提供する。

【解決手段】貴金属または高融点金属からなるシード層を有する基板Wの該シード層と対向する位置に配置されるアノード52と、電解液62で満たされた基板Wとアノード52との間に、内部に電解液を含浸させて配置される多孔質体46と、シード層表面の電場を制御してシード層表面に形成された不動態層を電解処理により電気化学的に除去する制御部58を有する。

(もっと読む)

積層構造体、多層配線基板、アクティブマトリックス基板、画像表示装置及び積層構造体の製造方法

【課題】インクジェット方式により緻密な配線の形成される積層構造体を提供する。

【解決手段】基板と、基板上において、エネルギーを付与することにより臨界表面張力が変化し、低表面エネルギー状態から高表面エネルギー状態へと変化する材料を含むものであって、エネルギーの付与により、高表面エネルギー領域と、低表面エネルギー領域とが形成されている濡れ性変化層と、濡れ性変化層の高表面エネルギー領域上に導電性材料により形成された導電層と、を有し、高表面エネルギー領域は、導電層による電気配線が形成される第1の領域と、第1の領域と接続されており、第1の領域よりも幅が狭く、第1の領域に導電材料を含む溶液を供給するための第2の領域とにより構成されていることを特徴とする積層構造体を提供することにより上記課題を解決する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】オーミック接触と、低い接触抵抗と、密着強度の大きい表面を有するNiシリサイド膜をアニールなしに形成することのできる炭化珪素半導体装置の製造方法の提供。

【解決手段】SiC基板1を真空中で最表面から所定の深さまでエッチングし、続いて、組成をNixSi1−xで表した場合、0.3<x<0.7となるようなNiとSiの比率で、NiとSiを前記SiC基板1のエッチング面上に堆積してNiシリサイド膜5を成膜する工程を有する炭化珪素半導体装置の製造方法とする。

(もっと読む)

導体または半導体基板上に堆積させたカーボンナノチューブマットの製造方法

【課題】酸化層の前堆積を行うことなく、導体または半導体材料上に高密度のカーボンナノチューブマットを製造する方法を提供する。

【解決手段】拡散バリア520、拡散バリア上にアモルファスシリコン層530、アモルファスシリコン層上に金属層を含む触媒複合体を導体または半導体基板510上に堆積させる。次いで前記金属層に酸化処理を行い、最後に、酸化処理された金属層からカーボンナノチューブマット580を成長させる。

(もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】多層配線構造における硼窒化ジルコニウム膜と下地膜との間の密着性を向上させることにより半導体装置の信頼性を向上させた半導体装置の製造装置及び半導体装置の製造方法を提供する。

【解決手段】第1メタルキャップ膜MC1と第2メタルキャップ膜MC2とが成膜される際に、まず基板Sの表面に水素ラジカルが供給されて、表面処理である微粒子のエッチング処理や未結合手への末端処理、さらには酸化層の還元処理が実行される。そして、この表面処理が基板Sに施された後、基板Sの表面にZr(BH4)4と励起状態の窒素とが供給されて、第1メタルキャップ膜MC1及び第2メタルキャップ膜MC2である硼窒化ジルコニウム膜が成膜される。

(もっと読む)

半導体装置の製造方法

【目的】膜切れの無い均一なシード膜を形成する半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S102)と、絶縁膜に開口部を形成する工程(S104)と、開口部内に光触媒膜を形成する工程(S110)と、Cuを含有する溶液に光触媒膜を浸漬させた状態で光触媒膜に紫外線を照射する工程(S112)と、開口部内に電解めっき法によりCuを埋め込む工程(S114)と、を備えたことを特徴とする。

(もっと読む)

凹状のドレイン及びソース区域並びに非共形的な金属シリサイド領域を有するMOSトランジスタを備えたCMOSデバイス

【解決手段】

凹状のドレイン及びソース構造のトランジスタ(150)における非共形的金属シリサイド層(156)は、歪誘起メカニズム、ドレイン/ソース抵抗等に関して高い性能を提供することができる。このために場合によっては、シリサイド化プロセスに先立ちアモルファス化注入プロセスが実行されてよい一方で、他の場合には高融点金属(156)の異方的な堆積が用いられてよい。

(もっと読む)

カーボンナノチューブを利用した半導体素子の配線形成方法およびその方法により製造された半導体素子

【課題】高い電流密度を持つカーボンナノチューブを利用した半導体素子の配線形成方法、およびその方法により製造される超高集積度の半導体素子を提供する。

【解決手段】半導体素子の電極120表面を前処理して活性化させる段階と、電極の活性化した表面122上に絶縁層130を形成した後、電極の活性化した表面の一部を露出させるために絶縁層を貫通するコンタクトホール132を形成する段階と、コンタクトホールを通じて電極の活性化した表面に炭素が含まれているガスを供給して前記電極の活性化した表面からカーボンナノチューブ140を成長させて配線を形成する段階と、を具備する半導体素子の配線形成方法およびその方法により製造された半導体素子。

(もっと読む)

201 - 220 / 634

[ Back to top ]