Fターム[4M104DD26]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098) | 基板への不純物導入 (557)

Fターム[4M104DD26]に分類される特許

41 - 60 / 557

炭化珪素半導体装置の製造方法

【課題】 実施形態は、低損失な炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】 実施形態の炭化珪素半導体装置の製造方法は、炭化珪素基板にイオン注入する工程と、前記イオン注入がされた炭化珪素基板に第1の熱処理を行う工程と、前記第1の熱処理がされた炭化珪素基板に前記第1の熱処理より低温の第2の熱処理を行う工程と、を有することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

半導体素子及びその製造方法

【課題】 この実施の形態は、SiC半導体基板上に形成されたn型半導体領域とp型半導体領域を形成した半導体装置において、n型半導体領域とp型半導体領域の両領域にまたがって、単一の金属電極用いて同時コンタクトを形成することを目的としている。

【解決手段】 この実施の形態の半導体装置は、導電性材料を用いた第1の電極240に、導電型がp型の第1の炭化珪素(SiC)半導体部220と、導電型がn型の第2のSiC半導体部230とが接続され、前記第1の電極と前記第1の界面部において炭素(C)の面密度がピークになるようしている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SiC基板を用いて形成され、金属シリサイド膜と金属電極との密着性の向上する半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、炭化珪素と、炭化珪素上に形成され、第1の層、第1の層よりも低い炭素比率を有する第2の層を備える金属シリサイドと、金属シリサイド上に形成される金属電極を備え、第2の層が第1の層上に形成され、第2の層が金属電極に接し、第2の層中の金属シリサイドの平均粒径が、第1の層中の金属シリサイドの平均粒径よりも大きい。

(もっと読む)

半導体装置及びその製造方法

【課題】高い逆方向耐圧VR及び低いリーク電流IRを維持したまま、順方向降下電圧VFを低くしたり、逆回復時間trrを短くしたりすることが可能な半導体装置を提供する。

【解決手段】n+型半導体層112とn−型半導体層114とを有する半導体基体110と、n−型半導体層114の表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114及びp+型拡散領域120の表面上に形成され、n−型半導体層114との間でショットキー接合を形成し、p+型拡散領域120との間でオーミック接合を形成するバリアメタル層130とを備える半導体装置であって、半導体基体110には、n−型半導体層114の表面で濃度が最も高くなるように重金属としての白金が拡散されている。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能および製造安定性を向上させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、第1の面および第2の面を有する有機半導体部と、第1の面に隣接されたソース電極部と、第2の面に隣接されたドレイン電極部とを備える。ソース電極部およびドレイン電極部のうちの少なくとも一方は、有機半導体部よりも高導電性の有機半導体材料を含む高導電性電極部である。

(もっと読む)

半導体素子のための非活性化保護リング

【課題】半導体素子、特にショットキーダイオードのような金属対半導体整流接合を組み込む半導体素子を提供する。

【解決手段】保護リングは、ショットキー接合又はショットキーダイオードの一部である半導体領域に形成される。保護リングは、高抵抗領域を形成するために、半導体コンタクト層を完全にアニール処理することなく半導体コンタクト層内へのイオン注入によって形成される。保護リングは、層のエッジ部か又は代替的に層のエッジ部からある一定距離を離して位置することができる。ショットキー金属接点は、層の上に形成され、ショットキー接点のエッジ部は、保護リングの上に配置される。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

半導体デバイス及びその製造方法

【課題】接合障壁ショットキーダイオード及びその製造方法を提供すること。

【解決手段】第1の導電型を有する半導体層と、この半導体層上にあり、半導体層と共にショットキー接合部を形成する金属接点と、半導体層内に半導体領域とを含んでいる。半導体領域と半導体層とが、第1のp−n接合部を、ショットキー接合部と並列に形成する。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、ショットキー接合部に隣接する半導体層内に空乏領域を発生させるように構成され、それによってショットキー接合部を通る逆漏れ電流が制限される。第1のp−n接合部は、ショットキー接合部に逆バイアスがかけられたとき、第1のp−n接合部のパンチスルーが、ショットキー接合部の降伏電圧よりも低い電圧で起こるように構成される。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置およびその製造方法

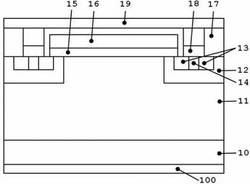

【課題】互いに隣接する2つの半導体層どうしの境界部分において、電界集中を緩和し、絶縁耐圧を改善することが可能な半導体装置およびその製造方法を提供する。

【解決手段】第1半導体層11の露出面11a、第2半導体層12の一面12a、および第3半導体層13A,13Bの表面13Aa,13Baの互いの境界で段差が実質的に無くなるように形成することで、露出面11a、一面12a、および表面13Aa,13Baからなる平面Q上に、段差無く平坦なゲート酸化膜16が形成できる。

これにより、ゲート酸化膜16の特定部分に電界が集中し、ゲート絶縁耐圧の低下などゲート酸化膜16の機能を大きく損なうことがない。

(もっと読む)

ジャンクションバリアショットキーダイオード

【課題】ジャンクションバリアショットキーダイオードの耐圧を低下させることなく、リーク電流の低減とオン電流の増大を両立したダイオードを提供する。

【解決手段】本発明は、ジャンクションバリアショットキーダイオードにおいて、pn接合を形成するp型領域の側部に存在するpn接合の傾きが、当該p型領域の底部に存在するpn接合の傾きより急峻である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

41 - 60 / 557

[ Back to top ]