Fターム[4M104DD34]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | 蒸着 (925)

Fターム[4M104DD34]に分類される特許

141 - 160 / 925

ショットキーバリアダイオード及びその製造方法

【課題】バリア金属層に電極金属層からの引っ張り応力等の応力が作用した場合においても、この応力がバリア金属層に局部的に集中するのを緩和することができ、逆方向電流(IR)を小さくすることができるショットキーバリアダイオード及びその製造方法を提供する。

【解決手段】本発明のショットキーバリアダイオード(SBD)11は、シリコン基板2の表面2aにトレンチ3が形成され、このトレンチ3の内面に絶縁膜12が形成され、この絶縁膜12が形成されたトレンチ3内に導電体13が埋め込まれ、シリコン基板2、絶縁膜12及び導電体13を覆うようにバリア金属層14が形成され、バリア金属層14のうち導電体13の凹面13aの周縁部近傍上の領域に緩衝層15が形成されている。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおいて、フィールドプレート終端での高電界の集中を緩和し、もって高耐圧半導体装置として利用可能とする。

【解決手段】本電界効果トランジスタ30は、GaN系エピタキシャル基板32の電子走行層上に、ゲート電極38を挟んで配置されたソース電極34及びドレイン電極36を備え、ゲート電極38及びソース電極34はドレイン電極36を囲み、ソース電極34の上部に、ゲート電極38の上方を通過してドレイン電極36側に庇状に突き出したフィールドプレート170が形成され、GaN系エピタキシャル基板32の表面層とフィールドプレート170との間に、誘電体膜46が形成され、誘電体膜46は、フィールドプレート170の直下領域においてフィールドプレート終端面と面一状態となるように切れ込み、その下端からドレイン電極36に接続するようにドレイン電極36に向かって延びている。

(もっと読む)

パターン形成方法および積層構造体

【課題】所望のパターンが形成でき、製造工程の迅速化を図ることが可能なパターン形成方法を提供する。

【解決手段】本実施形態のパターン形成方法は、下地10の上に第1の膜11を選択的に形成する工程と、前記第1の膜11および前記第1の膜に覆われていない前記下地10の上に、第2の膜13を形成する工程と、前記第2の膜13の平均結晶粒径を前記第2の膜13の膜厚以上に調整する工程と、前記第1の膜11のエッチャントを前記第2の膜13の表面に晒し、前記第1の膜11の上に形成された前記第2の膜13を前記下地上から選択的に除去する工程と、を備える。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

半導体装置

【課題】 表面保護膜中へのホットキャリアの侵入に起因する半導体装置の出力低下を抑制すること。

【解決手段】 本半導体装置100は、窒化ガリウム系半導体からなる電子走行層12と、電子走行層12上に設けられ、窒化ガリウム系半導体からなる電子供給層16と、電子供給層16上に設けられ、窒化ガリウムからなるキャップ層18と、キャップ層18上に設けられたゲート電極24と、電子供給層16上にゲート電極24を挟んで設けられたソース電極20及びドレイン電極22と、キャップ層18上に設けられた表面保護膜30と、キャップ層18と表面保護膜30との間に介在し、少なくともゲート電極24とドレイン電極22との間の領域に設けられたAlxGa1−xN(0.5≦x≦1)からなるバリア層50と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とソース電極との間のゲート寄生容量成分Cgsを低減することができる半導体装置を提供する。

【解決手段】半導体基板11上に形成された動作層12と、この動作層12の表面上に、互いに離間して形成されたドレイン電極13およびソース電極14と、動作層12の表面上において、ドレイン電極13とソース電極14との間に形成されたゲート電極15と、動作層12の表面上において、ドレイン電極13とソース電極14との間に、ゲート電極15を覆うように形成された表面保護膜19と、表面保護膜19の表面上であって、少なくともゲート電極15のドレイン側端部上を含む位置に形成されたソースフィールドプレート電極20と、ソースフィールドプレート電極20に接続されるとともに、ソース電極14に電気的に接続され、これらの電極20、14のよりも狭い幅で表面保護膜19上に形成された複数の配線21を具備する。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法および電子装置

【課題】ゲートリーク電流の増加が抑制された信頼性の高い電界効果トランジスタを提供する。

【解決手段】 ゲート電極は、第1金属層16および第2金属層17を含み、

第2金属層17は、第1金属層16よりも導電率が高く、

第1金属層16の上方に、第2金属層17が積層され、

ソース電極18およびドレイン電極19は、半導体層12〜14上にオーム性接触し、

ゲート電極は、ソース電極18およびドレイン電極19の間に配置され、かつ、第1金属層16により半導体層上にショットキー性接触し、

半導体層上におけるソース電極18およびゲート電極の間、ならびに、ゲート電極およびドレイン電極19の間は、絶縁膜15Aにより覆われ、

かつ、

第2金属層17下面の全体が第1金属層16上面の上方に重なっているか、または、第1金属層16の厚みが絶縁膜15Aの厚み以上であることを特徴とする電界効果トランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。または、良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面に第1の絶縁膜を形成し、第1の絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて第1の絶縁膜にエッチング処理を行うことにより、第2の絶縁膜を形成し、第2の絶縁膜を覆うように第1の導電膜を形成し、第1の導電膜および第2の絶縁膜に研磨処理を行うことにより、等しい厚さの第3の絶縁膜、ソース電極およびドレイン電極を形成し、第3の絶縁膜、ソース電極およびドレイン電極上に酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上の第3の絶縁膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体デバイスとその製造方法

【課題】裏面電極/半導体基板の間のエネルギー障壁が低く、半導体デバイスのオン抵抗が低減され、裏面電極の露出面の耐腐食性が良好で、かつ、裏面電極と半導体基板との密着性が良好で、裏面電極の材料コストを抑えることが可能な半導体デバイスを提供する。

【解決手段】裏面電極300は、Si基板101側から順にTiシリサイド層301とTi層302とNi層303とAg層304とAu層305とが積層された積層構造、又はSi基板101側から順にTiシリサイド層301とNi層303とAg層304とAu層305とが積層された積層構造を有する。裏面電極300は、Si基板101にTi層302とNi層303とAg層304とを順次成膜した後にシンター処理を行ってTiシリサイド層301を生成し、その後Au層305を成膜して製造されたものであることが好ましい。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】耐圧向上や短チャンネル効果の抑制を可能とする半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、半導体基板であるSiC基板1上に形成された、バッファ層2と、バッファ層2上に形成された、バッファ層2よりもバンドギャップが小さいチャネル層3と、チャネル層3上に形成された、チャネル層3よりもバンドギャップが大きいバリア層4と、バリア層4上に互いに離間して形成された、ソース、ドレイン電極7、8と、ソース、ドレイン電極7、8下から、バリア層4を通ってチャネル層3中にそれぞれ達する、不純物領域5とを備え、不純物領域5の下端は、バッファ層2に達しない。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置

を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構

造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を

提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加

熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理

回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジス

タを配置する。

(もっと読む)

有機薄膜トランジスタ絶縁層用樹脂組成物、オーバーコート絶縁層及び有機薄膜トランジスタ

【課題】閾値電圧の絶対値及びヒステリシスが小さい有機薄膜トランジスタを製造しうる有機薄膜トランジスタ絶縁層用樹脂組成物を提供すること。

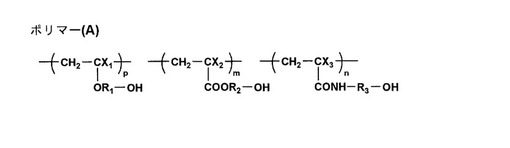

【解決手段】本発明の有機薄膜トランジスタゲート絶縁層用樹脂組成物は、フッ素原子を含む基を有する繰り返し単位を有する高分子化合物(A)、及びフッ素樹脂である活性水素化合物(B)を含有する。

(もっと読む)

有機電子デバイス用電極

【課題】透明性、導電性且つ生産後のロール状態での保存性が良好な有機電子デバイス用電極の提供。

【解決手段】透明基材上に、導電性の金属細線パターンと、導電性ポリマー層を設けた有機電子デバイス用電極において、該金属細線パターンの金属細線の厚みをaとし、開口部における該導電性ポリマー層の厚みをbとしたとき、以下式1〜式3で表される条件を満たし、且つ、導電性ポリマー層がπ共役系導電性高分子とポリアニオンとを含んでなる導電性ポリマーおよび下記ポリマー(A)を有する有機電子デバイス用電極。0.2≦a≦2.0(式1)0.2≦b≦2.0(式2)−0.2≦b−a≦1.8(式3) (もっと読む)

(もっと読む)

基板の製造方法、半導体装置の製造方法、電気光学装置

【課題】任意の方向に傾斜した開口部を形成可能な基板の製造方法、半導体装置の製造方法、およびこれを適用した半導体装置を備えた電気光学装置を提供すること。

【解決手段】本適用例の素子基板101の製造方法は、素子基板101上に設けられた半導体装置としてのTFT110を覆うと共に第1開口部としての孔104aが設けられた第2絶縁膜としての層間絶縁膜104をマスクとして、素子基板101の面法線101aと交差する一の方向からドライエッチングを第1絶縁膜としてのゲート絶縁膜103に施して、孔104aに連通すると共にTFT110のドレイン電極110dに開口する第2開口部としての孔103aを形成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製造方法

【課題】ヘテロ接合バイポーラトランジスタのエミッタメサがより正確に形成できるようにする。

【解決手段】第1エミッタ電極107bの側部には、例えば酸化シリコンからなる庇部108が形成され、また、少なくともキャップ層106を含んで構成されたエミッタメサの露出している側面から庇部108の下部の領域のレッジ構造部105aにかけて形成された、例えば窒化シリコンからなる被覆層109が形成されている。被覆層109が、庇部108の側面,庇部108の下面,エミッタメサの側部,およびレッジ構造部105aの上にかけて形成されている。

(もっと読む)

半導体装置

【課題】IGBTにおいて、P型コレクタ層におけるキャリア濃度の変化を抑制し、オン電圧のばらつきを低減可能な技術を提供することを目的とする。

【解決手段】半導体装置は、表面側にMOSFET構造1が形成されたN型半導体基板2と、N型半導体基板2の裏面に形成されたP型コレクタ層4とを備える。そして、P型コレクタ層4上にストライプ状に互いに離間して形成された、AlとSiとのAl合金からなるAlSi電極7aを含む積層構造の裏面電極7を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体基板上の金属電極と半導体基板の界面に、現像残渣のない半導体装置を提供すること。

【解決手段】半導体基板上に、金属電極が設けられた半導体装置であって、金属電極は、半導体基板の上面視において、細線部と、細線部の電極の長手方向の両端に太線部と、細線部から太線部へ向けて線幅が漸増する線幅漸増部とからなり、細線部の側面と線幅漸増部の側面の境界領域に、曲率を有す円弧が付けられた形状であることを特徴とする半導体装置。

(もっと読む)

パターン形成体の製造方法、機能性素子の製造方法および半導体素子の製造方法

【課題】本発明は、高精細なパターニングが可能なパターン形成体の効率的な製造方法を提供することを主目的とする。

【解決手段】本発明は、基板上に形成され、表面が疎水性を示す疎水性層上にフォトレジストパターンを形成するフォトレジストパターン形成工程と、上記フォトレジストパターンが形成された上記疎水性層の表面にエネルギーを照射して親水化し、親水性領域を形成する親水化工程と、上記フォトレジストパターンを剥離し、上記疎水性層表面に、上記親水性領域と上記親水化工程にて上記フォトレジストパターンで覆われていた疎水性領域とがパターン状に形成された親疎水パターンを形成するフォトレジストパターン剥離工程とを有することを特徴とするパターン形成体の製造方法を提供することにより、上記目的を達成する。

(もっと読む)

141 - 160 / 925

[ Back to top ]