Fターム[4M104DD34]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | 蒸着 (925)

Fターム[4M104DD34]に分類される特許

201 - 220 / 925

電界効果トランジスタ

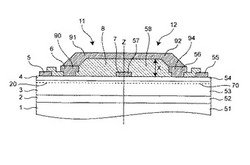

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたpチャネル型トランジスタを提供することを目的の一とする。また、酸化物半導体を用いたnチャネル型トランジスタとpチャネル型トランジスタとのCMOS(相補型金属酸化物半導体)構造を提供することを目的の一とする。

【解決手段】ゲート電極層と、ゲート絶縁層と、酸化物半導体層と、前記酸化物半導体層と接するソース電極層及びドレイン電極層とを含み、前記酸化物半導体層に用いる酸化物半導体の電子親和力をχ(eV)、バンドギャップをEg(eV)とすると、前記ソース電極層及び前記ドレイン電極層に用いる導電体の仕事関数φmは、φm>χ+Eg/2を満たし、かつ、χ+Eg−φmで表される正孔に対する障壁φBPは0.25eV未満である、酸化物半導体を用いたpチャネル型トランジスタを提供する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

半導体装置およびその製造方法

【課題】オン電圧の低電圧化と高速動作を両立させた半導体装置を提供する。

【解決手段】ゲート絶縁膜3は、ソース領域5の端縁部からウエル領域4の外縁にかけての部分の上部に相当する領域が、厚さ約50nmの薄膜部3aとなっており、エピタキシャル層1の上部に相当する領域が、厚さ80〜100nmの厚膜部3bとなっている。薄膜部3aと厚膜部3bとの間は曲率を有して緩やかに変化し、この薄膜部3aから厚膜部3bへと変化する領域を膜厚変化領域15と呼称する。膜厚変化領域15は、エピタキシャル層1のウエル領域4の側面に接する部分および、当該部分近傍のウエル領域4の上部に相当する領域であり、そこでの、ゲート絶縁膜3の厚さは薄膜部3aよりも厚くなっている。

(もっと読む)

薄膜トランジスタ

【課題】電気特性が良好な、酸化物半導体を用いた薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、基板上に設けられたゲート電極と、ゲート電極上に設けられたゲート絶縁膜と、ゲート電極およびゲート絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられた金属酸化物膜と、金属酸化物膜上に設けられた金属膜と、を有し、酸化物半導体膜は、金属酸化物膜と接し、且つ、酸化物半導体膜の他の領域よりも金属濃度が高い領域(金属高濃度領域)を有する。金属高濃度領域には、酸化物半導体膜に含まれる金属が、結晶粒または微結晶として存在していてもよい。

(もっと読む)

DLTS測定用電極及びその製造方法

【課題】測定時において疑似ピークが現れないDLTS測定用電極を提供する。

【解決手段】シリコン基板上に設けられたアンチモンからなるショットキー電極12aと、シリコン基板10の表面10aとショットキー電極12aとの間に設けられたチタンからなる密着膜12bとを備える。本発明によれば、ショットキー電極の材料としてアンチモンを用いていることから、DLTS測定において疑似ピークがほとんど現れず、しかも、測定時におけるリーク電流を抑制することが可能となる。このため、シリコンウェーハに含まれている重金属の種類や濃度を正確且つ高感度に評価することが可能となる。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間に金属酸化物層でなるバッファ層が設けられ

た逆スタガ型(ボトムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース

電極層及びドレイン電極層と半導体層との間に、バッファ層として金属酸化物層を意図的

に設けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体発光素子およびその製造方法

【課題】 光取出し側の電極部である上側電極部と、この電極部と対になる電極部である中間電極部とを適切な位置関係で配設することにより、大電流印加時の発光効率を維持させた半導体発光素子およびその製造方法を提供する。

【解決手段】 支持基板の上面側に、中間電極部を含む中間層、第2導電型半導体層、活性層、第1導電型半導体層および上側電極部を順次具え、支持基板の下面側に下側電極層を具える半導体発光素子であって、前記中間電極部を互いの中間電極部間の間隔が50μm以上100μm以下の均等に分散した島状または等間隔の縞状、格子状かつ上面から見た中間電極部の第2導電型半導体層に対する面積率が3〜9%となるように配置することにより、大電流での使用時でも発光効率の高い半導体発光素子を提供することができる。

(もっと読む)

電界効果トランジスタ

【課題】蛇行した形状に形成されたリセス部を備えることにより、オン抵抗を低減することができる電界効果トランジスタを提供することを目的とする。

【解決手段】電界効果トランジスタ1は、チャネル層11と、チャネル層11とヘテロ接合を構成するキャリア供給層12と、キャリア供給層12の表面から掘り下げて形成されたリセス部13と、リセス部13に沿って形成された第1絶縁層31と、第1絶縁層31の上に形成された第1ゲート電極23と、リセス部13に対してチャネル長方向の一方側に形成されたソース電極21と、リセス部13に対してチャネル長方向の他方側に形成されたドレイン電極22とを備える。リセス部13は、ソース電極21とドレイン電極22とが平面視で平行に対向するチャネル長の範囲内において、蛇行しながらチャネル長方向と交差する方向に延長されている。

(もっと読む)

半導体装置及びその作製方法

【課題】安定した電気特性を持つ、酸化物半導体を用いた薄膜トランジスタを有する、信頼性の高い半導体装置の作製方法の提供を目的の一とする。

【解決手段】ゲート絶縁膜を間に挟んでゲート電極と重なっている酸化物半導体膜と、酸化物半導体膜に接するソース電極またはドレイン電極とを有しており、ソース電極またはドレイン電極は、チタン、マグネシウム、イットリウム、アルミニウム、タングステン、モリブデンなどの電気陰性度が低い金属のいずれか一つまたは複数を含む混合物、金属化合物または合金を含んでおり、ソース電極またはドレイン電極中の水素濃度は酸化物半導体膜中の水素濃度の1.2倍以上、好ましくは5倍以上である。

(もっと読む)

窒化物系ダイオード

【課題】高耐圧でかつ低オン電圧動作が可能な窒化物系ダイオードを提供する。

【解決手段】窒化物系ダイオード10は、シリコン基板11の(111)面上に形成されたバッファ層12と、アンドープのGaNからなるチャネル層13と、チャネル13層上に形成されたアンドープのAlGaNからなる電子供給層14と、電子供給層14上に形成されたカソード電極15およびアノード電極16とを備える。窒化物系ダイオード10はさらに、電子供給層14を、チャネル層13に達する深さまで部分的に除去したメサ18を備え、メサ18の一方の側面部18aにアノード電極16が接触している。アノード電極16がメサ18の側面部18aに接触することで、アノード電極16と2次元電子ガス層17とが電気的に接続されている。

(もっと読む)

半導体装置の製造方法

【課題】炭化ケイ素を材料とする半導体ウェハから半導体装置を製造する方法において、表面電極と半導体基板とのショットキー接合、裏面電極と半導体基板とのオーミック接合を確保することと、製造工程を簡略化する。

【解決手段】半導体ウェハの表面に表面Mo電極を形成した後で、半導体ウェハの裏面に裏面Ni系電極を形成し、形成した表面Mo電極および裏面Ni系電極を同時にシンター処理する。表面Mo電極は、900℃以上のシンター処理を行っても、半導体基板とのショットキー接合を確保できる。裏面Ni系電極が半導体基板とオーミック接合するために必要な高温(例えば900℃以上)で、表面電極と裏面電極のシンター処理を同時に行うことができるため、製造工程が簡略化される。

(もっと読む)

半導体装置、電子装置、半導体装置の製造方法および使用方法

【課題】 スイッチング速度の低下やオン抵抗の増大を抑制しつつ、オフ耐圧を改善可能な半導体装置を提供する。

【解決手段】

半導体層11および12は、基板10上に形成され、第1の電極101、第2の電極102および絶縁膜14は、それぞれ、半導体層11および12上に形成され、絶縁膜14は、第1の電極101と第2の電極102との間に配置され、フィールドプレート電極17Aおよび17Bは、複数であり、かつ、絶縁膜14上に点在し、第1の電極101および第2の電極102は、半導体層11および12を介して電気的に接続されており、前記第1の電極と前記第2の電極との間の電圧印加時における電流の方向と垂直方向の各フィールドプレート電極の長さ、および、前記電流の方向と垂直方向に隣接する各フィールドプレート電極間の距離が、それぞれ、第1の電極101と第2の電極102との間の距離以下であることを特徴とする半導体装置。

(もっと読む)

SiC半導体装置とその製造方法

【課題】 炭化珪素を材料とする半導体基板の終端領域に、内側から外側に向かって滑らかな空乏層を形成することができるSiC半導体装置を提供する。

【解決手段】 半導体装置10は、炭化珪素を材料とする半導体基板25を有している。半導体基板25は、素子領域12と、その素子領域の周囲を取囲む終端領域14を有している。終端領域14には、素子領域12の外側を一巡する複数の溝17,19,21,23が形成される。それら複数の溝の底面は、内周側の溝から外周側の溝に向かって、順に浅くなるように形成されている。それら複数の溝の下方のそれぞれには、その周囲がドリフト層26によって取囲まれているp型領域16,18,20,22が形成される。

(もっと読む)

半導体装置

【課題】GaN電子走行層、AlGaN電子供給層、およびGaNキャップ層が順次積層された半導体装置において、高周波数動作および高出力動作を実現することが可能な半導体装置を提供すること。

【解決手段】本発明は、基板10上に順次積層されたGaN電子走行層12、AlGaN電子供給層14、およびGaNキャップ層16と、GaNキャップ層16上に形成されたゲート電極18と、ゲート電極18の両側であって、AlGaN電子供給層14上に形成されたソース電極20およびドレイン電極22と、ゲート電極18とソース電極20との間のGaNキャップ層16に形成された第1の凹部30と、を具備し、第1の凹部30が有する底面32下におけるGaNキャップ層16の厚さは、ゲート電極18下におけるGaNキャップ層16の厚さに比べて薄い半導体装置である。

(もっと読む)

半導体装置とその製造方法

【課題】製造コストを低く、炭化珪素基板の裏層部に、電極形成用の複数の溝を形成する半導体素子の製造技術を提供する。

【解決手段】炭化珪素基板13の裏層部の転移の存在する箇所に対応して、複数のエッチピット24をウエットエッチングにより形成する。炭化珪素基板とオーミック接触するカソード電極32をスパッタ法により形成する。炭化珪素基板13の表層部にp層16を形成し、アノード電極34をスパッタ法により形成し、ジャンクション・バリア・ショットキーダイオードとする。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性が良好で信頼性の高いトランジスタをスイッチング素子として用い、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】加熱処理により脱水化または脱水素化され、表面にナノ結晶からなる微結晶群が形成された酸化物半導体層を形成し、酸化物半導体層上に非晶質で透光性のある酸化物導電層を用いてソース電極層及びドレイン電極層を形成し、酸化物半導体層上の酸化物導電層を選択的にエッチングすることで透光性のあるボトムゲート型のトランジスタを形成し、同一基板上に駆動回路部と画素部を設けた信頼性及び表示品質の高い半導体装置を作製する。

(もっと読む)

半導体装置

【課題】半導体層と電極の接続部に生じる寄生抵抗を抑制し、配線抵抗による電圧降下の影響や画素への信号書き込み不良や階調不良などを防止し、より表示品質の良い表示装置を代表とする半導体装置を提供することを課題の一つとする

【解決手段】上記課題を解決するために、本発明は酸素親和性の強い金属を含むソース電極、及びドレイン電極と、不純物濃度を抑制した酸化物半導体層とを接続した薄膜トランジスタと、低抵抗な配線を接続して半導体装置を構成すればよい。また、酸化物半導体を用いた薄膜トランジスタを絶縁膜で囲んで封止すればよい。

(もっと読む)

201 - 220 / 925

[ Back to top ]