Fターム[4M104DD34]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | 蒸着 (925)

Fターム[4M104DD34]に分類される特許

121 - 140 / 925

電界効果トランジスタ及びその製造方法

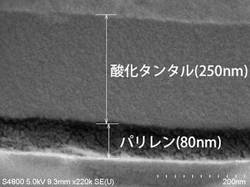

【課題】 複合酸化物の単結晶をチャンネルに用いたFETに電界効果のみで1013cm-2以上の高濃度のキャリアを注入することと、キャリアの移動度が室温でも10cm2/Vsに達するほどに理想的なチャンネルとの界面を得ることを共に可能にするゲート絶縁膜を有する電界効果トランジスタ及びその製造方法を提供することを目的とする。

【解決手段】 チャンネル層を構成するペロブスカイト構造の複合酸化物単結晶基板と、該複合酸化物単結晶基板上にパラキシリレンのポリマー膜及び酸化タンタルがこの順に積層された積層構造からなるゲート絶縁膜とを有する電界効果トランジスタ。

(もっと読む)

半導体発光素子及びその製造方法

【課題】高輝度化の半導体発光素子及びその製造方法を提供する。

【解決手段】半導体発光素子は、第1導電形の第1半導体層と、第2導電形の第2半導体層と、前記第1半導体層と前記第2半導体層との間に設けられた発光層と、第1電極層と、第2電極層と、を備える。第1電極層は、第2半導体層の第1半導体層とは反対側に設けられ、第2半導体層と接する金属部と、第1半導体層から第2半導体層に向かう方向に沿って金属部を貫通し前記方向に沿って見たときの形状の円相当直径が10ナノメートル以上5マイクロメートル以下である複数の開口部と、を有する。第2電極層は、第1半導体層と導通する。第2半導体層は、金属部に接する凸部と、開口部の底部において凸部よりも前記方向に沿って後退した凹部と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】GaAsデバイスにおいて、空洞上に浮遊するGaAs層に素子形成を行うことにより、浮遊容量を抑え、高速化・低電力化を図ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板11上に形成される空洞14と、空洞14上に形成されるGaAsエピタキシャル層13と、GaAsエピタキシャル層13上に形成されるゲート電極15と、それぞれGaAsエピタキシャル層13上に形成され、隣接するゲート電極15を挟むように形成される一対のソース電極16及びドレイン電極17と、を備える。

(もっと読む)

半導体発光素子及びその製造方法

【課題】窒化ガリウム系半導体層の半極性主面とパラジウム電極との接触抵抗が増加することを抑制可能な半導体発光素子を提供する。

【解決手段】半導体レーザ1は、半導体基板10上に設けられた活性層14と、活性層14上に設けられると共に半極性の表面18sを有するp型半導体層18と、表面18sに接合すると共にガリウムを含有するパラジウム電極38と、を備え、パラジウム電極38におけるガリウムの含有量が1mol%以上である。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上に第1のマスクを形成し、第1のマスクにスリミング処理を行うことにより、第2のマスクを形成し、第2のマスクを用いて絶縁膜にエッチング処理を行うことにより、絶縁層を形成し、絶縁層を覆うように酸化物半導体層を形成し、酸化物半導体層を覆うように導電膜を形成し、導電膜に研磨処理を行うことにより導電膜表面を平坦化し、導電膜をエッチング処理して導電層とすることにより酸化物半導体層の最上部の表面よりも導電層の表面を低くし、導電層と酸化物半導体層に接するゲート絶縁膜を形成し、ゲート絶縁膜の上で絶縁層と重畳する領域にゲート電極を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】容量増加による高周波特性の劣化及び裏面電極に起因する絶縁破壊を抑止し、チップ面積を増加させることなく、インパクトイオン化により生成したホールを容易且つ確実に引き抜いて排出することを可能として、高耐圧性及び高信頼性を実現する化合物半導体装置及びその製造方法を提供する。

【解決手段】絶縁性又は半絶縁性の基板1の表面に電子走行層3、電子供給層4が形成され、電子供給層4内には局所的なp型領域7が形成されており、基板1の裏面にp型領域7の一部を露出させる開口1aが形成され、開口1aを導電材料で埋め込みp型領域7とオーミック接続された裏面電極8を備え、AlGaN/GaN・HEMTが構成される。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

薄膜トランジスタ、薄膜トランジスタの製造方法、および電子機器

【課題】基板やゲート絶縁膜の露出表面と、ソース電極およびドレイン電極の露出表面とに、良好で均一な膜質の半導体薄膜を設けることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタ1aは、有機材料または酸化物材料またはシリコン系材料からなるゲート絶縁膜(絶縁層)15上に、導電性酸化物材料からなる酸化物材料層17-aとこの上部の金属材料層17-bとからなるソース電極およびドレイン電極が設けられたものである。そしてゲート絶縁膜(絶縁層)15とソース電極17sおよびドレイン電極17dとにおける酸化物材料層17-aとの露出面が、自己組織化膜19で覆われており、この自己組織化膜19で覆われた上部のソース電極17s−ドレイン電極17d間にわたって半導体薄膜21が設けられている。

(もっと読む)

成膜付半導体素子、及びその製造方法

【課題】半導体素子を破壊することを防止しつつ半導体素子の金属膜に対し安価に成膜できるとともに容易に厚膜化できる成膜付半導体素子の製造方法を提供すること。

【解決手段】シリコン層11に重ねてアルミ膜12を有する半導体素子10に対しコールドスプレー装置30によって成膜する成膜付半導体素子の製造方法は、第1工程と、第2工程とを有する。第1工程では、コールドスプレー装置30が、アルミ膜12の厚さV1より小さい粒径R1の第1銅粉末41を噴射することにより、アルミ膜12の表面に下地層21を形成する。第2工程では、コールドスプレー装置30が、第1銅粉末の粒径R1より大きく且つ下地層21の表面からアルミ膜12とシリコン層11との境界面までの寸法V2より小さい粒径R2の第2銅粉末42を噴射することにより下地層21に重ねて厚膜層22を形成する。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成する半導体装置の作製方法を提供することを目的の一とする。

【解決手段】絶縁表面上に、酸化物半導体層と、酸化物半導体層と接するソース電極およびドレイン電極と、を形成し、ソース電極上およびドレイン電極上にそれぞれ絶縁層を形成し、酸化物半導体層、ソース電極、ドレイン電極および絶縁層上にゲート絶縁層を形成し、ゲート絶縁層上に導電層を形成し、導電層を覆うように絶縁膜を形成し、導電層におけるソース電極またはドレイン電極と重畳する領域の少なくとも一部が露出するように絶縁膜を加工し、導電層の露出した領域をエッチングして、ソース電極とドレイン電極に挟まれた領域の少なくとも一部と重畳するゲート電極を自己整合的に形成する半導体装置の作製方法である。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

半導体装置の製造方法

【課題】信頼性を向上させることが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、窒化物半導体層11の表面に、パワー密度が0.2〜0.3W/cm2である酸素プラズマ処理を行う工程を有する半導体装置の製造方法である。本発明によれば、酸素プラズマ処理によって、窒化物半導体層11に導電層26が形成されることにより、イオンマイグレーション現象が抑制される。このため、半導体装置の信頼性が向上する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】電気特性が良好な半導体装置を、歩留まり高く作製する。

【解決手段】n型及びp型の少なくともいずれかの不純物が添加された不純物領域を有する半導体膜と、配線とを有し、配線は、導電性を有する金属酸化物を含む拡散防止膜と、該拡散防止膜上の低抵抗導電膜とを有し、配線と半導体膜とのコンタクト部において、拡散防止膜と不純物領域とが接する。拡散防止膜は、導電膜を酸化性ガス及びハロゲン系ガスの混合ガスから生成されるプラズマに暴露して該導電膜に含まれる金属材料の酸化物を形成し、金属材料の酸化物が形成された導電膜を、水を含む雰囲気に暴露して導電膜を流動化させ、流動化した導電膜を固化することで形成する。

(もっと読む)

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

トップゲート型薄膜トランジスタ及びこれを備えた表示装置

【課題】酸化物半導体層のチャネル領域の、水素拡散による低抵抗化を抑制するトップゲート型酸化物半導体TFT及びこれを備えた表示装置を提供する。

【解決手段】基板の上に、ソース電極層と、ドレイン電極層と、酸化物半導体層と、ゲート絶縁層と、In、Ga、Zn、Snの少なくとも1種類の元素を含むアモルファス酸化物半導体からなるゲート電極層と、水素を含む保護層と、を有し、ゲート絶縁層は酸化物半導体層のチャネル領域の上に形成され、ゲート電極層はゲート絶縁層の上に形成され、保護層はゲート電極層の上に形成されていることを特徴とするトップゲート型薄膜トランジスタ。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート−ソース間の容量低減及びソース抵抗を低減させ、且つ耐圧向上、高出力化及び高周波化を、容易且つ確実に可能とする量産化に優れた信頼性の高い化合物半導体装置を実現する。

【解決手段】ゲート電極19を形成する際に、4層の電子線レジスト11〜14を用いてゲート開口17を形成し、ゲート開口17内に、キャップ層5の表面との接触面を含む幹状の下方部分19aと下方部分19aから傘状に拡がる上方部分19bとが一体形成されてなり、下方部分19aの接触面がドレイン電極7に比べてソース電極6に偏倚した位置に設けられており、上方部分19bの傘状の下端面のうちソース電極6側の部位がドレイン電極7側の部位よりもキャップ層5の表面からの高さが高いゲート電極19を形成する。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】本発明は、ソース電極およびドレイン電極の熱耐久性を向上させて、かつ製造過程においてオーミック性に与える不安定要因を取り除き信頼性および量産性の高いGaN系HEMTを提供する。

【解決手段】GaN系HEMTは、基板と、窒化ガリウム系半導体と、融点が3000℃と高融点金属のタンタルと低融点金属のアルミニウムが前記窒化ガリウム系半導体上に積層されてなる前記ソースおよび前記ドレイン電極を備えている。前記ソース電極および前記ドレイン電極は、前記タンタルと前記アルミニウムの積層膜厚の比(前記アルミニウム膜厚/前記タンタル膜厚)を10以上にし、積層後のアニール処理温度が510℃以上、600℃未満で処理されて成る。

(もっと読む)

半導体装置の製造方法

【課題】コンタクト抵抗率を低く抑えることが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、Al組成比が0.2以上のAlGaN層をエッチングして、RMS粗さが0.3nm未満の底面を有する凹部を形成する工程と、前記凹部の底面に接して、4nmから8nmの厚さの第1Ta層を形成する工程と、前記第1Ta層に熱処理を施して、前記AlGaN層にオーミック接触させる工程と、を有する半導体装置の製造方法である。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】柱状結晶構造を有する金属を用いた場合でも、簡便な方法で、再現性良く階段構造状のテーパーを有する電極を形成する。

【解決手段】真空状態を保ったままの状態において、同一種類の金属を用いて、スパッタリング法で少なくとも2層の金属膜を成膜する成膜工程と、該成膜工程によって成膜された複数の金属膜にエッチング処理を施すことにより、階段構造状のテーパー形状を端部に有する、ゲート電極、ソース電極およびドレイン電極のうちの少なくとも1つを形成するエッチング工程とによって薄膜トランジスタを製造する。

(もっと読む)

ショットキーバリアダイオード及びその製造方法

【課題】バリア金属層のカバレッジを向上させることができ、さらに、トレンチ内に埋め込まれた導電体に応力が集中する虞がなく、逆方向電流(IR)を抑制することができるショットキーバリアダイオード(SBD)及びその製造方法を提供する。

【解決手段】本発明のSBD11は、シリコン基板2の表面2aにトレンチ3が形成され、トレンチ3の内面に最上面12aが傾斜面22とされた絶縁膜12が形成され、このトレンチ3内には、最上端部21aがトレンチ3の側壁上面3aより下方に位置するように導電体13が埋め込まれ、シリコン基板2の表面2a、絶縁膜12及び導電体13を覆うようにバリア金属層14及び電極金属層15が積層されている。

(もっと読む)

121 - 140 / 925

[ Back to top ]