Fターム[4M104DD34]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | 蒸着 (925)

Fターム[4M104DD34]に分類される特許

41 - 60 / 925

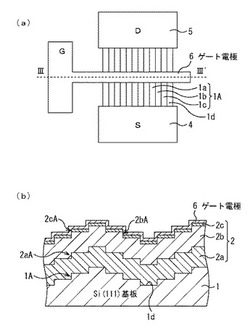

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

薄膜デバイス及びその製造方法

【課題】酸化物半導体膜を用いたTFTでは、ソース・ドレイン電極のプラズマエッチング後に酸化物半導体膜の表面領域に酸素欠損が生成されオフ電流が高くなってしまうという課題があった。

【解決手段】TFT101は、絶縁性基板10上のゲート電極11、ゲート電極11上のゲート絶縁膜12、ゲート絶縁膜12上のインジウムを含む酸化物半導体膜13、及び、酸化物半導体膜13上のソース・ドレイン電極14を有する。そして、酸化物半導体膜13のソース・ドレイン電極14が重ならない部分の表面層15におけるXPSスペクトルのインジウム3d軌道起因のピーク位置が、表面層15の下部に存在する酸化物半導体領域におけるXPSスペクトルのインジウム3d軌道起因のピーク位置よりも、高エネルギ側にシフトしている。

(もっと読む)

半導体装置、半導体装置の製造方法、および試験装置

【課題】ゲートリーク電流が少なく、かつ電流コラプスが抑えられた半導体装置の提供。

【解決手段】第1の態様においては、窒化物系半導体で形成された半導体層110と、半導体層上に開口を有して設けられ、タンタル酸窒化物を含む第1絶縁膜120と、第1絶縁膜の開口において半導体層上に積層された第2絶縁膜130と、第2絶縁膜上に設けられたゲート電極140と、を備える半導体装置を提供する。ここで、第2絶縁膜は、第1絶縁膜より絶縁性が高い絶縁膜により構成される。

(もっと読む)

電界効果トランジスタ

【課題】窒化物半導体を用いた電界効果トランジスタで、高いドレイン電流が実現できるようにする。

【解決手段】ドレイン電極107とゲート領域121との間のドレイン領域123の距離は、ソース電極106とゲート領域121との間のソース領域122の距離より長く形成され、加えて、ゲート電極104は、ゲート領域121からソース電極106の側に延在する延在部141を備えて形成されている。ゲート電極104のソース電極106の側への延在部141により、ゲート電極104に対する電圧印加でソース領域122のチャネル層101における電子濃度が増加可能とされている。

(もっと読む)

半導体装置の製造方法

【課題】オン抵抗の十分な低減を可能とする半導体装置の製造方法を提供する。

【解決手段】半導体装置1の製造方法は、少なくとも一方の主面を含む領域が単結晶炭化珪素からなる基板を準備する工程と、一方の主面上に活性層23を形成する工程と、基板の前記一方の主面とは反対側の他方の主面を含む領域を研削する工程と、他方の主面を含む領域を研削する工程において形成されたダメージ層22Cを除去する工程と、ダメージ層22Cが除去されることにより露出した主面に接触するように裏面電極を形成する工程とを備え、一方の主面は{0001}面に対するオフ角が50°以上65°以下となっている。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

選択成膜用マスク

【課題】ダイシングの負荷を増大させることなく、パターン部内に応力緩和用開口部を設けることができ、パターン精度を向上することが可能な選択成膜用マスクを提供する。

【解決手段】選択成膜用マスク2は、成膜基板上に取り付けられ、成膜基板上に所定のパターンで膜を成膜するためのものである。選択成膜用マスク2は、膜のパターンに対応した開口パターンと、少なくとも一方の面において開口し、成膜の際に選択成膜用マスク2にかかる応力を緩和するための応力緩和用開口部30とを備え、応力緩和用開口部30は、成膜基板上に選択成膜用マスク2を取り付けたときに、応力緩和用開口部30を通して成膜基板の表面が直接視認されない断面構造を有している。

(もっと読む)

蒸着用マスク、蒸着用マスクの製造方法、電子素子および電子素子の製造方法

【課題】被蒸着膜を高精細なパターンで形成することが可能な蒸着用マスクを提供する。

【解決手段】蒸着用マスクは、1または複数の第1開口部を有する基板と、この基板の第1主面側に設けられると共に、各第1開口部と対向して1または複数の第2開口部を有する高分子膜とを備える。蒸着の際には、蒸着材料が第1開口部および第2開口部を順に通過することにより、第2開口部に対応した所定のパターンで被蒸着膜が形成される。基板と高分子膜とを組み合わせて用いることにより、機械的強度を保持しつつも、金属膜のみで構成されている場合に比べ、第2開口部において微細かつ高精度な開口形状を実現できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体装置

【課題】高い開口率を有し、安定した電気特性を有する薄膜トランジスタを有する、信頼

性のよい表示装置を作製し、提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動

回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物

半導体によって構成された駆動回路用薄膜トランジスタと、金属によって構成された駆動

回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体に

よって構成され且つ半導体層が酸化物半導体によって構成された画素用薄膜トランジスタ

と、酸化物導電体によって構成された表示部用配線とを有する。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層に形成された第1チャネル型の第1MISFETの第1ソースおよび第1ドレインと、第2半導体結晶層に形成された第2チャネル型の第2MISFETの第2ソースおよび第2ドレインが、同一の導電性物質からなり、当該導電性物質の仕事関数ΦMが、数1および数2の少なくとも一方の関係を満たす。

(数1) φ1<ΦM<φ2+Eg2

(数2) |ΦM−φ1|≦0.1eV、かつ、|(φ2+Eg2)−ΦM|≦0.1eV

ただし、φ1は、N型半導体結晶層の電子親和力、φ2およびEg2は、P型半導体結晶層の電子親和力および禁制帯幅。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置においてオーミック特性を良好にし、かつ、酸・アルカリによる腐食に対し高い耐性を有することが可能な技術を提供することを目的とする。

【解決手段】半導体装置は、不純物が添加された高濃度不純物領域2を有する窒化物半導体層1と、高濃度不純物領域2上に順に積層された下地電極層3及び主電極層4を含む電極11とを備える。主電極層4は、窒化物半導体層1に対して下地電極層3よりも仕事関数が近い第1金属と、水素よりもイオン化傾向が小さい第2金属とからなる合金を主成分として含む。下地電極層3は、主電極層4よりも窒素との反応性が高い金属を主成分として含み、かつ、第1金属を含む。

(もっと読む)

Ga2O3系半導体素子

【課題】Ga2O3系化合物を半導体として用い、これに適合したショットキー特性が得られる電極を有するGa2O3系化合物半導体素子を提供する。

【解決手段】本発明のGa2O3系半導体素子は、n型導電性を有するβ−Ga2O3化合物半導体からなるn型層と、前記n型層上に形成されたショットキー特性を有する電極とを備え、前記電極は、Au、Pt、あるいはNi及びAuの積層体のいずれかによって構成される。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

半導体装置の製造方法

【課題】ワイドバンドギャップ半導体層とメタル電極のコンタクト抵抗を低減することができる半導体装置の製造方法を得る。

【解決手段】まず、シリコンに比べてバンドギャップが大きいIII−V族化合物半導体又はIV−IV族化合物半導体からなるp型窒化ガリウム層1の表面に、3−ヘリウム又は4−ヘリウムのイオンを照射してイオン照射領域2を形成する。イオン照射領域2を形成した後に、p型窒化ガリウム層1の表面にオーミックコンタクトしたメタル電極3を形成する。

(もっと読む)

窒化物半導体層のエッチング方法及びこれを用いた窒化物半導体装置の製造方法

【課題】高抵抗なダメージ層を形成しない窒化物半導体層のエッチング方法と、これを用いた低抵抗なオーミック電極を備える窒化物半導体装置の製造方法の提供を目的とする。

【解決手段】本発明の窒化物半導体層のエッチング方法は、(a)窒化物半導体層に不純物イオンを注入し、その表面から所定深さまで不純物領域を形成する工程と、(b)前記不純物領域を熱処理する工程と、(c)前記不純物領域の前記表面側の所定領域をウェットエッチングで除去する工程とを備える。

(もっと読む)

スパッタリング装置、スパッタリング装置を用いた成膜装置、およびそれらの成膜方法

【課題】基板サイズの大型化により、基板を水平搬送でき、基板を略垂直に立てて成膜でき、かつ膜厚均一性がよく、低コストのターゲットや電源を利用でき、蒸着装置とのクラスタ化に適したスパッタリング装置を提供する。

【解決手段】処理真空チャンバ(10)を有するスパッタリング装置であって、処理真空チャンバ内にカソード電極(60)が設けられ、カソード電極上にスパッタリングターゲット材料(61)が設けられ、処理真空チャンバ内に基板が上面搬送され、カソード電極は矩形であり、基板が垂直方向に立てられた状態でカソード電極が基板面と平行に走査されることで、スパッタリングターゲット材料が基板に成膜されるスパッタリング装置。

(もっと読む)

半導体素子

【課題】銅を回路層に用いても、信頼性の高い半導体装置を提供する。

【解決手段】半導体素子は、GaN系の半導体材料でできている本体21および少なくとも1つの電極構造物23を含む。電極構造物23は、本体21に形成されるオーミック接触層231、本体21の反対側のオーミック接触層231上に形成されるバッファ層232、および、銅系の材料でできており、オーミック接触層231の反対側のバッファ層232に形成される回路層233を含む。オーミック接触層231は、チタン、アルミニウム、ニッケルおよびそれらの合金から選択される材料でできている。バッファ層232は、オーミック接触層231の材料とは異なっており、かつ、チタン、タングステン、窒化チタン、タングステン窒化およびそれらの組み合わせから選択される材料でできている。

(もっと読む)

41 - 60 / 925

[ Back to top ]