Fターム[4M104DD34]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | 蒸着 (925)

Fターム[4M104DD34]に分類される特許

161 - 180 / 925

半導体装置及び半導体装置の製造方法

【課題】半導体基板上の金属電極と半導体基板の界面に、現像残渣のない半導体装置を提供すること。

【解決手段】半導体基板上に、金属電極が設けられた半導体装置であって、金属電極は、半導体基板の上面視において、細線部と、細線部の電極の長手方向の両端に太線部と、細線部から太線部へ向けて線幅が漸増する線幅漸増部とからなり、細線部の側面と線幅漸増部の側面の境界領域に、曲率を有す円弧が付けられた形状であることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】バイポーラトランジスタや縦型FET等の縦型デバイスを、絶縁膜マスクを用いた選択成長による、ボトムアップ構造にするすることで、精密な制御を要求される工程を削減できる製造方法を提供する。

【解決手段】導電性基板20の第1主表面上に、第1絶縁膜32、金属膜42及び第2絶縁膜52を順次に形成する。次に、第1絶縁膜、金属膜及び第2絶縁膜の、中央領域の部分を除去することにより、導電性基板を露出する成長用開口部70を形成する。次に、成長用開口部内に、半導体成長部82,84を形成する。次に、第2絶縁膜の、中央領域の周囲の周辺領域内に設けられた引出電極領域の部分72を除去することにより、金属膜を露出する引出電極用開口部を形成する。次に、引出電極用開口部内72に、引出電極90を形成する。次に、半導体成長部上及び導電性基板の第2主表面上にオーミック電極92を形成する。

(もっと読む)

貫通孔配線基板の製造方法

【課題】めっき反応速度を調整することでめっき未着を防ぐことが可能な貫通孔配線基板の製造方法を提供することである。

【解決手段】微小デバイスを構成する貫通孔配線基板の製造方法であって、基板40の両表面を貫通する貫通孔41を形成する工程と、貫通孔41の少なくとも内表面にNiめっきを成長させる工程と、を備え、貫通孔41の少なくとも内表面にNiめっきを成長させる工程では、Niめっきの析出レートを50nm/min未満にしてめっきを成長させる。

(もっと読む)

電界効果トランジスタ

【課題】スイッチング速度を向上でき、動作不良品を低減できる、横型の電界効果トランジスタを提供する。

【解決手段】ゲート配線43は、基部44と、基部44から突出する複数の指状部45と、隣接する指状部45の先端部46を接続する接続部47と、を有する。ゲート配線43の指状部45は、ソース配線23の指状部25とドレイン配線33の指状部35と、の間に配置されている。ゲート配線43の基部44は、ソース配線23の基部24とドレイン配線33の指状部35との間に配置され、かつ、ソース配線23の指状部25との間に絶縁膜を介在させて指状部25と交差している。

(もっと読む)

ナノワイヤトランジスタ及びその製造方法

【課題】動作不良や動作速度の低下の発生を従来よりも抑制できるナノワイヤトランジスタ及びその製造方法を提案する。

【解決手段】窒素が導入されたニッケルからなるニッケル層28をナノワイヤ5の周辺に形成して熱処理することにより、ナノワイヤ5に形成されたソース15及びドレイン16をシリサイド化させつつ、窒素によりゲート電極被覆領域ER1までシリサイド化されることを抑制できることから、従来よりもゲート電極被覆領域ER1にチャネル17を確保でき、かくして動作不良や動作速度の低下の発生を従来よりも抑制できる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】本発明は、高い信頼性を有するオーミック電極を備えた化合物半導体装置及びその製造方法を提供することを目的とする。

【解決手段】実施形態によれば、窒化物半導体層と、この窒化物半導体層上に設けられたオーミック電極と、を備え、前記オーミック電極は、前記窒化物半導体層との間で金属窒化物を形成する金属を含む第1電極層と、前記第1電極層上に設けられた、アルミニウム(Al)を含む第2電極層と、前記第2電極層の外面を被覆し、かつタングステン(W)を含む第3電極層と、前記第3電極層の外面を被覆し、かつ金(Au)を含む第4電極層と、を有することを特徴とする化合物半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

薄膜電極、及びその製造方法

【課題】実効キャリアー濃度が増加し、物質間のエネルギーバンドギャップ調節によりショットキー障壁が減少し、高い透過率を有する、優れた電気的、光学的、熱的及び構造的特性を有する新概念のオーミック接触システムを提供する。

【解決手段】発光ダイオード又はレーザーダイオードにおいてオーミック接触を形成するための薄膜電極において、p型窒化ガリウム層上に積層され、Ni−X固溶体を含有する第1電極層と、前記第1電極層上に積層され、Au、Pt、Pd、Ni、Ru、Rh、Re、C、Cu、及びIrからなる群から選択される少なくとも1種以上の元素を含有する第2電極層と、を含むことを特徴とする、薄膜電極である。

(もっと読む)

半導体発光素子の製造方法

【課題】発光効率と信頼性の向上

【解決手段】第2半導体層108上の全面に、透明導電膜10を形成し、形成された透明導電膜の上に、フォトレジストを塗布し、第1半導体層104の電極形成部16の上部のフォトレジストが除去される際に、除去される部分の輪郭部において、残されたフォトレジストの厚さが除去される部分に向かって次第に薄くなるようにフォトレジストを除去する。残されたフォトレジストをマスクとして、透明導電膜をウエットエッチングして、第2半導体層の一部を露出させる。残されたフォトレジスト及び透明導電膜をマスクとして、ドライエッチングして、第1半導体層の電極形成部を露出させる。残されたフォトレジストをマスクとして、透明導電膜のドライエッチングで露出した部分をウエットエッチングし、残されたフォトレジストを除去する。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】電気特性が良好な薄膜トランジスタを、生産性高く作製する方法を提供する。

【解決手段】第1のゲート電極と、第1のゲート電極とチャネル領域を挟んで対向する第2のゲート電極とを有するデュアルゲート型の薄膜トランジスタのチャネル領域の形成方法において、結晶粒の間に非晶質半導体が充填される微結晶半導体膜を形成する第1の条件で第1の微結晶半導体膜を形成した後、結晶成長を促進させる第2の条件で、第1の微結晶半導体膜上に第2の微結晶半導体膜を形成する。

(もっと読む)

トランジスタ基板及びその製造方法

【課題】オフ領域におけるゲート電圧−ドレイン電流特性(Vg−Id特性)の劣化を抑制した薄膜トランジスタを備えたトランジスタ基板及びその製造方法を提供する。

【解決手段】薄膜トランジスタTFTに設けられるチャネル保護層15の下層に形成された半導体層14のうち、ソース、ドレイン電極17間に側壁部が露出する領域(及びその近傍領域)が、酸素プラズマ処理により酸化処理されている。これにより、当該領域に酸化膜20が形成され、非導体化又は高抵抗化する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】化合物半導体装置のソース電極、ドレイン電極及びゲート電極を形成するいずれの領域においても、残渣のない良好な半導体/金属界面が得られるようにする。

【解決手段】化合物半導体装置の製造方法を、基板1上に化合物半導体積層構造4を形成する工程と、化合物半導体積層構造上に金属膜5A〜5Cを形成する工程と、金属膜上にソース電極7及びドレイン電極8を形成する工程と、金属膜の一部を酸化又は窒化して、金属酸化物膜又は金属窒化物膜5CXを形成する工程と、金属酸化物膜又は金属窒化物膜上にゲート電極9を形成する工程とを含むものとする。

(もっと読む)

ヘテロ接合型電界効果トランジスタ

【課題】リーク電流が少なくて高耐圧のヘテロ接合型電界効果トランジスタを提供する。

【解決手段】ヘテロ接合型電界効果トランジスタは、絶縁性基板上に順次積層されたAlNバッファ層、AlGaN組成傾斜層、GaNチャネル層、およびAlGaN障壁層を含み、AlGaN組成傾斜層はその下面から上面に向かってAl濃度が低減されており、AlGaN障壁層はAlGaN組成傾斜層の上面におけるAl濃度よりも15%以上大きなAl濃度を有しており、AlGaN組成傾斜層中において自発分極およびピエゾ効果によって得られる擬似的なp型シートキャリア濃度が3x1012cm−2以上4x1012cm−2以下である。

(もっと読む)

MEMS及びMEMSの製造方法

【課題】回路構成の設計自由度の高いMEMS及びMEMSの製造方法を提供する。

【解決手段】基板10と、基板10の一方の面側に設けられる第1半導体部21と、基板10の一方の面側に設けられる振動子31と、を備えるMEMSにおいて、第1半導体部21の側面側に設けられ、かつ基板表面に対して略垂直な第1面21aと、振動子31の側面側に設けられ、かつ基板表面に平行な方向において第1面21aと対向する第2面31aが設けられると共に、第2面31a側の表層部分は第1面21a側をゲート電極として電圧が印加された際にチャネルとなることで、第1半導体部21における第1面21aを含む部分と振動子31における第2面31aを含む部分とで電界効果トランジスタが構成されることを特徴とする。

(もっと読む)

有機薄膜トランジスタの製造方法、有機薄膜トランジスタレイの製造方法及び表示装置の製造方法

【課題】有機薄膜トランジスタを高い歩留まりで製造する製造方法を提供する。

【解決手段】基板上又は基板上における絶縁膜上にソース電極及びドレイン電極を形成する電極形成工程と、有機半導体インクが供給された際、前記ソース電極及び前記ドレイン電極上における前記有機半導体インクの接触角を前記基板上又は前記絶縁膜上における接触角よりも高くする電極処理工程と、形成された前記ソース電極及び前記ドレイン電極の間に前記有機半導体インクを供給することにより有機半導体層を形成する半導体層形成工程と、を有し、前記ソース電極と前記ドレイン電極とにより形成されるチャネルのチャネル幅をW、前記有機半導体インクが供給される際の液滴の液滴径をφ、前記液滴が供給される位置の誤差である着弾位置誤差幅をXとした場合、W>φ+Xを満たしていることを特徴とする有機薄膜トランジスタの製造方法を提供することにより上記課題を解決する。

(もっと読む)

電子デバイス及びオーミック電極形成方法

【課題】製造工程において高温で短時間のアニールを可能にすることにより、イオン注入の工程が不要なAlxGa1−xN/AlyGa1−yNヘテロ接合のオーミック電極を備える電子デバイスを提供する。

【解決手段】

電子デバイスは、ワイドバンドギャップ化合物半導体層と、前記ワイドバンドギャップ化合物半導体層上に形成されるオーミック電極とを含む電子デバイスであって、前記ワイドバンドギャップ化合物半導体層は、IniAljGakN(i+j+k=1,0≦i≦1,0<j≦1,0≦k<1)からなる化合物半導体バリア層とAlyGa1−yN(0<y≦1)からなる化合物半導体チャネル層からなり、前記オーミック電極は、前記化合物半導体バリア層上に密着層が積層され、前記密着層上にオーミック層が積層されて形成された電極であり、前記密着層はZrからなるようにする。

(もっと読む)

電子素子基板及びその製造方法

【課題】酸化物の一部領域又は全領域の比抵抗を低下させることにより、簡易な工程で多様な電子素子を作製できる電子素子基板の製造方法を提供する。

【解決手段】少なくとも最表層の一部が比抵抗1×109Ω・cm以下の酸化物からなる基板における前記酸化物の一部領域又は全領域に対し、前記基板の電位よりも高い電位を印加することにより、前記一部領域又は前記全領域の比抵抗を低下させる低抵抗化処理工程を有する電子素子基板の製造方法である。

(もっと読む)

新規有機導電性膜を使用した有機電極

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

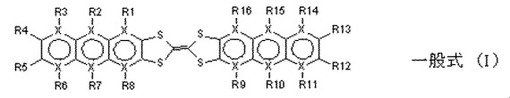

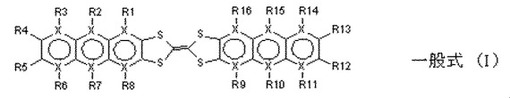

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

有機積層膜

【課題】複雑な工程を経ることなく、テトラチアフルバレン誘導体と電子受容性化合物とを積層させるだけで、簡便かつ高電気伝導度を有する積層膜を提供する。

【解決手段】一般式(I)で表されるテトラチアフルバレン誘導体と電子受容性化合物の積層膜

(式(I)中、Xは炭素原子または硫黄原子または窒素原子から選択される原子であり同一でも異なっていても良い。Xに炭素原子及び窒素原子が選択される場合においてR1〜R16は水素原子、ハロゲン原子、置換および無置換のアルキル基またはアルコシキ基またはチオアルコキシ基から選択される基であり同一でも異なっていても良い。)。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

161 - 180 / 925

[ Back to top ]